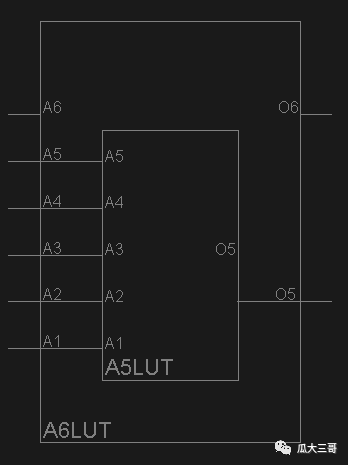

我们知道FPGA由LUT、IO接口、时钟管理单元、存储器、DSP等构成,我觉得最能代表FPGA特点的就是LUT了。当然不同厂家、同一厂家不同阶段FPGA的LUT输入数量是不同的,随着技术的发展,LUT的输入数量也在增加。

作为FPGA最基本的电路单元,承担着各种电路功能的实现,如果能够理解LUT对电路的实现及影响,对我们进行FPGA开发及优化有着至关重要的作用。如果电路的输入数量远大于LUT的输入数量,LUT在实现电路时必然采用级联方式,级联数量必定会造成电路的延时,有时候会严重制约系统的最高运行频率。

如果我们能够理解好这一点,那么我们在设计电路的时候就要尽量避免级联级数太多,对电路进行优化,比如插入寄存器等方式来减少电路的延时,保证系统的正常运行。

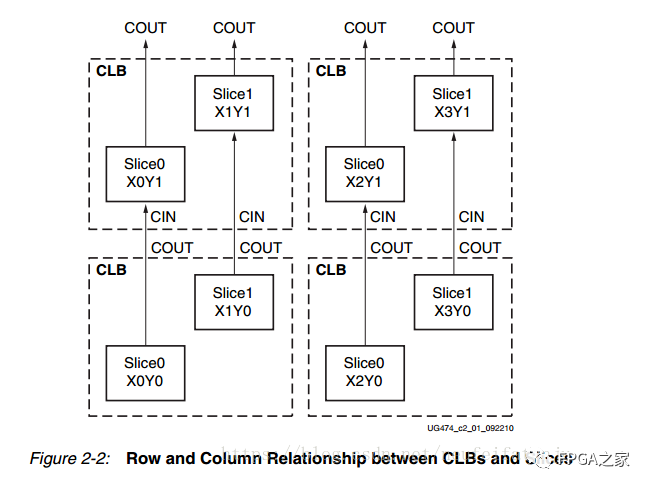

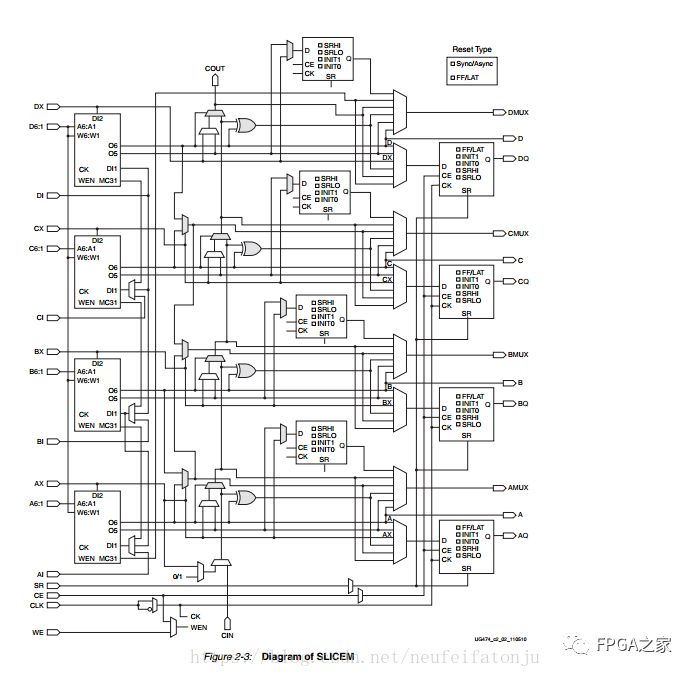

附XILINX 7Series基本逻辑单元框图

审核编辑:汤梓红

-

FPGA

+关注

关注

1634文章

21827浏览量

607858 -

存储器

+关注

关注

38文章

7551浏览量

164758 -

Xilinx

+关注

关注

71文章

2173浏览量

122676 -

时钟

+关注

关注

11文章

1755浏览量

132098 -

LUT

+关注

关注

0文章

50浏览量

12624

原文标题:关于FPGA四输入、六输入基本逻辑单元LUT的一点理解

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

请教ALTERA的FPGA什么时候开始使用6输入LUT?

FPGA基础知识0(查找表LUT和编程方式)

如何在LUT和逻辑元件之间以及逻辑元件和逻辑单元之间进行交换

Spartan 6 FPGA LUT中是否有pmos和nmos transisors?

解析数字电路的与、或、非等逻辑是通过 6 输入的查找表实现

关于FPGA四输入、六输入基本逻辑单元LUT的一点理解

关于FPGA四输入、六输入基本逻辑单元LUT的一点理解

评论