以下是用于集成 AXI VIP 以在简单定向环境中开始验证 AXI 接口的步骤。这种定向测试方法也实现了良好的性能。

下面的测试平台示例显示了一个连接到 DUT 从机的 AXI 主 VIP。实际示例还使用 VIP 代替从属 DUT 。

1) 导入并包含所需的 VIP 包/文件

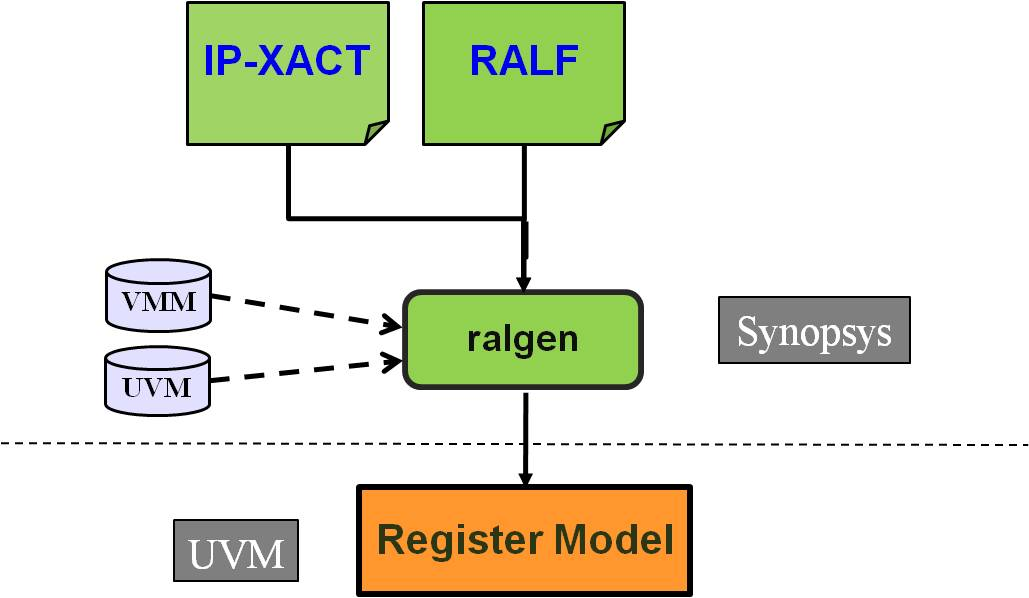

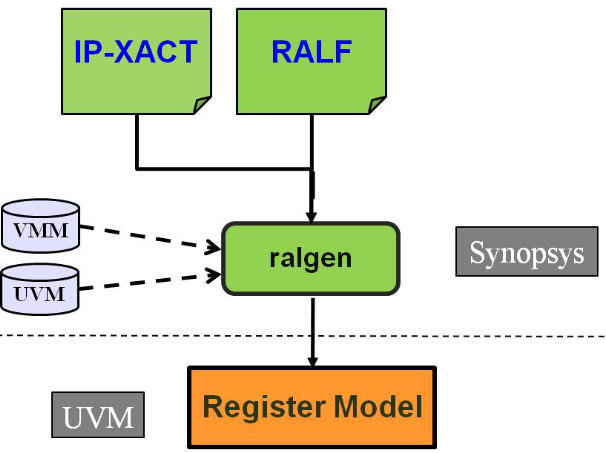

Synopsys 的 VIP 以 SystemVerilog 包的形式提供。这些包为 VIP 定义唯一的命名空间,但为了使 VIP 更易于使用,可以将 VIP 命名空间导入到全局命名空间中。除了SystemVerilog软件包之外,SVT VIP的某些方面(如SystemVerilog接口)作为全局文件交付,必须包含这些文件,因为它们必须同时存在于设计和测试平台域中。

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

|

`include "uvm_pkg.sv"`include "svt_axi_if.svi"/** Include the AXI SVT UVM package */`include "svt_axi.uvm.pkg"module test_top;/** Import UVM Package */import uvm_pkg::*;/** Import the SVT UVM Package */import svt_uvm_pkg::*;/** Import the AXI VIP */import svt_axi_uvm_pkg::*;……endmodule |

2) 将 VIP 接口连接到 DUT 信号

VIP提供SystemVerilog接口,提供所需的信号连接。必须声明这些接口的实例,并且来自这些接口的信号必须连接到 DUT。在这个例子中,主(vip)和从(vip)都是背靠背连接的。可以轻松地将所需的VIP模型替换为相应的DUT模型。

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

|

/** VIP Interface instance representing the AXI bus */svt_axi_if axi_if();assign axi_if.common_aclk = SystemClock;/** Testbench reset */logic tb_reset;/*** Assign the testbench reset to the reset pins of the VIP* interface.*/assign axi_if.master_if[0].aresetn = tb_reset;/* connection from master[0] to slave[0], connected back to back */assign axi_if.slave_if[0].awvalid = axi_if.master_if[0].awvalid;assign axi_if.slave_if[0].awaddr = axi_if.master_if[0].awaddr;…assign axi_if.master_if[0].arready = axi_if.slave_if[0].arready;assign axi_if.master_if[0].rvalid = axi_if.slave_if[0].rvalid;assign axi_if.master_if[0].rlast = axi_if.slave_if[0].rlast;……/** make rest of assignments (you can alternately choose the SystemVerilog bind approach/** for that you can refer to “amba_svt/tb_axi_svt_uvm_intermediate_sys”/** example from VIP installation |

3) 为异议管理和 UVM 低执行创建虚拟 UVM 测试

Directed_test是一个虚拟测试,可以扩展uvm_test。这允许 UVM 阶段机制执行,并使用事件 (end_test) 同步管理在程序块中编写的定向测试的运行阶段的异议。

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

|

class Directed_test extends uvm_test;/** UVM Component Utility macro */`uvm_component_utils(Directed_test)/** Class Constructor */function new(string name = "Directed_test", uvm_component parent=null);super.new(name,parent);endfunction: new//Objection management co-ordinated by uvm_testvirtual task run_phase(uvm_phase phase);super.run_phase(phase);phase.raise_objection(this);@end_test; //this event will be triggered by directed test from initial-begin-end blockphase.drop_objection(this);endtaskendclass |

4) 实例化 VIP 组件

必须构造和配置主 VIP 代理类和从属 VIP 代理类。初始化这些配置对象后,将使用 UVM 资源数据库将它们发送到 UVM 层次结构中的相应代理实例。

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

|

initial begin`uvm_info("Directed_test", "Entered...", UVM_MEDIUM)master_0 = svt_axi_master_agent::type_id::create("master_0",null);master_cfg0 = svt_axi_port_configuration::type_id::create("master_cfg0",null);/** set required interface for agent instances */master_cfg0.set_master_if(axi_if.master_if[0]);master_cfg0.data_width = 256;/**Pass master and slave configuration using resource database */uvm_config_db#(svt_axi_port_configuration)::set(null, "*master_0", "cfg", master_cfg0); |

5) 开始 UVM 执行

UVM run_test() 方法启动 UVM 执行,并且它的参数用作要执行的默认测试。

|

1

2

3

4

|

/** Start the UVM execution */forkrun_test("Directed_test");join_none |

6) 重置 DUT DUT

重置代码必须在执行任何事务之前调用/执行。

|

1

2

3

4

5

6

7

8

|

/* Reset logic */`uvm_info("reset_logic", "Entered...", UVM_LOW)tb_reset = 1'b1;repeat(10) @(posedge SystemClock);tb_reset = 1'b0;repeat(10) @(posedge SystemClock);tb_reset = 1'b1;`uvm_info("reset_logic", "Exiting...", UVM_LOW) |

7) 从主站发起流量

现在,我们已准备好开始从主节点创建事务。下面的示例创建一个 WRITE 事务,设置所有必填字段,并使用 execute_item() 方法将其发送到 VIP 主驱动程序。

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

|

/* Create and Send atomic transaction */`uvm_info("atomic_transation", "Entered...", UVM_MEDIUM)beginsvt_axi_master_transaction axi_trans;axi_trans = new();axi_trans.port_cfg = cfg.master_cfg[0];axi_trans.xact_type = svt_axi_transaction::WRITE;axi_trans.addr = 32'h0000_0000;axi_trans.burst_type = svt_axi_transaction::INCR;axi_trans.burst_size = svt_axi_transaction::BURST_SIZE_32BIT;axi_trans.atomic_type = svt_axi_transaction::NORMAL;axi_trans.burst_length = 16;axi_trans.data = new[axi_trans.burst_length];axi_trans.wstrb = new[axi_trans.burst_length];/** Send the atomic write transaction */master_0.sequencer.execute_item(axi_trans); //send axi transaction to driver`uvm_info("atomic_transation", "Ended...", UVM_MEDIUM)end |

8 ) 触发测试结束

end_test事件用于使 run_phase() 引发的异议能够删除。这表示运行阶段结束,其余的 UVM 阶段将在运行阶段完成后执行。这表示测试结束。

|

1

2

3

4

|

//Trigger uvm end of testend_test;`uvm_info("Directed_test", "Exited...", UVM_MEDIUM)end |

审核编辑:郭婷

-

接口

+关注

关注

33文章

8575浏览量

151014 -

Synopsys

+关注

关注

2文章

157浏览量

90160 -

DUT

+关注

关注

0文章

189浏览量

12373

发布评论请先 登录

相关推荐

AXI VIP设计示例 AXI接口传输分析

如何将AXI VIP添加到Vivado工程中

如何使用AXI VIP在AXI4(Full)主接口中执行验证和查找错误

如何下载Webpack版本并开始使用

XPS中用“axi-pcie 1.08a”和其他一些露水创建项目不起作用的原因?

如何使用Xilinx AXI VIP对自己的设计搭建仿真验证环境的方法

使用AXI VIP的几个关键步骤及常见功能

一些高质量的AMBA(APB/AHB/AXI) VIP分享

记录最近Debug AMBA VIP的两次经历

简化UVM寄存器模型的使用教程

AXI VIP当作master时如何使用?

开始使用AXI VIP,对UVM有一些基本的了解

开始使用AXI VIP,对UVM有一些基本的了解

评论