什么是RISC-V?

精简指令集计算机体系结构(RISC)是一种指令集体系结构(ISA),它意味着硬件和软件之间的基本桥梁。RISC通过定义一组简单的指令来实现汇编语言程序员和处理器之间的通信,这些指令组合在一起以执行各种复杂的指令。

RISC和复杂指令集计算机(CISC)方法都试图优化CPU的处理时间。在RISC中,每条指令所需的周期减少,而每个程序的指令增加。但在CISC中,每个程序的指令数减少,而每条指令的周期增加。

执行时间 = # 每个程序的指令数 X # 每条指令的周期数

因此,RISC更像是基于软件的ISA,因为软件必须负责发送必要的简单指令来执行应用程序。而CISC是基于硬件的ISA,因为CISC中的指令很复杂,因此需要复杂的指令解码。

RISC-V是基于既定RISC原则的开放标准指令集架构。与大多数其他ISA设计不同,RISC-V是在开源许可下提供的,允许在整个行业中广泛使用。

了解TileLink在RISC-V架构中的作用

RISC-V的开发人员开发了一种名为RocketChip的参数化SoC发生器,它使用TileLink规范作为其多处理器,加速器和DMA引擎等的互连。

TileLink 是一种开源芯片级互连标准,提供对内存和其他设备的一致内存映射访问。它也是一种快速且可扩展的互连,可提供低延迟和高吞吐量传输。

磁贴链接的主要优点:

TileLink 旨在支持缓存一致性共享内存

在多核(单个芯片上的多个处理器)环境中,缓存一致性是一个问题,其中每个处理器都有一个单独的缓存内存。在这种情况下,可以拥有共享数据的不同副本 - 即主存储器中有一个副本,每个缓存内存中有一个副本 - 并且当其中一个数据副本被更改时,其他副本将留下无效数据而没有更改通知。缓存一致性是用于确保通过系统更新共享数据值更改的概念。TileLink支持MESI等效协议来解决缓存一致性问题。

TileLink 为任何符合标准的 SoC 提供无死锁

TileLink 支持可定义为有向无环图 (DAG) 的任何拓扑,其中代理是顶点,链路是边,边从驱动程序接口定向到接收器接口。通过支持 DAG,TileLink 在其拓扑中没有任何循环或循环。

TileLink 配备了无序完成功能,以提高并发操作的吞吐量。

TileLink 提供无状态总线宽度自适应。

TileLink网络如何工作?

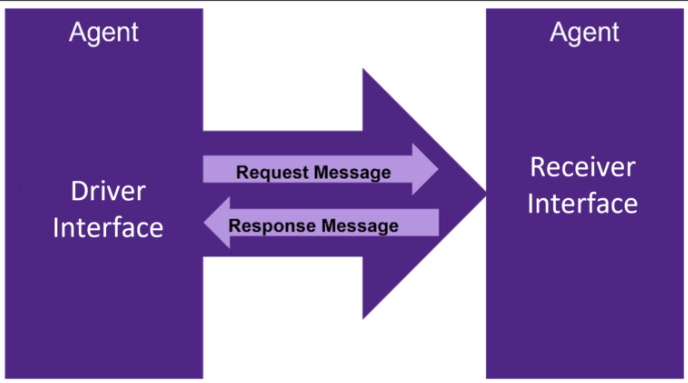

下图显示了基本 TileLink 网络的示例。包含驱动程序接口的代理通过链路连接到包含接收方接口的另一个代理。驱动程序代理向接收代理发送请求,接收代理将响应原始请求者,确认已收到发送的数据或权限。

在每个链路中,Tilelink 定义了五个在逻辑上彼此独立的通道,代理可以通过这些通道交换消息。TileLink规范按照“A << B << C << D << E”的顺序定义了通道消息之间的优先级,增加了优先级,必须确保TileLink网络中的消息永远不会进入路由或保持和等待循环,从而避免死锁。

TileLink 中的消息由节拍组成,每个节拍包含以下内容:

不变的邮件头

不变的操作码(消息类型)

不变大小(数据有效负载中字节数的以 2 为底的对数)

可选的多拍数据有效负载

节拍由特定通道的独立“就绪”和“有效”信号调节。发送方和接收方需要分别提供有效和就绪的信号才能实现位传输。一旦请求消息启动,其相应的响应消息可能会在以下任何时间发送:

在预定义的延迟之后

在接受请求的第一个节拍的同一周期内

在接受请求消息的所有节拍之前

TileLink禁止TileLink网络中的超时,保证TileLink网络永远不会死锁。TileLink 协议定义了称为转发处理规则的规则,这些规则控制接收代理可以通过更改就绪信号来拒绝消息节拍的条件。

Synopsys VIP for TileLink

Synopsys® 验证 IP for TileLink 提供了一套全面的协议、方法、验证和生产力功能,使用户能够实现加速验证收敛。

Synopsys TileLink VIP 的功能包括:

支持 TileLink 1.8.0 和 1.8.1 规范

驱动器、接收器和交叉杆代理

TL-UL、TL-UH 和 TL-C 一致性级别

所有渠道

所有请求和响应消息

全面的同通道和跨通道延迟

数据宽度:32、64、128、256、512、1024 位

所有突发大小高达 4KB

无序响应

用户定义的先进先出模式(按顺序)响应

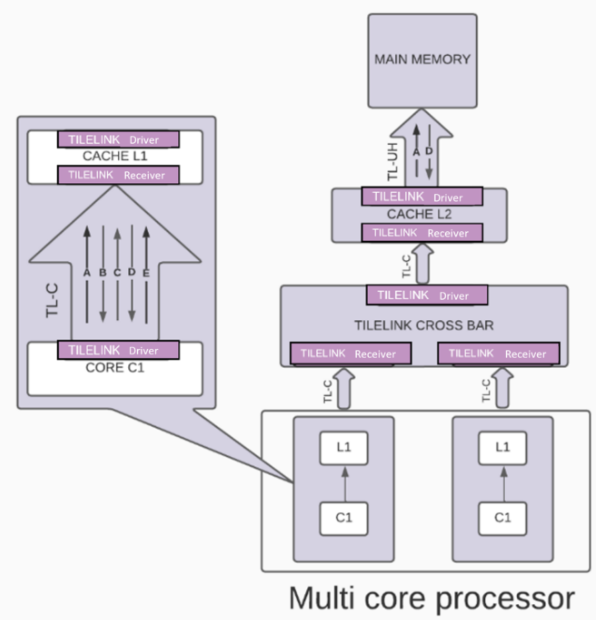

下图显示了可在多级高速缓存应用程序中使用 Synopsys 验证 IP for TileLink 的基本架构示例。通过TileLink驱动程序或接收器接口连接到TileLink互连的每个组件(内核,缓存L1,缓存L2,主存储器)都可以与其相应的驱动程序或接收器验证IP代理集成。

如图所示,当具有独立缓存的多个内核共享主内存或更高级别的缓存时,可以使用 TileLink 交叉条代理来维护它们之间的缓存一致性。

总结

尽管RISC-V不是第一次尝试免费和开源处理器IP,但它是第一个大规模地引起业界兴趣的尝试。这为TileLink规范提供了灵活性和开放的方法,产生了巨大的创新和增长潜力。

Synopsys VIP for TileLink 可以毫不费力地集成、配置和定制。

Synopsys VIP 与 Synopsys Verdi Protocol Analyzer 调试解决方案以及 Synopsys Verdi®® Performance Analyzer 原生集成。在 SoC 上运行系统级有效负载需要更快的基于硬件的预硅解决方案。基于 Synopsys IP 的 Synopsys 事务处理器、内存模型、混合和虚拟解决方案可在业界最快的验证硬件 Synopsys ZeBu® 和 Synopsys HAPS® 系统上实现各种验证和确认用例。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19122浏览量

228875 -

ISA

+关注

关注

0文章

55浏览量

43709 -

RISC

+关注

关注

6文章

461浏览量

83637

发布评论请先 登录

相关推荐

RISC-V最重要的意义所在

学习RISC-V入门 基于RISC-V架构的开源处理器及SoC研究

可扩展的高性能RISC-V 内核IP

RISC-V应用领域的拓展

Microchip FPGA 和基于 SoC 的 RISC-V 生态系统简介

RISC-V SoC 新开源平台发布 zqh_riscv

布局 RISC-V 领域,中国联通加入中国 RISC-V 产业联盟

RISC-V入云!赛昉科技联合中国电信完成首个RISC-V云原生轻量级虚拟机验证

RISC-V,正在摆脱低端

基于形式的高效 RISC-V 处理器验证方法

如何保证RISC-V验证设计完整性

晶心科技与Arteris合作加速RISC-V的SoC设计创新

Arteris与晶心科技携手推进RISC-V SoC设计创新

晶心科技与Arteris携手加速RISC-V SoC的采用

用于RISC-V SoC的TileLink互连验证IP

用于RISC-V SoC的TileLink互连验证IP

评论