2021 年,PCI-SIG® 发布了最新版本的 PCI Express® 规范 PCIe® 6.0。PCIe 6.0 的原始数据速率为 64 GT/s,带宽是 PCIe 5.0 (32GT/s) 的两倍,可满足行业对高速、低延迟互连的需求。它是一种可扩展的互连解决方案,适用于数据中心、AI/ML、高性能计算 (HPC) 和汽车等数据密集型市场。

在本博客中,我们将讨论 PCIe 6.0 中的前向纠错 (FEC) 机制、为什么需要它,以及 Synopsys 提供哪些验证解决方案来涵盖此功能。

什么是 PAM-4?

PCIe 6.0 使用数据速率为 4GT/s 的 PAM-64 信令,而不是以较低数据速率使用的不归零 (NRZ) 信令。这意味着发送和接收的信号现在将在一个单位间隔内具有四个不同的电压电平(2位)编码,从而产生三个眼睛。这是因为 64GT/s 的 NRZ 信令会导致 32GHz 的奈奎斯特速率增加,此时信道损耗可能很大;因此,PAM-4 以 64GT/s 的速度使用以减少信道损耗,因为它具有与 16GT/s 数据速率相同的奈奎斯特速率 (32GHz)。

然而,这需要权衡,因为眼睛高度和眼睛宽度会减小,这使得接收器容易出错。预计误差在车道中以突发形式发生,并且预计车道之间也会有一定程度的相关性。因此,与PAM-4信令相关的误码率(BER)预计将远高于较低数据速率的10^-12目标。

为什么需要 FEC 以及如何完成?

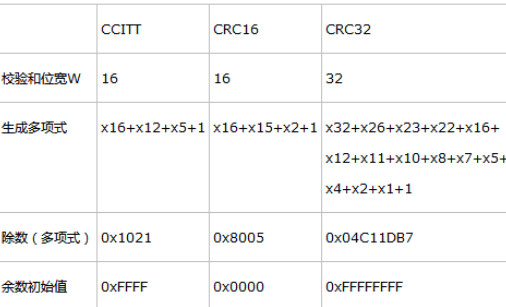

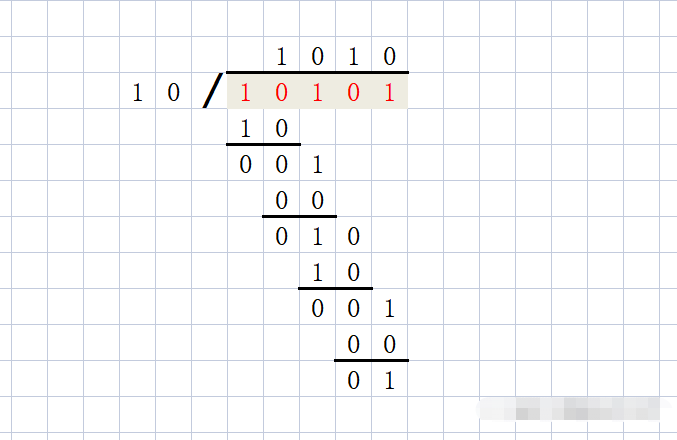

FEC 用于缓解数据流中的高 BER。由于 FEC 在固定代码大小上工作,因此 FLIT 用于传输数据流中的 TLP 和 DLP。FEC 的延迟和复杂性随着要更正的字节数呈指数级增长。为了保持较低的延迟(<2ns)和复杂性,使用了轻量级FEC,它可以纠正单字节错误。这与用于错误检测的强循环冗余校验 (CRC) 相结合,以产生高可靠性结果。此外,预编码可用于最大限度地减少突发中的错误。

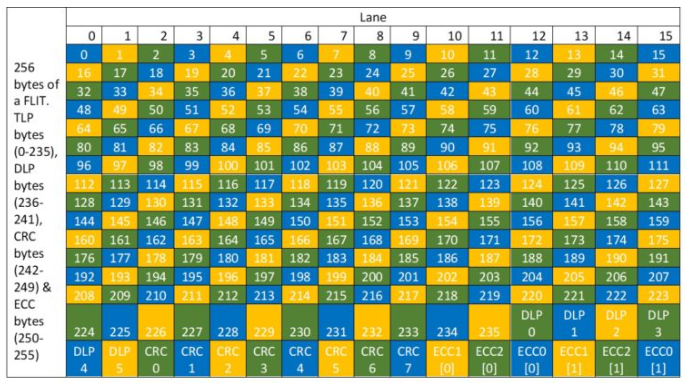

FLIT 的大小为 256 字节,其中 236 字节用于 TLP,6 字节用于 DLP,8 字节用于 CRC,6 字节用于错误检查和纠正 (ECC)。CRC 的 8 个字节保护 TLP 和 DLP 字节,但不保护 ECC 字节。6 字节的 ECC 保护整个 FLIT,包括 CRC 字节。

FEC 代码是 3 路交错的,如下表所示。每种颜色代表一个 ECC 组,其字节以相同的颜色标记。因此,一个通道中的三个连续字节属于三个不同的 ECC 组。因此,通道中长度为 <=16 的突发误差不会影响每组中的多个字节,并且每个 ECC 可以纠正单个字节错误。

表 1:x16 链路上的 FLIT 交错

在接收器上,ECC 解码器对其相应的代码组执行校正,并根据需要报告错误状态。然后进行CRC检查,以确定是否接受收到的FLIT。如果 CRC 检查失败,FLIT 将重放并得到纠正。

如果检测到无法纠正的错误,CRC 检查将失败并导致否定确认 (NAK),然后重播。优化是可能的,例如,可能无法重放具有仅 NOP TLP 的 FLIT,也可以仅重放错误 FLIT。

可纠正和不可纠正的错误:

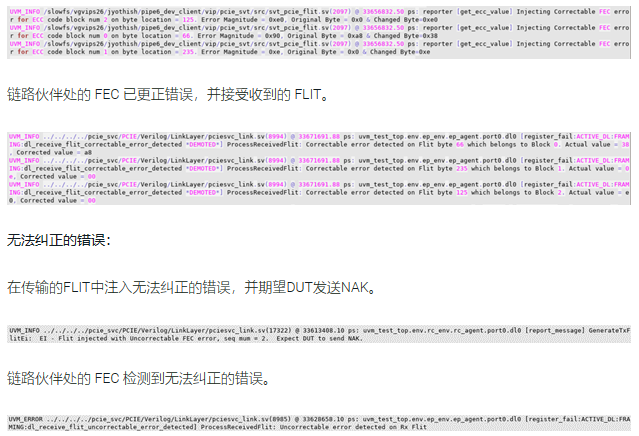

以下是 Synopsys 验证 IP for PCIe 6.0 成绩单的快照,说明了 FLIT 中可纠正和不可纠正的错误。

可纠正的错误:

在传输的FLIT中注入可纠正的错误。

验证可纠正和不可纠正的错误以确保 FEC、CRC 和重放机制正常工作非常重要。

最终,轻量级 FEC 与强大的 64 位 CRC 相结合,适用于 10^-6 的 FBER,即使具有高通道相关性。每个 FLIT 的重试概率约为 5×10^-6,时间失败 (FIT) 几乎为 0。

适用于 PCIe 6.0 的 Synopsys 验证 IP 旨在解决关闭 SoC 数据可靠性方面所需的所有验证复杂性。 数据可靠性是一个非常理想的系统方面,PCIe 6.0 的目标用户正在寻找在系统级别验证其 SoC 的解决方案。在 SoC 上运行系统级有效负载需要更快的基于硬件的预硅解决方案。基于 Synopsys IP 的 Synopsys 事务处理器可实现快速验证硬件解决方案,包括用于验证用例的 Synopsys ZeBu® 仿真系统和 Synopsys HAPS® 原型系统。

Synopsys 协议验证解决方案与 Synopsys 验证系列产品原生集成,包括 Synopsys Verdi® 调试器以及使用 Synopsys VC Execution Manager 进行回归管理和自动化。

Synopsys 一直是 PCIe 规范的主要贡献者之一,并继续为 PCIe 6.0 和 Testsuite 提供业界首个采用 Synopsys 验证 IP 的验证解决方案。

此外,适用于 PCIe 6.0 的 Synopsys DesignWare IP 包括控制器和 PHY 解决方案,支持早期开发 PCIe 6.0 片上系统 (SoC) 设计。

审核编辑:郭婷

-

解码器

+关注

关注

9文章

1226浏览量

43820 -

crc

+关注

关注

0文章

206浏览量

30993 -

PCIe

+关注

关注

16文章

1494浏览量

89099

发布评论请先 登录

基于FPGA的循环冗余校验实验系统

验证PCIe 6.0中的轻量级前向纠错和强循环冗余校验功能

验证PCIe 6.0中的轻量级前向纠错和强循环冗余校验功能

评论