需要多芯片小芯片互连

云、AI、5G、汽车和高性能计算 (HPC) 等关键应用,加上半导体缩放的快速变化的物理和经济性,正在引领多样化的集成趋势和新的芯片到芯片用例。半导体小芯片封装(多芯片)正在帮助集成商采用新方法来构建可扩展的模块化设计。

多芯片 SoC 架构能够以更低的价格实现比单片设计更大、更强大的 SoC。它还使产品具有更好的可扩展性和可组合性,从而加快上市时间并提高灵活性,以满足多个细分市场的需求。芯片间接口是多芯片SoC趋势的关键推动因素。芯片间接口需要以最低延迟和最高能效在芯片之间提供无缝互连,以免影响系统性能。

小芯片标准概述

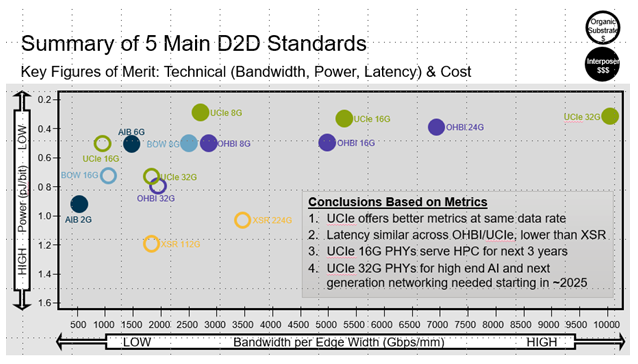

OIF 超短距离 (XSR)、开放计算项目线束 (BOW) 和 OpenHBI (OHBI) 以及芯片联盟高级接口总线 (AIB) 是 2D 和 2.5D 封装类型的联盟和标准。这些标准提供了带宽与功率的权衡,主要侧重于提供小芯片之间的传输连接。

UCIe 小芯片标准

2022 年 1 月,新成立的通用小芯片互连快递 (UCIe®) 组织宣布批准 UCIe 规范。Synopsys 是 UCIe 组织的贡献成员,作为 EDA 和 IP 解决方案的行业领导者,为行业联盟带来了独特的视角。

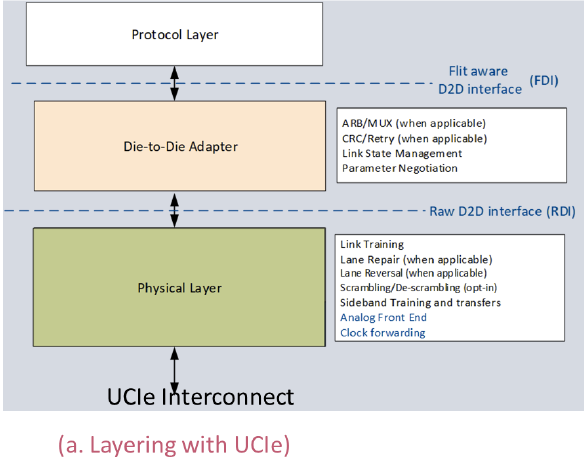

UCIe涵盖了完整的协议堆栈以及物理层,因此它可以解决最相关的多芯片SoC用例。相比之下,其他标准工作主要集中在接口的物理层方面。UCIe 规范通过边缘效率、电源效率和延迟来衡量其提出的性能指标非常引人注目,这将在推动标准采用方面发挥重要作用。以下是从小芯片互连标准角度来看UCIe 0.《》的关键协议功能:

• 非相干和相干芯片到芯片链路的协议层定义 – 实现 FLIT(流量控制单元)以通过 UCIe 传输 PCI Express® (PCIe®) 和计算快速链路

(CXL) 流量,并能够扩展现有的软件生态系统

– 具有供应商定义的 FLIT 的流模式,用于自定义协议 • 协议

不同层之间的首创信令接口 – FLIT 感知芯片到芯片接口 (FDI)

– 原始数据芯片到芯片接口 (RDI) • 物理互连信令接口,具有单模块和多模块

的使用模型 – 数据速率高达 32 GT/s

— 标准封装(x16 通道)

和高级封装(x64 通道),通道范围为 25mm/2 mm

— 传输模式为串行模式,小芯片之间共享时钟

– 宽度/工作

速率降低 – 用于数据路径的主频段接口,用于控制和调出

的边带接口 – 车道修复和车道反转功能

• 通过 UCIe 重定时器实现更大的通道长度

与大多数其他标准不同,UCIe提供软件堆叠以及物理层以实现关键功能参数。下图概述了每一层的 UCIe 堆栈和功能方面。

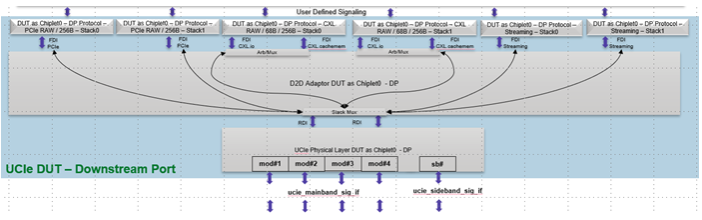

考虑到整体特性,UCIe设计可以采用多种拓扑结构。以下是一些表示下游和上游端口的 DUT 类型:

• 带 RDI 接口和 UCIe 物理接口的 PHY DUT • 带 RDI 和 FDI 接口的芯片到芯片 DUT • 带 UCIe 物理接口

的重定时 DUT • 具有协议、芯片到芯片和物理层

的全栈 这些 DUT 类型需要更广泛的验证方法集,以满足 IP 到系统级使用模型的需求。

主要验证挑战

让我们考虑充当下游端口的 UCIe 全栈 DUT。下图概述了下游端口的典型 UCIe 堆栈设计,该端口能够使用单个堆栈或多个堆栈支持流/PCIe/CXL 流量。物理层可以是单个模块,也可以是能够采用标准或高级封装的多模块。支持的确切功能在初始链接和发现阶段进行协商。

以下是验证多协议、多堆栈和多模块 DUT 类型时遇到的关键验证方面和挑战:

• DUT 的设备功能发现和配置设置,以匹配使用边带接口

的上游端口功能 • RDI、FDI、vLSM 和链路状态机和转换 • 评估芯片到芯片层的重试机制行为 • UCIe 物理层的训练、车道反转和车道修复功能

• 基于发现的功能

生成协议层

流量的有效方法 • 确保 PCIe/CXL 原始模式或 UCIe 定义的 FLIT 模式的可靠流量,包括协议层的完整性和数据加密 • 通过流操作

模式定义的自定义协议的端到端数据完整性 • 基于物理层

通道宽度以及数据速率能力是否满足设计预期的整体协议性能吞吐量

审核编辑:郭婷

-

AI

+关注

关注

87文章

30643浏览量

268824 -

HPC

+关注

关注

0文章

314浏览量

23745 -

5G

+关注

关注

1354文章

48420浏览量

563888

发布评论请先 登录

相关推荐

分享一个适用于业余无线电VoIP解决方案

jscrane/TTS库不适用于NodeMCU 1.0吗?

Synopsys为Arm AMBA CXS的VIP提供EDA验证解决方案

适用于工业应用的TCP/IP协议栈网络解决方案

适用于UCIe 1.0的新思科技协议验证解决方案

适用于UCIe 1.0的新思科技协议验证解决方案

评论