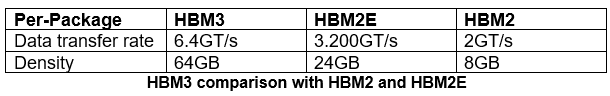

在这个技术革命的时代,人工智能应用程序、高端服务器和图形等领域都在不断发展。这些应用需要快速处理和高密度来存储数据,其中高带宽内存 (HBM) 提供了最可行的内存技术解决方案。我们之前的内存博客 HBM2 内存用于图形、网络和 HPC 探索了该协议,数据传输速率为 2GT/s,堆叠架构为 8-Hi 堆栈(8 芯片)。HBM2 扩展 (HBM2E) 架构在 HBM2 的基础上提供了进一步的改进,具有 3.2 GT/s 传输速率和 12-Hi 堆栈架构,单个芯片密度高达 8Gb,总密度为 24GB。

HBM3 架构提供 16Gb 的芯片密度和 16-Hi 堆栈,从而提供 64GB 的总密度。HBM3的最大数据传输速率可以达到6.4GT / s。

HBM3:DRAM 技术的未来

HBM3 是一种 3D DRAM 技术,可以堆叠多达 16 个 DRAM 芯片,通过硅通孔 (TSV) 和微凸块互连。

让我们快速浏览一下 HBM3 中的关键差异化功能。

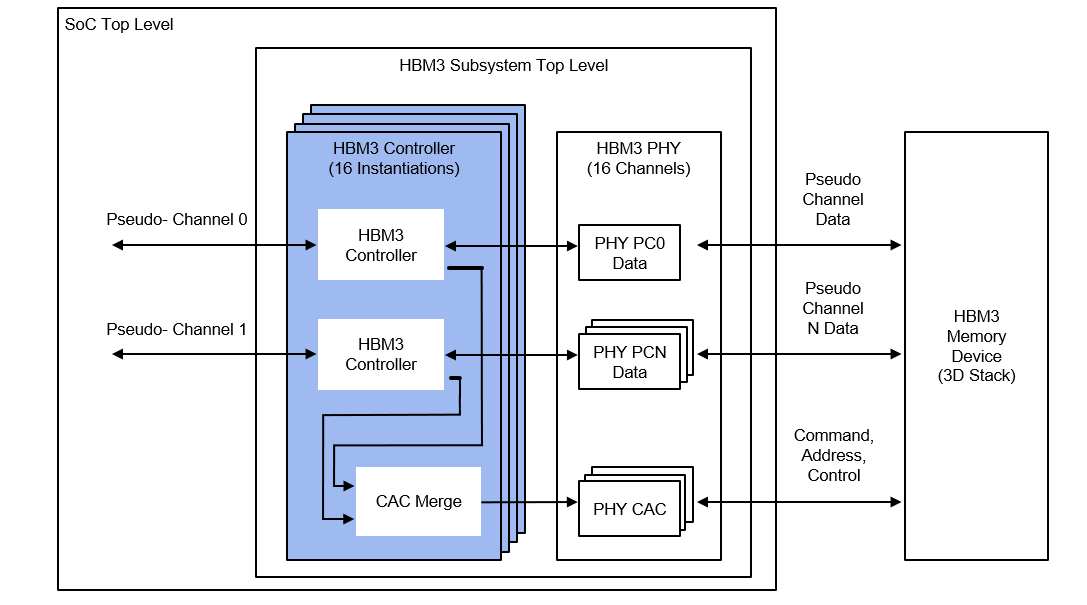

与 HBM2 架构一样,HBM3 提供两个独立的行和列命令接口,允许激活/预充电与读/写并行发出。这简化了控制器操作并增加了带宽。HBM3 支持 64 位的 DQ 宽度和 8n 预取架构,因此允许 512 位内存读写访问。HBM3 具有伪通道模式架构,将通道划分为两个单独的子通道,每个子通道 32 位 I/O。

HBM3 具有双时钟架构,DDR 时钟用于命令,DDR WDQS 时钟用于数据。WDQS 时钟是命令时钟的 2 倍,由控制器驱动,用于读取和写入操作。

HBM3 还提供片上 ECC 计算功能,用于错误检测和严重性引脚,以指示错误的严重性。HBM3器件将支持读/写元数据位,错误清理机制,错误透明协议和故障隔离限制,这将有助于实现高系统可靠性,可用性和可维护性(RAS)。向主机传输严重性有助于向主机提供有关错误类型的反馈。

HBM3 还引入了新的培训,即 WDQS2CK 培训(写入均衡)、WDQS 振荡器和占空比校正。这些培训取自新的 DRAM 系列,如 DDR5 和 LPDDR5。

总而言之,HBM3 是性能、功耗和外形尺寸受限系统的突破性内存解决方案,提供高带宽和高密度。HBM16 采用 3 通道堆叠架构,提供最佳外形尺寸之一。

审核编辑:郭婷

-

服务器

+关注

关注

12文章

9342浏览量

86198 -

人工智能

+关注

关注

1797文章

47867浏览量

240781 -

HBM

+关注

关注

0文章

388浏览量

14853 -

HBM3

+关注

关注

0文章

74浏览量

180

发布评论请先 登录

相关推荐

器件高密度BGA封装设计

用于高密度电路板的器件

探讨高密度小间距LED屏工艺

高密度PCB(HDI)检验标准

光迅科技:高密度MPO连接器,面向400G应用

光迅科技推出面向400G应用的高密度MPO连接器

SK海力士成功开发出业界第一款HBM3 DRAM 内存芯片

Rambus通过9.6 Gbps HBM3内存控制器IP大幅提升AI性能

HBM3:用于解决高密度和复杂计算问题的下一代内存标准

HBM3:用于解决高密度和复杂计算问题的下一代内存标准

评论