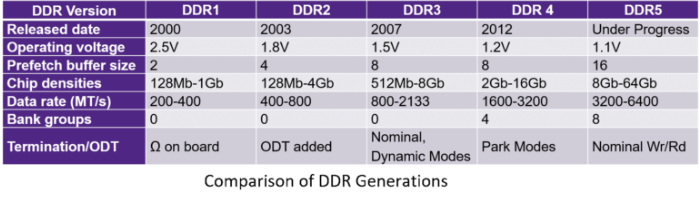

联合电子设备工程委员会(JEDEC)多年来一直在开发和维护DRAM标准,定义了DRAM标准等新兴内存标准。最新的公告宣布第五代DRAM,DDR5,终于准备好发布。定义DDR5的工作始于2017年,目标是提供一个可以超越DDR4速度限制16 Gb和3200 MT / s的标准。其目的是解决数据中心高端服务器周围的新应用程序,以处理AI / ML工作负载。

如今,DDR5 的数据速率(3200MT/s 至 6400MT/s)、内存接口带宽(51.2GB/s)和密度(8Gb 至 64Gb)显著提高。DDR5 技术具有许多与性能(更多银行、银行组、BL16、增强型刷新模式、DFE)、可靠性(芯片上 ECC、用于读取的数据 CRC)、低功耗(写入模式、VDD/VDDQ/VPP 的较低电压电平)和增强型 PHY 训练(CS 训练、读取训练模式、内部写入均衡、改进的 CA 训练)相关的许多新功能,以处理高频和精度要求。即使以 DDR30 速度运行,这些功能也允许带宽增加多达 4%。

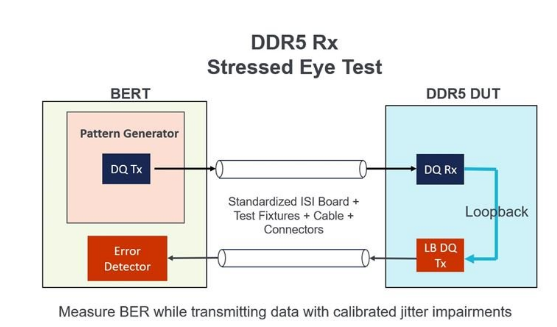

DDR5 具有更高的速度和更小的占用空间。由于电压要求从1.2V降低到1.1V,它还有望提高电源效率。电压要求的降低给DIMM供应商带来了额外的抗噪性复杂性。它将需要额外的功能,例如决策反馈均衡,以改善数据眼。更高的速度和更低的电压也会增加信号完整性的复杂性,需要额外的培训机制来确保正常运行。这反过来又会增加验证的复杂性,需要对真实场景及其覆盖范围进行可视化和建模。

大多数主要的内存供应商已经发布了发布DDR5内存设备的计划。他们已经开始对采用5纳米级(10z)工艺的下一代DDR1设备进行采样。随着 DDR5 的 4800 MT/s,内存供应商看到 DDR85 的 4 MT/s 性能提高了 ~3200%。随着更高速度的料箱投入生产,性能预计将提高数倍。

预计DDR5最终将占据DDR4市场的主要份额。预计立即利用率将围绕高端服务器和数据中心,但最终也可能用于台式机和笔记本电脑。来自领先处理器公司的集成内存控制器预计将很快采用DDR5。

新思科技验证 IP (VIP) 支持 JEDEC® 存储设备 DDR5 SDRAM 标准,并提供完整的验证解决方案。适用于 DDR5 的 Synopsys VIP 与行业标准的通用验证方法 (UVM) 兼容,可在所有领先的模拟器上运行。DDR5 VIP 支持 DRAM 和 DIMM 配置,部署在面向高端服务器、云和下一代计算的市场领导者中。

审核编辑:郭婷

-

电源

+关注

关注

184文章

17735浏览量

250490 -

服务器

+关注

关注

12文章

9203浏览量

85527 -

DDR5

+关注

关注

1文章

424浏览量

24155

发布评论请先 登录

相关推荐

DDR5内存接口芯片组如何利用DDR5 for DIMM的优势?

新一代DDR5内存模组密集发布,支持DDR5 CPU随后就到!

Introspect DDR5/LPDDR5总线协议分析仪

DDR3/4都还没玩够,DDR5已经来啦

DDR5这么快,为啥还能那么稳?

DDR5内存和DDR4内存差异总结

从DDR4到DDR5花了将近10年,DDR5将有什么重大突破?

ddr5的主板可以用ddr4内存吗 几代CPU才能上DDR5

ddr5为什么能跑得那么稳呢

DDR5 – 关闭并运行

DDR5 – 关闭并运行

评论