性能仍然是任何复杂片上系统 (SoC) 设计的关键因素。此外,复杂性每天都在增加,这给工程师跟踪设计性能带来了挑战,但他们的任务是不断提高芯片性能。在运行时,性能工程师不仅可以开发功能,还可以检查受新模块影响的设计性能。在传统方法中,功能开发和性能分析是顺序任务,并一个接一个地执行。

Synopsys 的 Verdi 性能分析器支持运行时指标,以帮助实现所需的芯片性能。Verdi 性能分析器允许功能开发人员在早期运行时执行基于性能的检查。本博客以内存协议为例,但该流程与协议无关,适用于所有 SoC 设计。

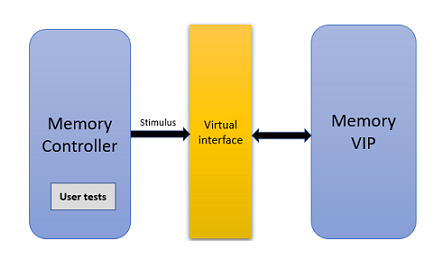

典型的SOC设计由许多子系统组成,例如存储器子系统,互连总线和处理器,每个子系统的验证都使用基于UVM的VIP独立完成。在基于 UVM 的环境中,控制器设计用于向验证 IP 发送测试激励,其结果可以通过 VIP 本身进行研究。VIP 可以提供可用于分析系统性能的性能数据,并帮助查找软件和硬件瓶颈。

API是用系统Verilog语言编写的,很容易集成到任何测试台中。Verdi 性能分析器解决方案允许基于时间片(默认为整个模拟时间)创建实例,并可进一步用于创建自定义配置和设置约束值。用户可以添加断点并在所需时间内评估性能。启用和禁用性能分析是许多设计人员在最短时间内找到确切性能漏洞的关键优势。如果在整个模拟中出现少量事务错误,则只能在该时间内启用性能指标,从而使用较少的内存和时间。此功能支持适用于所有 Synopsys 协议。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

20339浏览量

255298 -

soc

+关注

关注

40文章

4635浏览量

230270 -

Verilog

+关注

关注

31文章

1374浏览量

114732

发布评论请先 登录

优化HBM2E运行时性能

优化HBM2E运行时性能

评论