随着数据中心和人工智能应用成为中心舞台,过去几年见证了各种高带宽互连技术的出现。计算高速链路 (CXL) 是一种有抱负的新型互连技术,适用于高带宽设备,例如带内存的加速器、高密度计算卡和由 GPU 组成的加速器。Synopsys 开发了一个全面的 CXL 验证子系统,计划发布其第一个 CXL 应用程序的早期采用者已经使用该系统。CXL 验证子系统利用业界流行的 Synopsys PCI Express 验证 IP。

CXL 是一种在主机(通常是 CPU)和设备(通常是附加了内存的加速器)之间实现高带宽、低延迟链接的技术。CXL 堆栈专为低延迟而设计,使用 PCIe 电气和附加卡的标准 PCIe 外形规格。CXL 使用灵活的处理器端口,可以自动协商到标准 PCIe 事务协议或备用 CXL 事务协议。

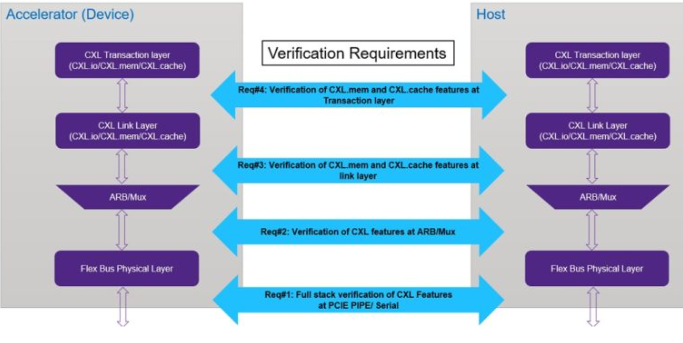

CXL 规范建立在完善的 PCIe 基础架构之上,并利用其基于层的架构,每一层都有一个目标角色。

图 1:CXL 分层体系结构和验证要求

CXL 事务层

CXL 事务层分为 PCIe/CXL.io 事务层和 CXL.cache+CXL.mem 事务层。CXL.cache+CXL.mem 事务层支持生成请求、响应和数据的功能。

CXL 链路层

CXL 链路层分为 PCIe/CXL.io 链路层和 CXL.cache+CXL.mem 链路层。链路层是事务层和物理层之间的中间层。它有助于维护整个链路上的事务的可靠性。

CXL ARB/MUX

CXL ARB/MUX 提供 CXL.io 和 CXL.cache+CXL.mem 流量的仲裁和多路复用,朝向物理层。

CXL 物理层

物理层由逻辑子块和电气子块组成。逻辑子块最初在 PCIe 模式下运行,并根据备用协议协商切换到 CXL 模式。电气子块始终遵循 PCIe 规范。

对于 CXL 流量,数据速率与 PCIe 规范定义的速率一致。在 CXL 模式下,支持 8 GT/s、16 GT/s 或 32 GT/s 的数据速率。在 CXL 模式下,支持 x16、x8、x4、x2 的链接宽度。x1 的链路宽度也支持降级模式。

数据的爆炸式增长以及AI和加密的快速创新催生了GPU加速器,需要与处理器建立高性能连接。虽然存在其他互连协议,但 CXL 在提供 CPU/设备内存一致性、降低设备复杂性以及捆绑在单一技术中的行业标准物理和电气接口方面是独一无二的,可实现最佳的即插即用体验。

审核编辑:郭婷

-

主机

+关注

关注

0文章

1074浏览量

36886 -

PCIe

+关注

关注

16文章

1502浏览量

89128 -

加速器卡

+关注

关注

0文章

19浏览量

8910

发布评论请先 登录

揭开特斯拉超级大厂Gigafactory的神秘面纱

[分享]揭开zzz 手机神秘面纱

揭开连接出现小叹号不能上网问题的神秘面纱

苹果iPhone手机神秘面纱被揭开

揭开vivo APEX全面屏的神秘面纱

MT-001: 揭开公式(SNR = 6.02N + 1.76dB)的神秘面纱

揭开CXL的神秘面纱:概述

揭开CXL的神秘面纱:概述

评论