SoC 性能是市场上的关键竞争优势,协议 IP 和互连的选择和配置旨在最大限度地提高所述性能。一个典型的例子是使用 HBM(高带宽内存)技术和内存控制器。目前在第三代, HBM 拥有高性能, 同时使用更少的功率, 比 DDR 小得多的外形.也就是说,团队如何确保在其 SoC 设计的上下文中交付性能?

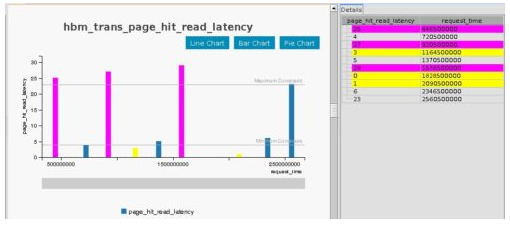

借助协议性能分析和调试工具(如Verdi Performance Analyzer),用户可以轻松可视化重要的性能指标,例如页面点击读取延迟等。(见下图)。此外,他们可以为每个指标设置最小和最大约束,并让该工具自动识别违反这些约束的情况(黄色和紫色)。通过与Verdi协议分析器的直接集成,他们可以在几秒钟内找到违规交易的根本原因。

虽然这对于调试非常强大且非常有用,但它只是冰山一角。团队可以在他们的 SoC 验证环境中使用更多的自动化,特别是对于 SoC 性能验证,由于项目截止日期,这些验证经常被压缩甚至被忽略。Synopsys SoC 验证自动化解决方案正是为此目的而构建的 – VC AutoTestbench 用于自动生成测试平台,VC VIP AutoPerformance 用于自动生成性能激励,Verdi Performance Analyzer 用于自动协议性能分析和调试。

审核编辑:郭婷

-

控制器

+关注

关注

113文章

16536浏览量

180135 -

DDR

+关注

关注

11文章

717浏览量

65682 -

soc

+关注

关注

38文章

4229浏览量

219575

发布评论请先 登录

相关推荐

[推荐]新世纪网络突破就在这里!

为什么说数字电源是正确的选择?答案就在这里

再见瓶颈 – 自动SoC性能验证就在这里

再见瓶颈 – 自动SoC性能验证就在这里

评论