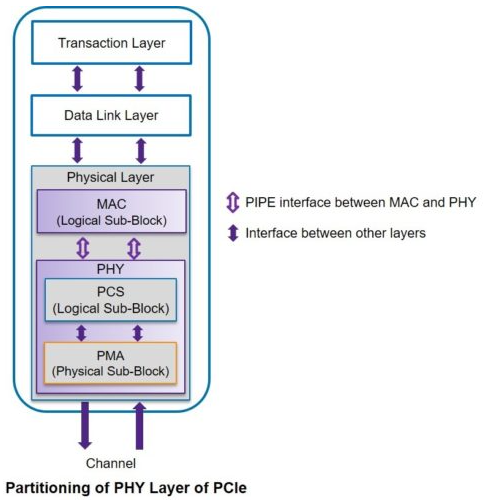

PCIe 是一种多层串行总线协议,可实现双单工链路。由于其专用的点对点拓扑,它提供高速数据传输和低延迟。为了加快基于 PCIe 的子系统的验证和设备开发时间,英特尔定义了 PIPE(PCI Express 的 PHY 接口)架构。PIPE 是 PHY 子层(PCS – 物理编码子层)和 MAC(媒体访问层)之间定义的标准接口。

PIPE 的第一个稳定版本于 2 年作为 PIPE 0.2007 发布。随着时间的推移,PIPE 已经发展到支持更高的速度和下一代 PCIe 规范的附加功能。4年初发布的PIPE 4.1.2017规范完全符合支持4GT / s速度的PCIe 0.16基本规范。它比 PIPE 4.3 有了重大改进,同时保持了向后兼容性。下图说明了 PIPE 接口和 PCIe 的 PHY 层的分区。

以下列表总结了 PIPE 4.4.1 和 PIPE 4.3 中新添加/修改的功能。

标称空弹性缓冲区模式: 与标称半满弹性缓冲区模式相比,以更小的最坏情况和平均延迟提供更好的数据流优化。

引入消息总线接口的 Rx 裕量:提供一种使用少量导线启动和参与非延迟敏感型 PIPE 操作的方法。它还可以在不添加额外电线/信号的情况下执行刚刚发布的 PIPE 5.0 操作。

SRIS:提供一种方法来指示有关独立 Refclk 独立 SSC 体系结构支持的 PHY。

MAC 和本地 PHY 之间的第 4 代均衡:为 Gen4 均衡提供专用控件,而不是 Gen3 均衡。

L1 次州电源管理:通过引入 RxEiDetectDisable 和 TxCommonModeDisable 信号提供超低功耗操作。

Tx合规性和TxElecIdle信号采样机制。

审核编辑:郭婷

-

接口

+关注

关注

33文章

9601浏览量

157628 -

总线

+关注

关注

10文章

3060浏览量

91869 -

PCIe

+关注

关注

16文章

1479浏览量

88929

发布评论请先 登录

钛金PCIe Gen4控制器的核心特性与技术细节

请问Virtex7 GTX如何生成PIPE接口PCIE PHY?

了解PIPE4.4规范及PCIe 4.0的开发设计

迈威科技PCIe Gen4 NVMe SSD控制器面世!推进下一代技术发展

PCIe Gen 4协议分析仪的竟然那么强大!

三星开发了基于PCIe Gen4的SSD新产品PM1733

迈入高速新进程,上海宝存推出PCIe Gen4企业级存储

为什么PCIe Gen3/Gen4不使用CXL

FORESEE成功研发出旗下首款PCIe Gen 4×4 SSD

西部数据推出高性能、轻薄低功耗的PCIe Gen4 NVMe SSD

江波龙推出PCIe Gen4×4无缓存主控SSD XP2000d

江波龙FORESEE推出PCIe Gen4×4无缓存主控SSD——XP2000

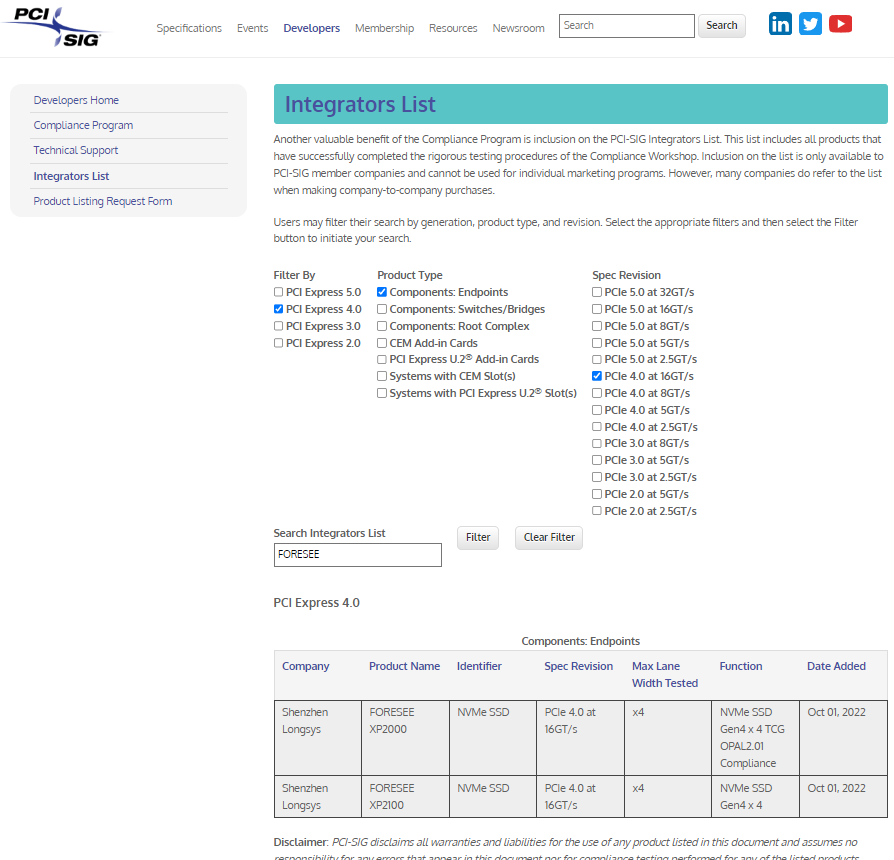

FORESEE PCIe Gen4 SSD系列产品通过PCI-SIG兼容性认证

江波龙FORESEE PCIe Gen4 SSD系列产品通过PCI-SIG兼容性认证

FORESEE推出首款自研PCIe Gen4 BGA SSD,轻薄终端的存储“更优解”

PCIe PIPE 4.4.1:PCIe Gen4的推动者

PCIe PIPE 4.4.1:PCIe Gen4的推动者

评论