关于这个问题,我们看看身边的同行都是如何回答的吧:

工程师A:这个问题其实...说白了主要是大家都在用,或者说大部分时候it works。

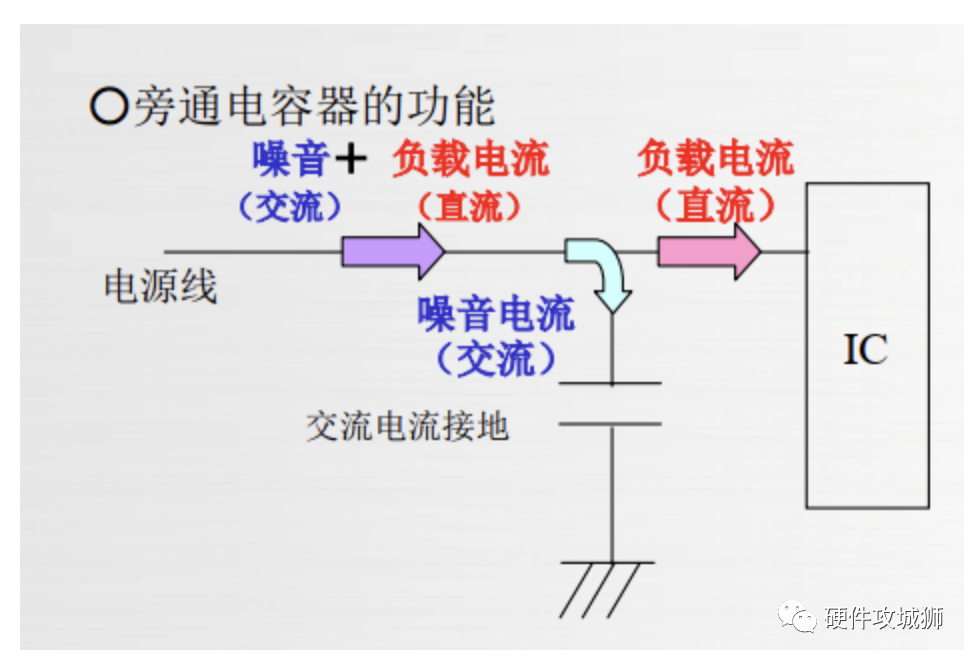

其实多看一些电源完整性相关的资料能发现不少讨论,100nF的去耦电容作用频段一般认为是几MHz到二三十MHz,再配合板上的bulk电容,能实现从很低频到二三十MHz这个频段内全程较低的电源阻抗,大部分的应用已经够用了。另外一方面因为大家形成了用100nF去耦的习惯,这样的电容通常也有大量的库存,采购价格也便宜,所以也没必要标新立异去选其它容值,比如82nF,效果可能差不多,但你这么用,采购的同事肯定会找你的麻烦。

另外一方面,现在大量的高速IC尤其是高速数字IC会集成高频去耦电容,所以片外只用搞一些相对低频的去耦就够了,一般做法就是搞一堆几百nF级别的电容。而且片上集成的高频去耦电容的效果比板上的强多了,板上去耦电容作用频段的极限大概就两三百MHz吧,对于现在动辄几百MHz往上的时钟频率来说主要起安慰效果。

其他容值的去耦电容也不是不用,低频模拟电路就会用上uF级别的去耦电容,PLL啊时钟驱动器啥的又可能用上pF级别的,需要具体情况具体分析,分析不来怼个100nF上去大部分情况下没啥问题。我最近遇到个问题,用1nF的去耦电容效果比用100nF的好,因为需要作用的频段是200MHz左右。

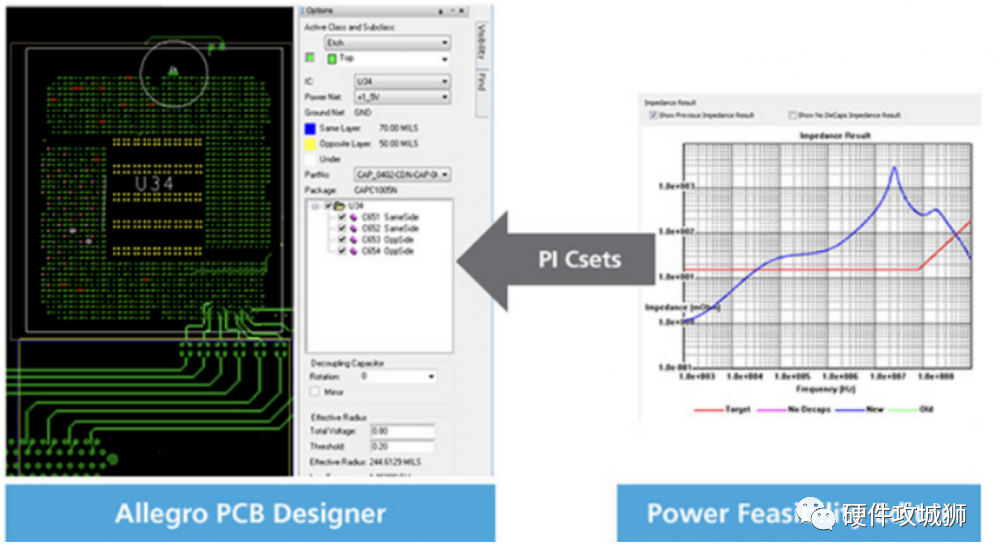

工程师B:放很多100nf是粗糙的设计,合理的做法是做PDN仿真,在电源平面所有频段控制阻抗满足要求。

100nF电容成本较低,在不做详细分析时,多放置一些,可以在1~100MHz之间都提供较低的交流阻抗,因此一般也没什么问题。

不考虑成本,同封装下容量越大滤波效果越好,1uF 0402比100nF 0402在全频段滤波效果都好。

工程师C:100nF电容可以更好地去除高频分量,小电容通常具有低ESR、低引线和内部电感、较高的自谐振频率和较高频率下的低阻抗。所以,在高频数字电路的PCB板上,100nF很重要,然后作为一种设计习惯,这种方式被应用于很多数字电路设计中,成为一种规范。但其实,在以往调试很多电路板时,这种退耦效果可能并不能量化和直观体现出来,是极端环境下的一种性能提升。

退藕电容并不是一个精确数值,因为每个电路的情况都不一样,也不一定要100nF,而且常用较多的100nF是5%精度,对精度要求并不高,但100nF电容量大,封装可以做到很小,容易制造,成本低,方便采购。前提是100nF对大部分数字IC来说,有较好的表现。

审核编辑:刘清

-

pll

+关注

关注

6文章

776浏览量

135181 -

电源完整性

+关注

关注

9文章

209浏览量

20731 -

退耦电容

+关注

关注

1文章

29浏览量

9580 -

时钟驱动器

+关注

关注

0文章

33浏览量

13837

原文标题:为什么退耦电容通常选100nF?

文章出处:【微信号:电子工程师笔记,微信公众号:电子工程师笔记】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

HLW8012功率芯片的电压采集100nF的电容有什么用?

请问104电容与100nf的电容能随便替换吗?

运放为什么要使用退耦电容呢?

什么是退耦电容

MCU退耦电容引发的EMC血案

为什么退耦电容通常选100nF呢?

为什么退耦电容通常选100nF呢?

评论