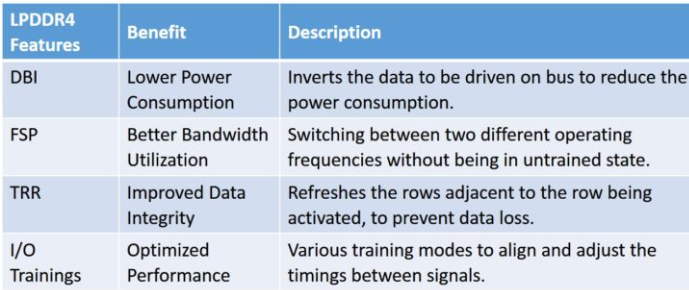

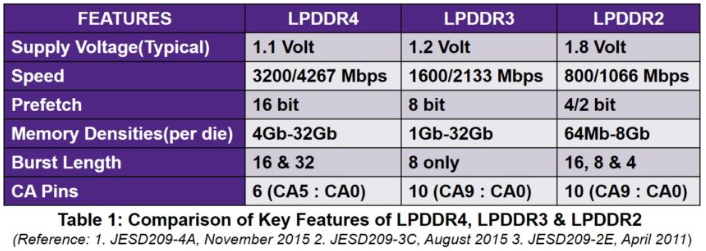

移动行业正在以非常快的速度增长,其对数据和带宽的永无止境的渴望。我们见证了从拨号盘到触摸屏,从黑白显示器到具有数百万种颜色的QHD 4k显示器,以及从KB到GB的内存空间在很短的时间内的变化。最大的挑战是在不影响性能或在功耗列中添加任何重要数字的情况下增加带宽。应对这一挑战的解决方案是JEDEC发布的LPDDR或移动DDR标准。该标准已经进行了多次修订,最新的是LPDDR4。LPDDR4 提供 4266 Mbps 的数据带宽,几乎是 LPDDR3 的两倍。与 LPDDR3 相比,它还显著降低了功耗。

在本博客中,我们将讨论使 LPDDR4 在功耗、带宽利用率、数据完整性和性能方面高效的功能。

DBI(数据总线反转)

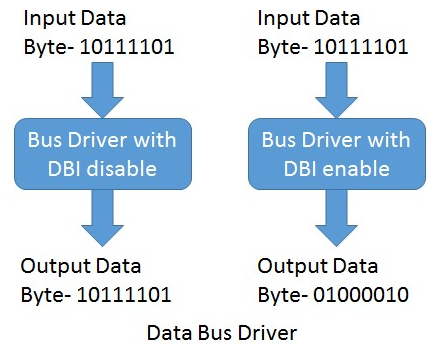

LPDDR4 中引入了一种新的 I/O 信令方案,称为低压摆幅端接逻辑 (LVSTL)。LVSTL 使用的电压电平明显低于以前版本的 LPDDR 中使用的电压电平。这种信令方案的另一个优点是,当低电平(0)通过I/O驱动器驱动时,它不消耗终止功率。这意味着如果数据流中有更多的零,则消耗的功率将更少。引入了 DBI 功能,以在数据流中保留比 1 更多的零。DBI 在字节级粒度下工作。每当一个字节包含超过四个位数的位为 <> 时,驱动程序将反转整个字节并发送相应的数据掩码反转 (DMI) 位,以通知接收器相应的字节已反转。

FSP(频率设定点)

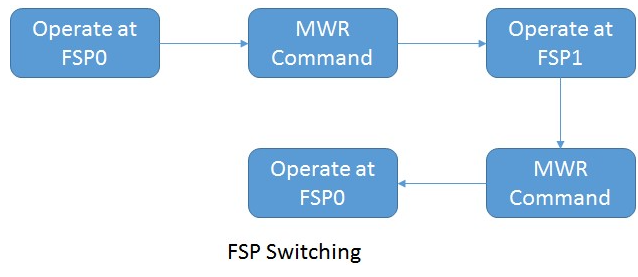

LPDDR4 增加了两组物理寄存器空间(FSP0 和 FSP1),无需重新训练即可在两个不同的工作频率之间切换。这些寄存器集以两种不同的频率存储DRAM所需的所有操作参数,一种处于有效模式,另一种处于阴影模式。DRAM 将使用两种频率进行训练,参数将在命令总线训练模式下存储在寄存器集中。FSP0 和 FSP1 之间的切换,反之亦然,只需在模式寄存器上写入即可快速完成。

TRR(目标行刷新)

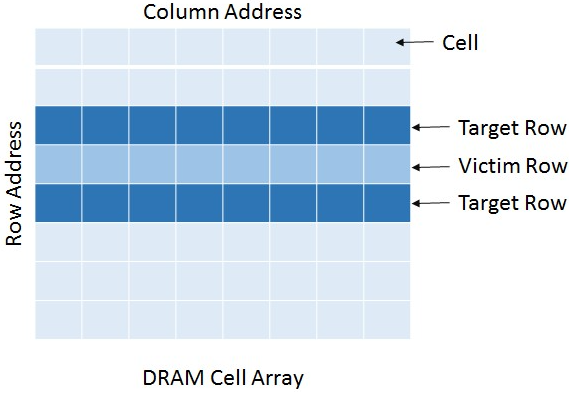

在相同芯片尺寸内,内存密度的增加会导致 DRAM 单元更小。与较大的电池相比,较小的电池可以存储较小的电荷,这反过来又可以降低噪声容限,从而使系统更容易出现数据错误。此外,密集放置的细胞对串扰干扰的免疫力较低,最终导致数据错误。要对行执行任何数据操作,需要先激活它。这里的“激活”意味着将行的电池置于较高的电压电平,而该行的其他行保持较低的电压电平。当一行被快速激活时,其电压电平也会相应变化,最终由于电池的靠近而加速相邻行电池的放电速率。由于DRAM单元以电荷的形式将数据信息存储在电容器中,这些电荷往往会在一段时间内放电,因此在刷新周期内需要一个刷新周期来保留存储的电荷。由于相邻行电池的放电速率加快,可能会导致数据丢失,因为电容器在下一个刷新周期到来之前已完全放电。为了克服这种情况,LPDDR4 引入了目标行刷新 (TRR) 机制。TRR 限制刷新周期内单行的最大激活次数(MAC 计数)。每当每行的激活计数(目标行)达到 MAC 计数时,TRR 过程将刷新相邻行(受害行)以避免数据丢失。

I/O 信号培训

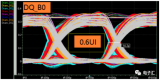

LPDDR4 提供了多种训练,以对齐或重新调整 I/O 信号相对于 CLK 或其他信号引入的延迟。根据 LPDDR4 的标准物理接口定义,有 CLK、CS、CA、DQ 和 DQS 信号需要正确对齐才能成功传输数据。由于CA线在CLK信号处采样,因此CA和CLK之间应存在适当的相位关系。类似地,DQ在DQS信号上采样,因此两者之间应该存在相位关系。为了保持这些阶段关系,LPDDR4提出了训练机制。让我们看看这些:

指挥总线培训:这用于将CS和CA信号相对于CLK信号对齐。上电时,接收器配置为低速操作。在高频下工作时,必须对接收器进行训练。时序裕量需要根据CBT程序实现的更高时钟频率重新调整。CBT 模式的进入和退出由模式寄存器写入命令控制。在CBT模式下,DRAM将切换到FSP_OP设置,这也需要进行训练。DRAM 在 CS 信号处对 CA 总线进行采样,并将采样信号的反馈提供给控制器,以便对 CS 和 CA 信号进行定时调整。

写入分级:这用于调整 DQS 输入信号相对于 CLK 信号的延迟。写均衡训练模式的进入和退出由模式寄存器写入命令控制。DQS 信号由控制器驱动,DRAM 对 DQS 边缘的 CLK 信号进行采样。DRAM 通过在 DQ 上提供捕获的 CLK 级别的反馈来响应控制器。此反馈可识别 DQS 相对于 CLK 的超前或滞后,以便控制器可以相应地重新调整延迟。

写作训练(DQS-DQ训练): 这用于将 DQ 输入信号延迟与 DQS 输入信号对齐。进入写入训练模式时,MPC WR_DQ_FIFO命令必须由控制器发出。此命令在 DRAM 中写入用户定义的数据,然后控制器发出 MPC RD_DQ_FIFO命令从同一位置读回数据,并比较写入和读取的数据以重新调整 DQ 线路上的延迟。

这些功能使 LPDDR4 成为一个完整的封装,非常适合用作任何移动 SoC 中的 RAM。这些功能必须在基于 LPDDR4 的 SoC 设计的任何验证计划中解决。Synopsys 为 LPDDR4 提供了完整的验证解决方案,包括 JEDEC 和供应商部件的运行时选择、一组内置协议、时序和数据完整性检查、可配置的时序参数、内置的功能覆盖范围和验证计划以及对内存的后门访问。

审核编辑:郭婷

-

显示器

+关注

关注

21文章

4983浏览量

140100 -

寄存器

+关注

关注

31文章

5357浏览量

120589 -

LPDDR4

+关注

关注

1文章

38浏览量

23406

发布评论请先 登录

相关推荐

论手机运行内存 LPDDR 4X在LPDDR4的基础上有哪些提升

求助,用于LPDDR4 6GB的imx8m-plus替代选项

使用了IMX8M Plus+PCA9450C+LPDDR4,如何才能降低SOC和LPDDR4的工作频率?

lpddr4频率无法修改怎么解决?

LPDDR4:是什么让它更快并降低功耗

Versal ACAP DDRMC-DDR4、LPDDR4和LPDDR4X外部参考时钟设计指南

LPDDR4是什么意思?LPDDR4X内存是什么意思?

DDR4、LPDDR4和LPDDR4x的区别

LPDDR4:移动SoC RAM的整体封装

LPDDR4:移动SoC RAM的整体封装

评论