第2章一个简单的UVM验证平台

2.4 UVM的终极大作:sequence

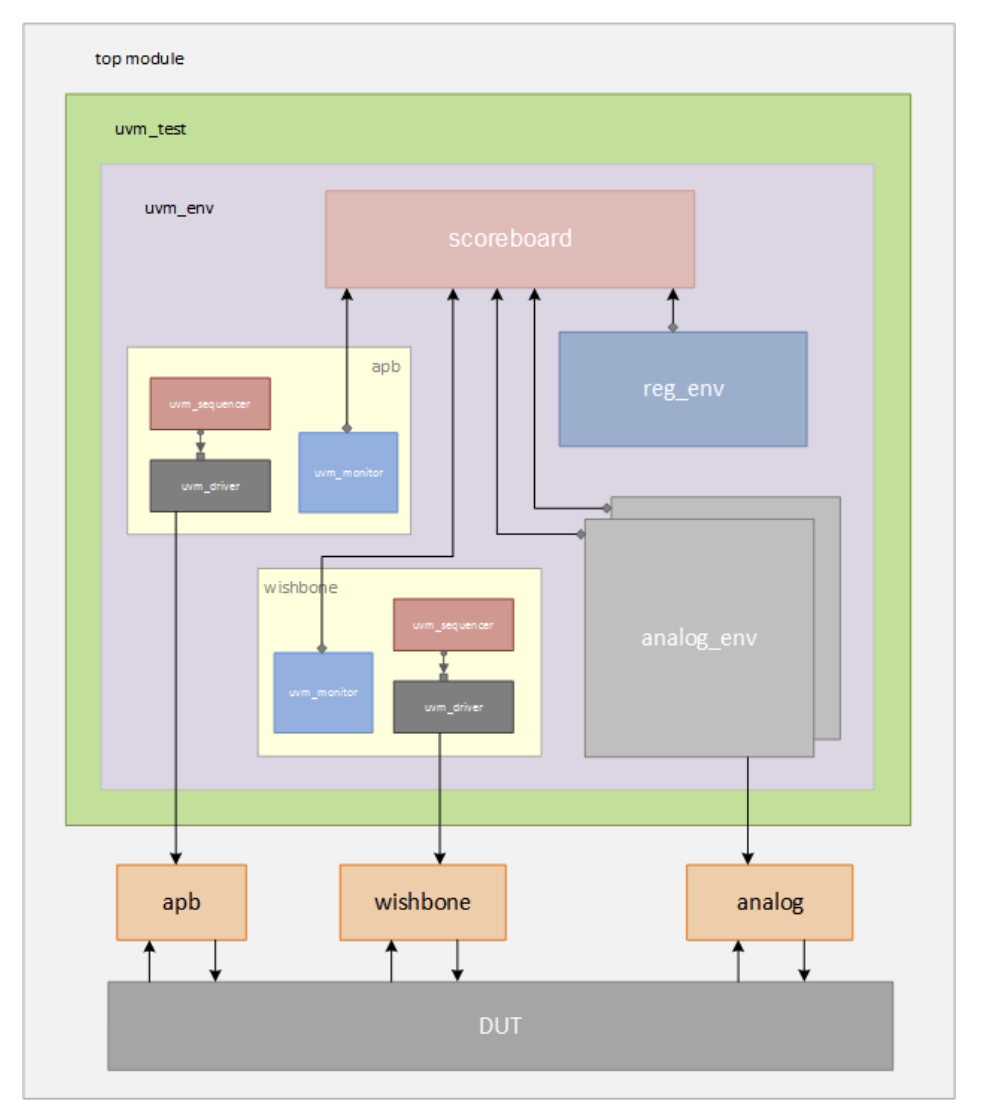

2.4.1 在验证平台中加入sequencer

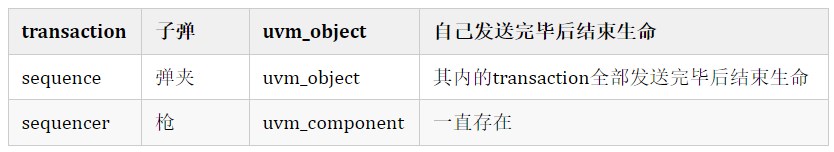

sequence机制作用:用于产生激励。其分为两部分,一是sequence,二是sequencer。

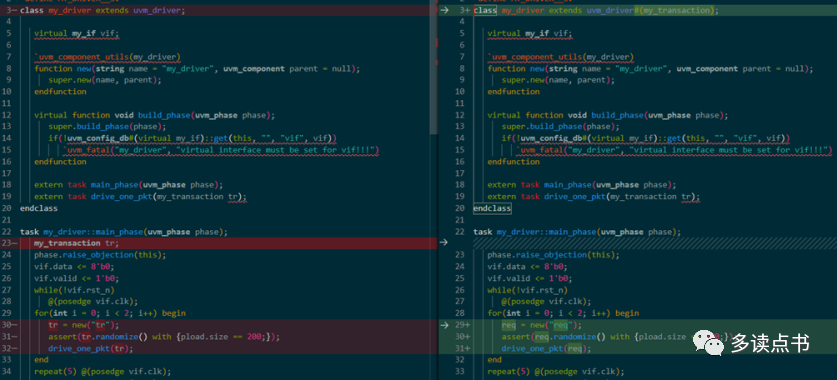

在定义driver时指明此driver要驱动的transaction的类型,这样定义的好处是可以直接使用uvm_driver中的某些 预先定义好的成员变量 ,如uvm_driver中有成员变量 req ,它的类型就是传递给uvm_driver的参数。由此带来的变化如下:(不需要定义中间变量tr了)

2.4.2 sequence机制

三者关系:

每一个sequence都有一个body任务,当一个sequence启动之后,会自动执行body中的代码。body中uvm_do这个宏的作用如下:

- 创建一个my_transaction的实例m_trans;

- 将其随机化;

- 最终将其送给sequencer。

如果不使用uvm_do宏,也可以直接使用start_item与finish_item的方式产生transaction。

sequencer负责协调sequence和driver的请求

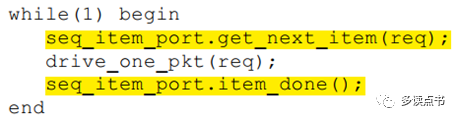

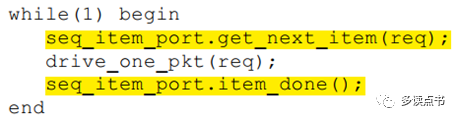

- sequencer和driver之间

- 将两者连接:drv.seq_item_port.connect(sqr.seq_item_export);

- 在driver中通过get_next_item任务来得到一个新的req,并且驱动它,驱动完成后调用item_done通知sequencer(完成握手)。

- sequencer和sequence之间:

- sequence中的uvm_do宏发送transaction后,会一直等待,直到driver返回item_done信号。

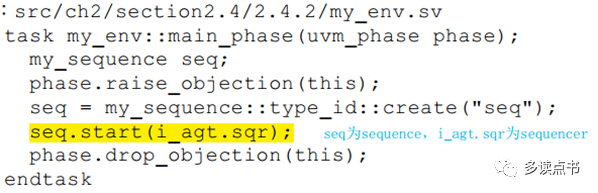

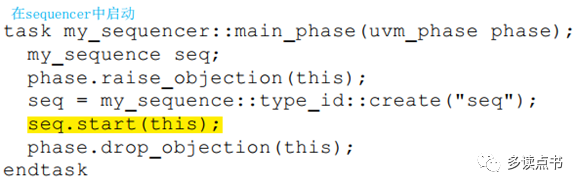

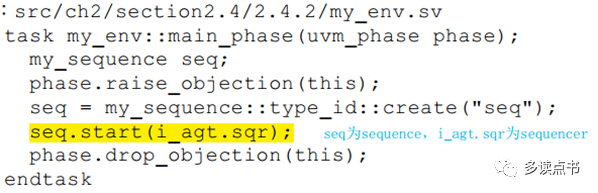

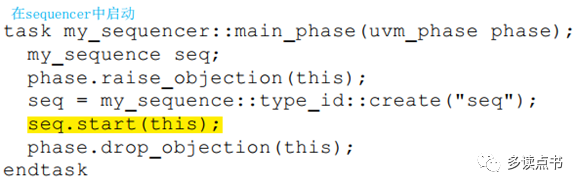

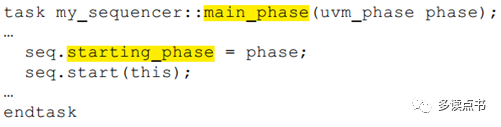

- 在某个component(如my_sequencer、 my_env)的main_phase中启动这个sequence,即可让sequence向sequencer发送transaction。

get_next_item和try_next_item的比较

- get_next_item是阻塞的,它会一直等到有新的transaction才会返回;

- try_next_item则是非阻塞的,它尝试着询问sequencer是否有新的transaction,如果有,则得到此transaction,否则就直接返回。其行为更加接近真实driver的行为

2.4.3 default_sequence的使用

引入default_sequence的原因:

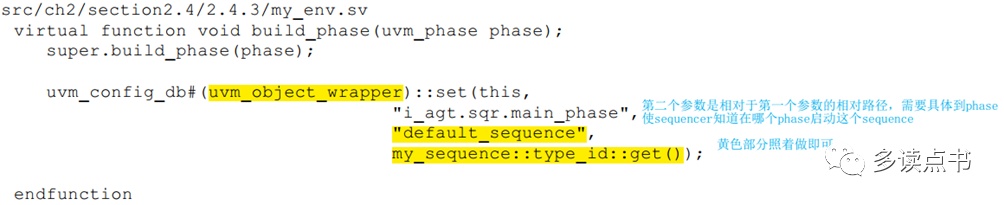

- 在某个component的build_phase阶段使用config_db与default sequence替代了在某个component的main_phase阶段利用seq.start(i_agt.sqr)启动sequence,将objection与sequence完全联系起来,增加了可移植性。

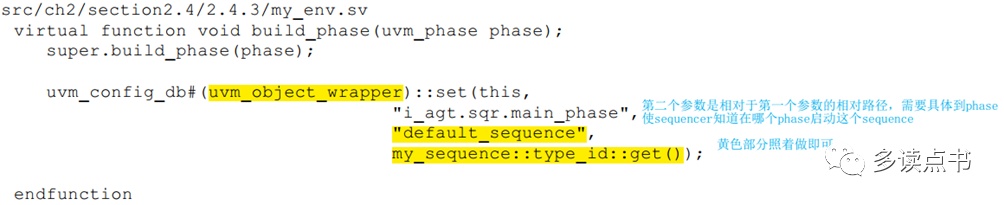

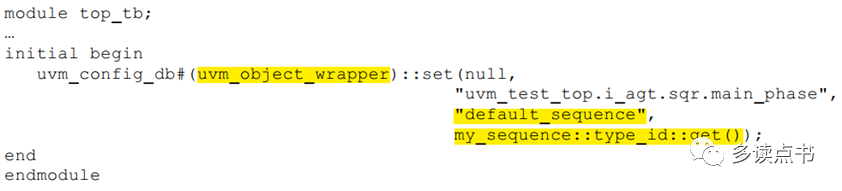

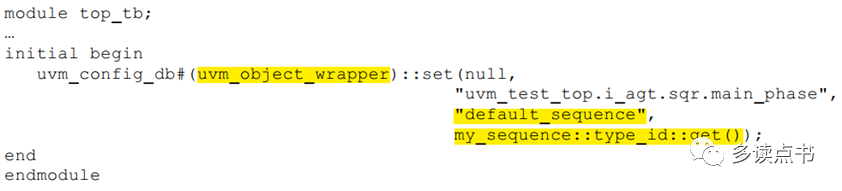

如何使用default_sequence:

- 方法一:在某个component(如my_env)的build_phase中设置如下代码

- 方法二:在top_tb中设置

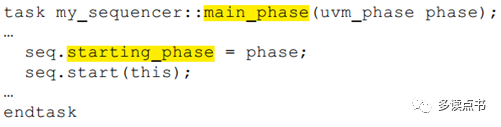

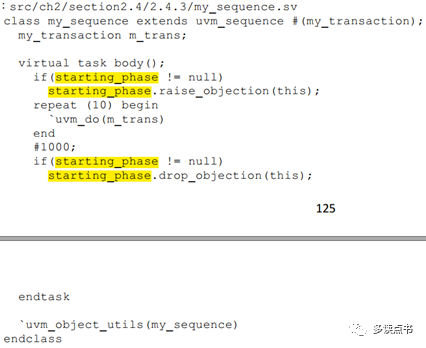

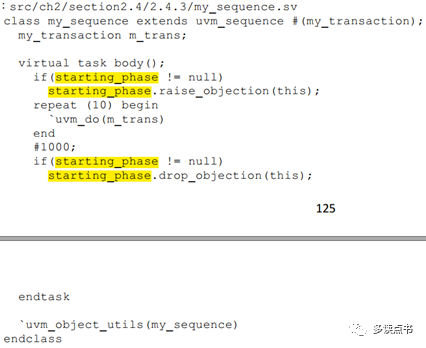

使用default_sequence时 如何提起和撤销objection ?

- 因为在sequencer在启动default_sequence时,uvm_sequence的内置变量starting_phase会自动执行如下内容:

- 所以可以在sequence中使用借助starting_phase来提起和撤销objection。

2.5 建造测试用例

2.5.1 加入base_test

对my_env进一步封装,添加一些公司个性化内容,举例如下:

- 在report_phase中根据UVM_ERROR的数量来打印不同的信息。它在main_phase结束之后执行。

- 设置整个验证平台的超时退出时间

- 通过config_db设置验证平台中某些参数的值

2.5.2 UVM中测试用例的启动

通过传递参数变量值启动的原因:

- 保证后加的测试用例不影响已经建好的测试用例

如何使用:

- 定义不同的base_test,让run_test()使用缺省模式,然后通过在命令中传递参数变量来实现一次编译执行多个用例,如下:

- +UVM_TEST_NAME=my_case0

-

UVM

+关注

关注

0文章

181浏览量

19167 -

sequence

+关注

关注

0文章

23浏览量

2840

发布评论请先 登录

相关推荐

新手学习System Verilog & UVM指南

IC验证"为什么要学习UVM呢"

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...

什么是uvm?uvm的特点有哪些呢

谈谈UVM中的uvm_info打印

谈UVM之sequence/item见解 sequencer特性及应用(下)

Modelsim uvm库编译及执行

开关电源学习笔记 --- 目录

什么是UVM environment?

UVM中uvm_config_db机制背后的大功臣

UVM中uvm_config_db机制背后的大功臣

一文详解UVM设计模式

UVM学习笔记(三)

UVM学习笔记(三)

评论