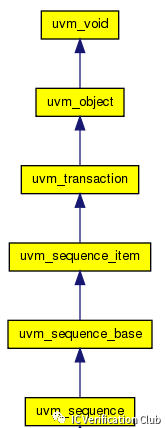

引入sequence的原因:

- 将 生成测试case的语句 从 main_phase 中独立出来,使得使用不同测试用例时,只需要修改sequence部分即可,而不用关注 UVM剩余部分。(提高剩余部分的可复用性)。

引入sequence的仲裁机制的原因:

- 一个sequencer上通过fork...join可以启动多个sequence,而多个sequence按照什么顺序启动需要一定的仲裁机制来控制,具体而言主要从两个角度控制

- sequence角度:自身的优先级、原子性、有效性

- sequencer角度:对多个sequence的仲裁算法

引入sequence相关宏的原因:

- 更方便地控制transaction的产生过程,主要有:

- uvm_do系列宏:实例化transaction+将transaction交给sequencer(对应start_item与finish_item任务)

- uvm_create宏:实例化transaction,可用new代替

- uvm_send宏:将transaction交给sequencer(对应start_item与finish_item任务)

- uvm_rand_send系列宏:对transaction进行随机化+将transaction交给sequencer(对应start_item与finish_item任务)

不同类型sequence共用sequencer的方法(一个driver):

- transaction类型例化的一个sequencer 对应 多个不同约束的transaction包

- 可以通过一个sequence启动其他sequence(即嵌套的sequence),然后间接生成多个不同约束的transaction包 —— 注意:这里使用了cseq. start ( m_sequencer );这样的语句

- 也可以通过一个sequence直接生成多个不同约束的transaction包

- 通过类型转换,实现同一个sequencer处理不同两个截然不同的transaction,步骤如下

- 将sequencer和driver能够接受的数据类型设置为uvm_sequence_item

- driver中使用时,使用cast将uvm_sequence_item转换为各自transaction的类型

补充:start任务参数说明 seq0.start(env.i_agt.sqr, null, 100);

- 第一个参数:sequencer的位置,指明seq0由哪个sequencer启动

- 第二个参数:parent sequence

- 第三个参数:seq0的优先级

补充:m_sequencer是一个属于每个sequence的成员变量,它指向执行当前sequence的sequencer句柄,其类型是uvm_sequencer_base。

sequencer向sequence传递变量(约束)的方法:

- 方法一:通过cast转换将sequence内置变量m_sequencer(类型为uvm_sequencer_base)转换成my_sequencer类型, 然后引用uvm_sequencer中的成员变量作为约束

- 方法二:在sequence中使用`uvm_declare_p_sequencer(my_sequencer),然后通过宏默认生成的变量p_sequencer来引用uvm_sequencer中的成员变量作为约束

补充:uvm_declare_p_sequence的实质是在base_sequence中声明了一个成员变量p_sequencer,并将其指向启动本sequence的sequencer。

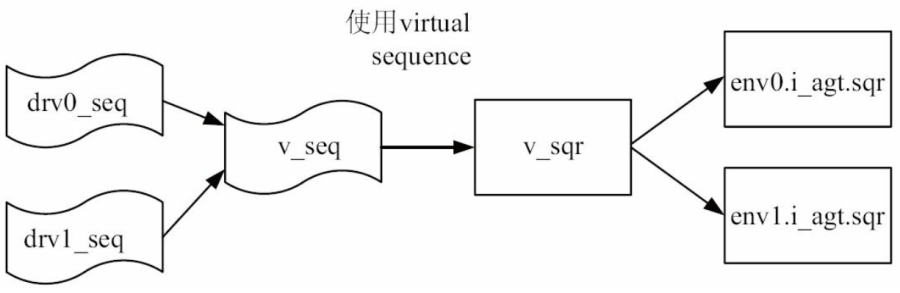

发往不同driver的sequence之间的同步的方法:

- 方法一:通过全局事件进行简单同步:在drv0_seq中触发事件,在drv1_seq中等待这个全局事件。

- 方法二:使用 virtual sequence+virtual sequencer,可以实现类似crossbar的连接,且因为virtual sequence的body是顺序执行,所以可以轻松实现整体顺序(同步),局部并行的效果。

补充:verilog中事件的基本使用

- event变量声明为:

- event var;

- event触发为:

- ->var;

- 捕获触发为:

- @(var);

sequence library的概念:

- 派生自uvm_sequence,就是一系列sequence的集合,它会根据特定的算法随机选择注册在其中的一些sequence, 并在body中执行这些sequence。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

UVM

+关注

关注

0文章

182浏览量

19195 -

sequence

+关注

关注

0文章

23浏览量

2852

发布评论请先 登录

相关推荐

数字IC验证之“搭建一个可以运行的uvm测试平台”(5)连载中...

的transaction,以及创建用于产生事物的事物发生器sequence。 在uvm验证平台中穿梭各个组件之间的基本信息单元是一个被称为transaction的数据对象,也就是我们前面所说的事物

发表于 01-26 10:05

UVM sequence分层有哪几种方式呢

种请求下可以使用第一种分层方式,在high-layer sequence中依然使用low-layer sequencer进行驱动,同时对low-layer sequence进行更加精细化的控制

发表于 04-11 16:37

请问一下在UVM中的UVMsequences是什么意思啊

在UVM方法学中,UVMsequences 是寿命有限的对象。UVM sequences从uvm_sequence_item基类扩展得到,uvm_s

发表于 04-11 16:43

UVM sequence分层的几种体现

种请求下可以使用第一种分层方式,在high-layer sequence中依然使用low-layer sequencer进行驱动,同时对low-layer sequence进行更加精细化的控制。在上面

发表于 04-14 11:08

如何配置sequence的仲裁算法和优先级及中断sequence的执行

01 Arbitrary在UVM中,多个sequence可以同时被绑定到相同的sequencer并启动。这种测试场景在实际中是存在的,比如在模拟同一个总线master口上的不同类型的数

发表于 09-23 14:35

sequence item实际应用中应该包含哪些东西

展开。Sequence item是游走在Sequence-Sequencer-Driver这一基本结构中的数据结构类型,在有些地方也直接叫transaction,可以说是UVM的必用品

发表于 09-23 14:42

UVM中seq.start()和default_sequence执行顺序

1. 问题 假如用以下两种方式启动sequence,方法1用sequence的start()方法启动seq1,方法2用UVM的default_sequence机制启动seq2。那

发表于 04-04 17:15

浅谈UVM之sequence/item见解(上)

item指的是uvm_sequence_item, Sequence Item具备UVM核心基类所必要的数据操作方法,对于激励的生成和场景控制,是由sequence来编织的,item应

UVM sequence机制中response的简单使用

sequence作为UVM几个核心机制之一,它有效地将transaction的产生从driver中剥离出来,并且通过和sequencer相互配合,成功地将driver的负担降低至仅聚焦于根据协议将

UVM中add_typewide_sequence和add_sequence的区别

第2和第3种方式类似,第3种是一下子添加多个sequence,它内部原理就是调用第2种的函数,因此在本质上,只有第1和第2种这两类区别。

在Sequencer上启动一个Sequence

Sequencer默认不执行任何Sequence。验证工程师可以通过调用start()启动一个Sequence,也可以通过uvm_config_db指定一个自动启动的Sequence。

UVM中sequence的那些事儿

UVM中sequence的那些事儿

评论