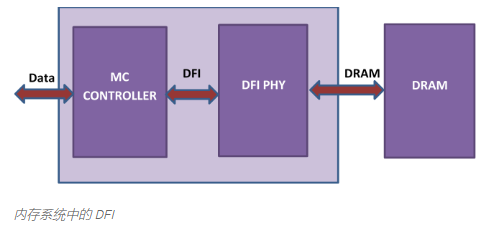

DDR PHY 接口 (DFI) 用于包括智能手机在内的多种消费电子设备。DFI 是一种接口协议,用于定义在 DRAM 设备之间以及 MC(微控制器)和 PHY 之间传输控制信息和数据所需的信号、时序和可编程参数。DFI 适用于所有 DRAM 协议,包括 DDR4、DDR3、DDR2、DDR、LPDDR4、LPDDR3、LPDDR2 和 LPDDR。

为什么需要DFI?

当 MC 和 PHY 专门开发用于协同工作时,不需要 DFI 接口。然而,在许多情况下,MC 和 PHY 是分开设计的——通常由不同的公司设计。DFI允许公司开发MC和PHY IP设计,因为他们知道他们将能够与其他公司开发的设备进行互操作。

此外,MC器件主要基于时钟,而PHY通常由大量的模拟逻辑组成,因此这两个器件通常由不同的工程师开发,甚至在同一家公司内。DFI 为两个独立的设计团队创建了一个定义明确的界面。

内存系统中的 DFI

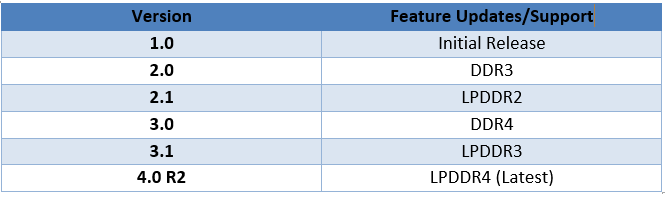

最新的 DFI 规范版本是 4.0,修订版 2。多年来,该规范经历了几次重大增强,如下表所示:

DFI协议的显著特点

不同的频率比 – DFI 接口支持 1:1、1:2 和 1:4 MC 与 PHY 时钟频率比,可实现快速 PHY 内存访问。DFI 规范定义了 MC 和 PHY 之间的频率变化协议,以允许设备更改内存控制器和 PHY 的时钟频率,而无需完全重新设置系统。

对 MC 或 PHY 没有限制 – DFI 协议并不包含 MC 或 PHY 的所有功能,该协议也不对 MC 或 PHY 如何与系统的其他方面接口施加任何限制。

数据总线反转 – DBI可用于减少总线上的转换次数和/或降低总线上的噪声和功耗。

DFI 读写训练操作可以提高 DDR4、DDR3、LPDDR4、LPDDR3 和 LPDDR2 系统中更高速度的信号放置精度。

低功耗模式 – 如果 PHY 知道 DFI 将空闲一段时间,则 PHY 可能能够进入 MC 启动的低功耗状态。

审核编辑:郭婷

-

微控制器

+关注

关注

48文章

7646浏览量

151980 -

接口

+关注

关注

33文章

8691浏览量

151792 -

DDR

+关注

关注

11文章

715浏览量

65482

发布评论请先 登录

相关推荐

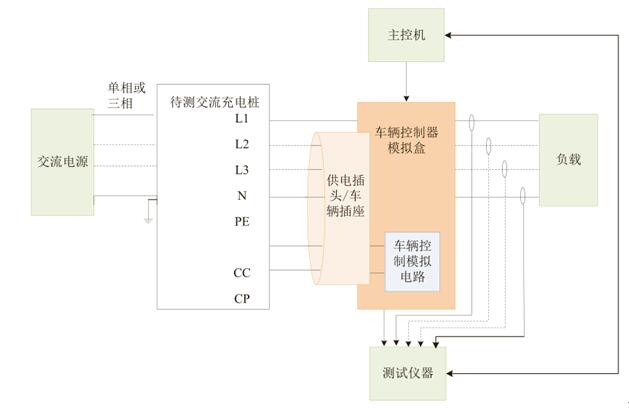

浅析交流充电桩的互操作性测试标准

10-Gbps以太网MAC和XAUI PHY互操作性硬件演示参考设计(PDF)中的说明进行操作

基于XML的现场总线设备互操作性研究

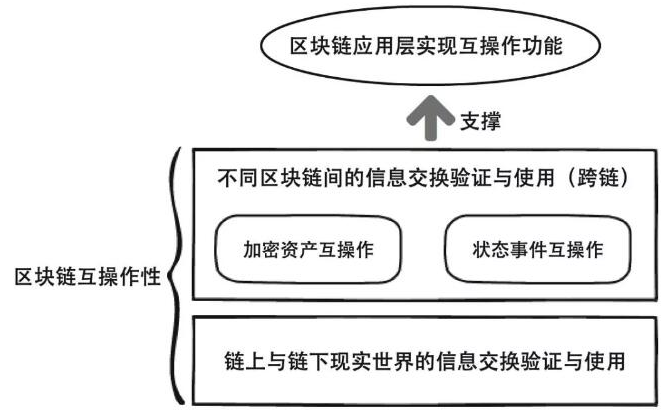

区块链为什么要追求互操作性?

区块链互操作性的三个类别

区块链互操作性是什么

使用DFI的DDR-PHY互操作性

使用DFI的DDR-PHY互操作性

评论