在Zynq开发中有一个很常用的功能是将ARM端的数据导出到本地,然后通过Matlab,Python等工具对数据进行分析。

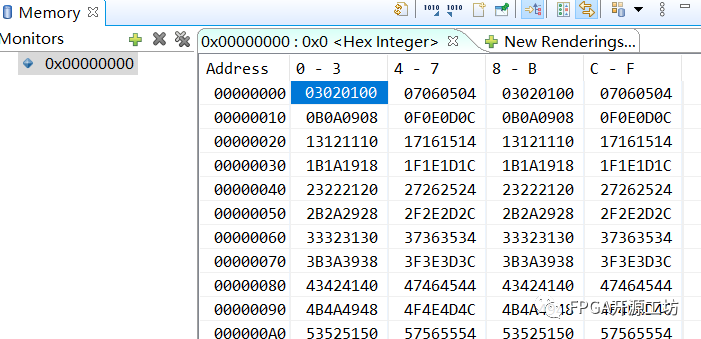

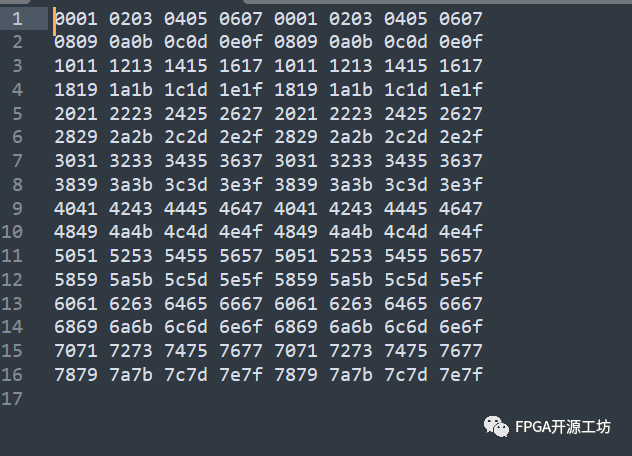

可以在Vitis的Memory窗口中观察到Zynq内存中的数据,如下图:

如果仅仅是观察几个数据的值,在这个窗口里面操作也足够了,但是往往是需要将这些导出来进行分析的。可以通过外置的接口比如串口,网口等方式将内存中的数据传到本地,但是这些方式都需要上位机的配合。

在Vitis中提供了mrd的命令来帮助我们将这些数据导出来。

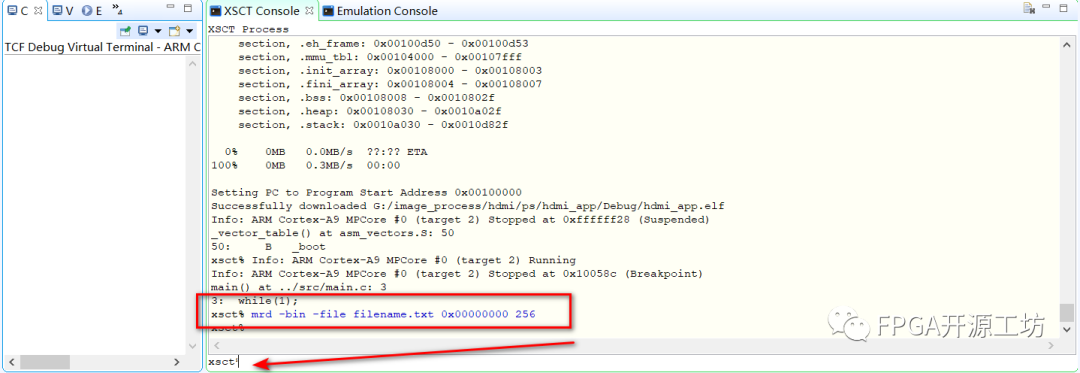

基本的使用方式如下,filename.txt是指保存的文件名,0x00000000指的是起始地址,256是指保存的大小,这个大小不一定是字节,这个需要注意。

mrd -bin -file filename.txt 0x00000000 256

我们在xsct console中输入上面的命令

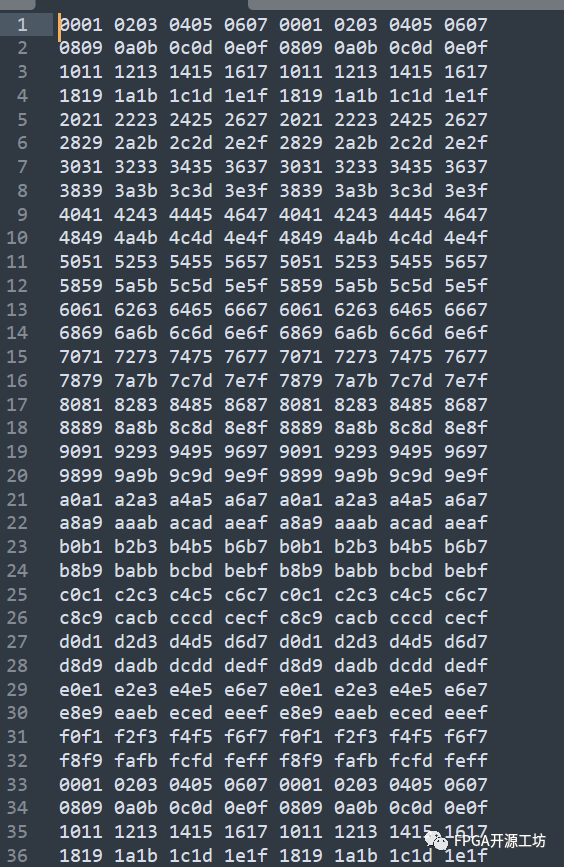

保存出来的文件如下所示,可以看到的确是从00000000地址起始的数据,可以和上面Memory窗口中的数据对应上。

因为每个数据都是8bit的,所以00 01 02 03这四个数据就是4个字节,那么下图中一行就是16个字节,而整个文件一共有64行(篇幅有限,所以没有全部截下来),也就是1024个字节,而在命令中只输入了256作为保存的大小,这又是为什么呢。

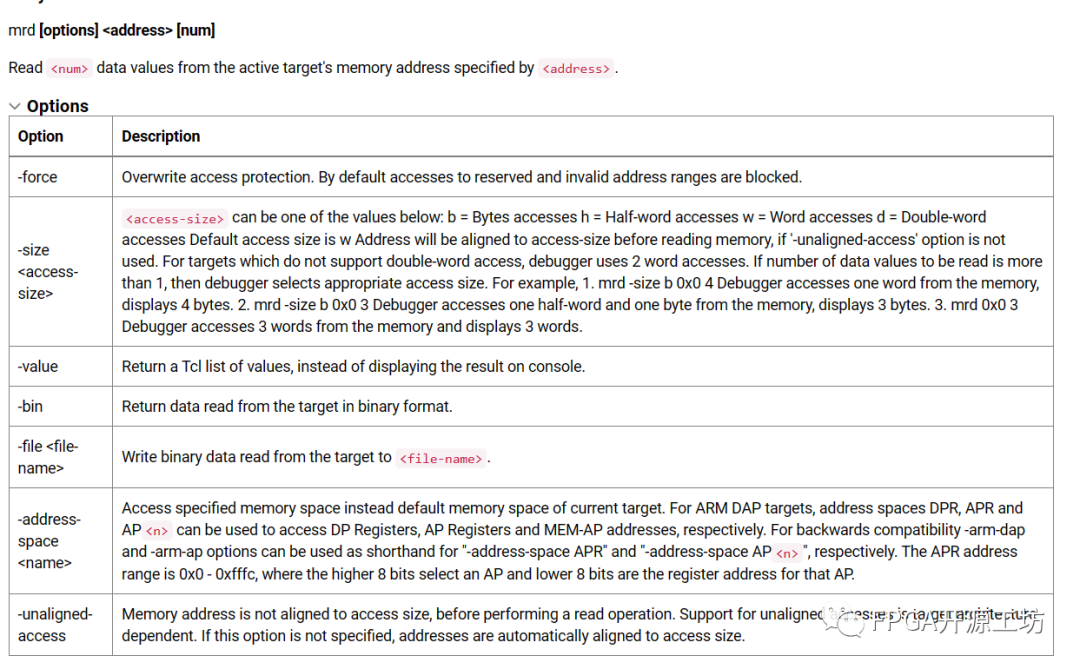

通过查看xilinx提供的手册可以看到mrd还有一些其他的参数来控制保存数据的大小。

可以看到第二个选项-size,里面提供了-b也就是按字节(8 bit)大小来保存,-h按半字(16 bit)来保存,-w是按字(32 bit)来保存,-d(64 bit)是按双字来保存,在默认情况下就按字来保存的。

因为ZYNQ是32bit处理器,所以半字,字,双字的位宽是括号里面的值。

那么就可以解释为啥我们给定的大小是256,而保存的文件有1024个字节了,1024=256*4(byte)。

所以我们可以通过指定-size这个选项来控制按哪种方式来保存数据的大小。

比如输入下面这句命令

mrd-bin-sizeb-filefilename.txt0x00000000256

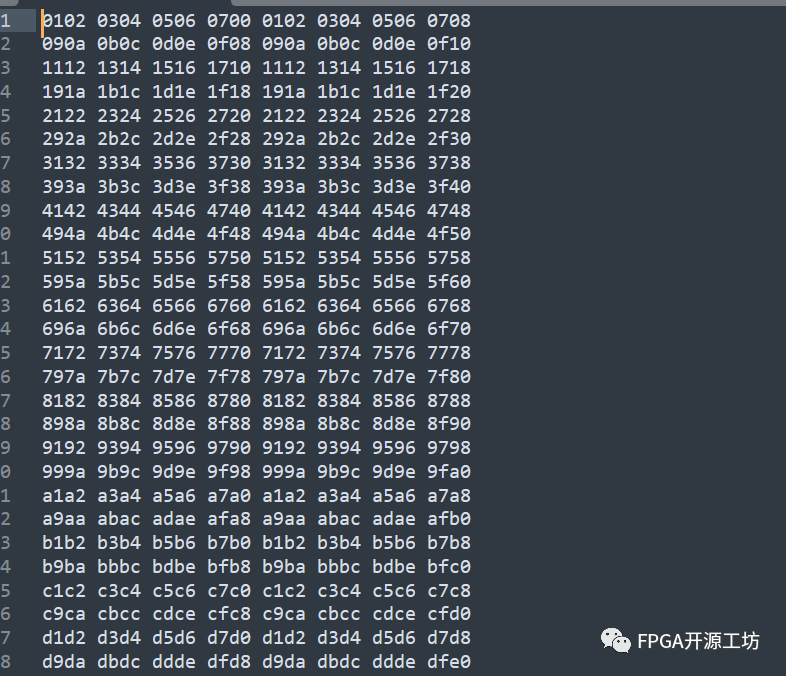

保存下来的数据如下图所示:这次就真的是256个字节了,一行是16个字节,一共16行

另外手册上还有一个-unaligned-access的选项,这个选项是为了让我们保存数据的时候可以从非对齐地址开始保存。对于32位地址空间来说就是按4字节对齐的,也就是如果不知道-unaligned-access的选项我们在获取数据的时候起始地址必须以0,4,8等4的倍数开始的地址,如果你强行指定一共0x00000001这样的非对齐地址,他保存数据的时候也是从0x00000000开始的。

mrd -bin -file filename.txt 0x00000001 256 mrd -bin -file filename.txt 0x00000000 256

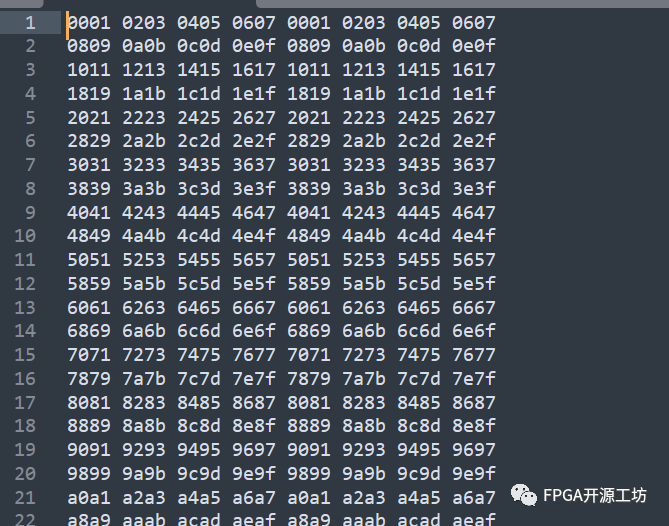

比如上面两句命令,他保存出来的结果是一样的,注意值是从0开始的,如下所示:

当我们指定非对齐之后,获取到的数据就是从01开始的,也就是从地址00000001获取到的数据

mrd -bin -unaligned-access -file filename.txt 0x00000001 256

需要注意的是,这里的对齐并不是和多少位总线,或者操作系统是多少位的有关,而是和之前我们指定的-size这个选项有关,在默认情况下是按-w也就是字来对齐的,也就是按32bit对齐。在-b下就是按8bit对齐,在这种情况下也就没有对不对齐的概念了,因为8bit对齐就是按0,1,2,3,4等等这样的自然序对齐的。所以-d是按64bit对齐,-h是按16bit对齐。

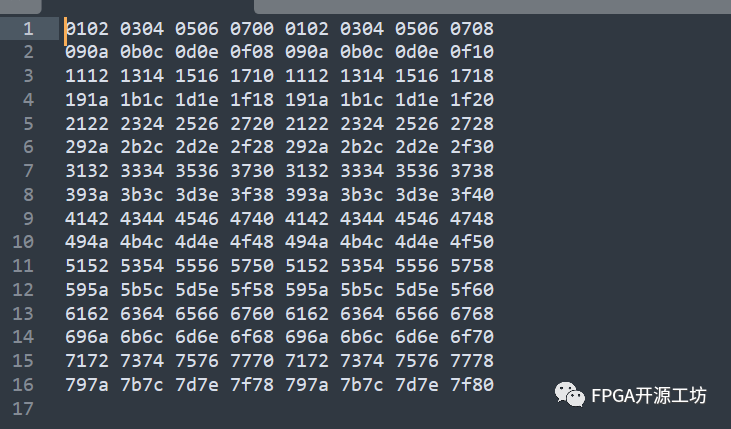

比如下面这句话没有指定非对齐获取,他也能从地址1开始取数,因为他本身就是对齐的。

mrd -bin -size b -file filename.txt 0x00000001 256

上面这个小技巧是经常使用的哦,比如在FPGA中处理完一组数据后想分析一下处理的对不对就可以把数据通过这种方式取出来,然后使用Matlab python等工具进行处理。例如在FPGA中做了一个Sobel的边缘检测,就可以把处理完的数据拿出来,用Matlab、Python等工具把处理结果恢复成图像,或者直接和参考模型进行比对。

审核编辑:刘清

-

FPGA

+关注

关注

1635文章

21837浏览量

608328 -

ARM处理器

+关注

关注

6文章

361浏览量

42071 -

上位机

+关注

关注

27文章

948浏览量

55182 -

python

+关注

关注

56文章

4813浏览量

85301

原文标题:Vitis调试技巧--从Vitis中导出数据到本地

文章出处:【微信号:FPGA开源工坊,微信公众号:FPGA开源工坊】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Vitis里如何创建嵌入式软件工程

如何把赛灵思SDK工程移植到Vitis

Vitis2023.2使用之—— classic Vitis IDE

Vitis2023.2使用之—— updata to Vitis Unified IDE

Vivado硬件平台更新后Vitis工程如何更新

Vitis的使用教程

使用Vitis HLS创建属于自己的IP相关资料分享

【KV260视觉入门套件试用体验】五、VITis AI (人脸检测和人体检测)

Vitis初探—1.将设计从SDSoC/Vivado HLS迁移到Vitis上

HLS导出的.xo文件如何导入到Vitis里面

基于Vitis HLS的加速图像处理

在Vitis中调试ARM可信固件和U-boot

Vitis调试技巧-从Vitis中导出数据到本地

Vitis调试技巧-从Vitis中导出数据到本地

评论