用于片上系统 (SoC) 中功能块连接和管理的 ARM® AMBA4® 规范现在具有支持多核计算的高级可扩展接口 (AXI) ™ 一致性扩展 (ACE ™)。ACE 规范支持跨多核处理器群集的系统级缓存一致性。在规划此类系统的功能验证时,这些一致性扩展带来了自己的复杂挑战,例如系统级缓存一致性验证和缓存状态转换验证。在任何给定时间,验证 ACE 互连是否可以在系统中的不同 ACE 主节点之间保持缓存一致性非常重要。随着硬件中的一致性支持以及相关的支持协议,系统和底层组件的复杂性大大增加。因此,这种系统的核查面临若干挑战。让我们掌握对激励生成基础设施的要求,以验证缓存一致性系统。

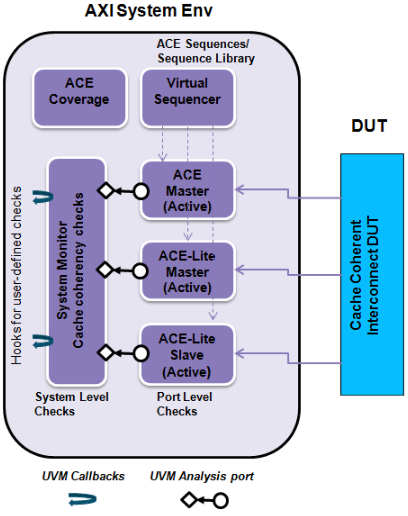

基于 AMBA ACE 互连的系统可以通过相干互连连接各种主站和从站。每个主组件和从组件都可以单独支持完整的 ACE、ACE-Lite™、AXI4™ 或 AXI3™ 协议,并且可以使用不同的总线宽度或时钟频率。不同的排列涉及以下参数:缓存状态、事务类型、突发长度和大小、侦听机制、侦听缓存状态、侦听响应、对推理获取的支持、对侦听过滤的支持以及用户指定的互连调度。

所有这些交叉组合导致了非常大的验证空间,从而产生了四个关键挑战:

生成映射到所有这些的激励包括,确保每个单独的主、从或互连与其支持的协议完全兼容;

确保启动主存储器、侦听主存储器和从主存储器之间所有可能的并发访问组合都经过验证,并符合ACE规范;

确保涵盖所有用户特定的功能并按预期工作;和

确保核查的完整性

您如何创建一个可以处理所有这些的刺激发电基础设施?

在这里,我们尝试向您展示如何做到这一点?这个想法是确保您拥有所有正确的构建块,并逐步组织它们并将它们拼接在一起以获得您需要的东西。

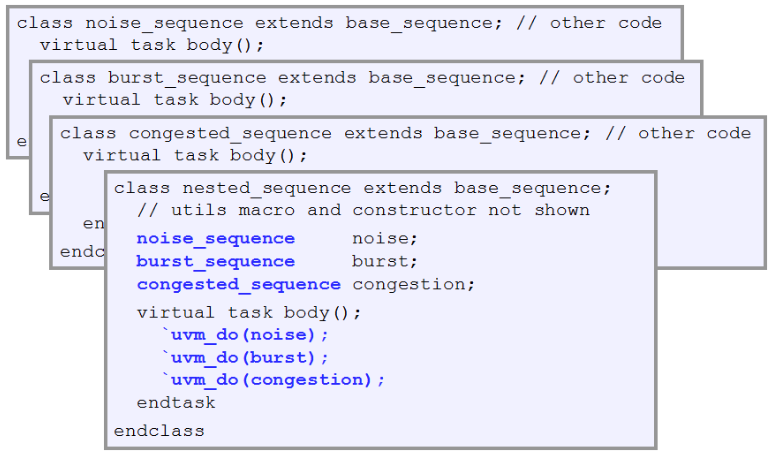

我们在VC验证IP(VIP)中所做的非常相似:我们从一些久经考验的原生SystemVerilog UVM原子序列开始,并逐步转向创建复杂的序列。鉴于 UVM 提供的功能,将低级、经过验证或验证的方案拼接在一起以创建更复杂的方案要方便得多。无需在序列主体中创建扁平化实现,可以创建分层或嵌套序列以利用之前创建的基本序列。这可以上升到多个层次结构级别,因此可以收敛以满足最复杂方案的要求。

随着多个 ACE 组件的复杂性增加,可能需要跨多个序列器和驱动程序协调序列。这些都是通过虚拟序列和序列器实现的。从刺激生成的角度来看,另一个重要功能是序列的分组和分层序列的创建。在UVM中,相似的序列可以组合到一个序列库中。使用 UVM 基类,您可以创建库基础结构,该基础结构允许通过库 API 将任何序列注册到序列库。在仿真中选取库后,默认功能会导致选取并执行随机数量的序列。因此,AXI VIP附带的序列库可以用作满足用户要求的起点。

可以通过更改关联配置类的参数来修改序列库的默认模式。因此,可以拾取特定数量的序列,启用随机循环序列,以及编程用户定义的序列执行。

为序列库创建自定义规则不仅有助于简化不同仿真中的多个序列,还有助于避免冗余,并逐步实现所有有趣的系统级场景的融合。因此,无需编写多个测试,我就可以通过虚拟序列器跨多个序列库、跨不同接口创建自定义序列执行,从而生成激励管理设置,有助于更快地满足所有激励生成要求。在某些情况下,序列必须知道功能配置,以便根据系统级要求进行重新配置。VC VIP 利用 UVM 资源机制提供的大部分功能,在 ACE 环境中提供可配置性和复杂的激励生成要求。通过资源机制启用的可配置性本身就是一个非常有趣的话题,我可以在后续文章中讨论它。

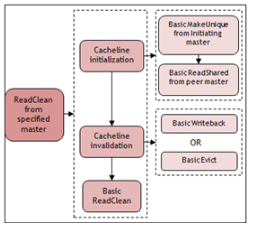

在这里,我有一个示例,展示了如何使用序列集合创建自定义序列生成要求。让我们以需要验证与 Readclean 事务关联的所有缓存行状态的情况为例。(“ReadClean 是一个读取事务,用于可与其他主节点共享的内存区域。保证 ReadClean 事务不会将更新主内存的责任传递给启动主服务器。通常,ReadClean 事务由想要获取缓存行的干净副本的主节点使用,例如具有直写缓存的主节点。那么,您如何发起此类交易?

ReadClean 事务需要缓存行初始化,然后是缓存行失效,然后是基本的 Readclean。让我们看看你有什么作为构建块。首先,采用“缓存行初始化”序列,该序列将主缓存及其对等方缓存的缓存行状态初始化为一组随机但有效的状态。这可确保验证由主服务器启动的一致事务的所有不同缓存行状态转换。这将需要一个序列,该序列将写入启动主服务器本地缓存。数据现在在本地缓存中是脏的。随后,另一个主节点启动“写入”内存。现在,本地缓存中的数据是干净的,缓存中的数据与内存中的数据匹配。接下来是“BasicReadShared”,它将通过从启动主服务器获取干净的数据将数据读入每个主服务器的本地缓存中。然后,您将需要一个使主节点的缓存行无效的序列。这将是缓存行失效序列。 对于非推理负载事务,可能需要这样做。最后,你需要有一个基本的 Readclean 序列:

可以使用嵌套序列和虚拟序列模拟完整的验证场景。使用分层方法,无论任何场景生成需求有多复杂,对任何场景生成需求进行建模都变得相对容易。这种方法与虚拟序列结合使用时有助于跨多个接口利用此功能,并且在系统上下文中高度相关,如上所示。因此,作为库一部分的多个虚拟序列可以执行从不同主站到同一从站或不同从站的不同顺序相干事务的组合。

随着协议复杂性的不断增加和发展,验证协议所需的基础设施也需要在复杂性上扩大规模。UVM等高级方法一直在不断发展,以满足许多复杂的要求。验证基本缓存一致性系统本身就具有挑战性。ACE 协议带来的额外复杂性对所使用的验证方法提出了很高的要求。UVM 库提供的序列生成、分布式相位和配置管理以及最新更新(可通过 UVM-1.2 库获得)的功能可以使 VIP 实施利用这些功能来满足不同系统中的验证要求。

审核编辑:郭婷

-

服务器

+关注

关注

12文章

9021浏览量

85183 -

总线

+关注

关注

10文章

2867浏览量

87988 -

AMBA

+关注

关注

0文章

68浏览量

14951

发布评论请先 登录

相关推荐

ARM系列之ACE协议资料汇总

AMBA CHI协议介绍

AMBA-PV TLM扩展用户指南

AMBA 3 AXI协议检查器用户指南

AMBA 4 ACE和ACE Lite协议校验器用户指南

PCIe AMBA集成指南

AMBA静态内存接口数据表

未来的物联网将物理世界中的所有内容都连接到互联网

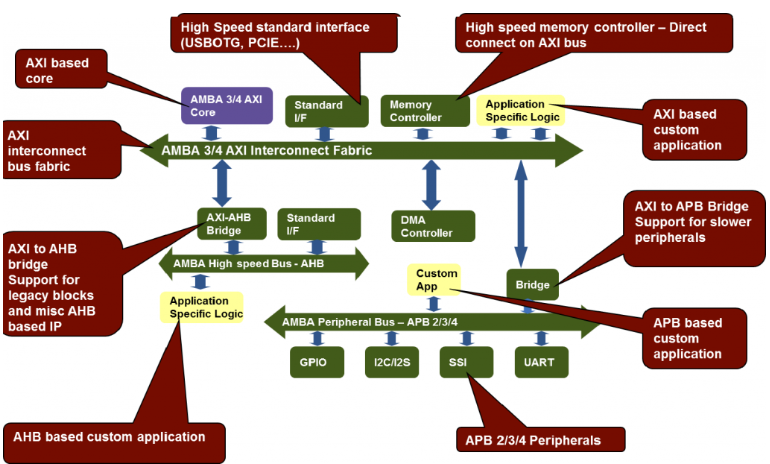

基于AMBA总线介绍

将您的Magicbit(ESP32)连接到thingsboard

Arm AMBA ACE5-Lite协议规范更新

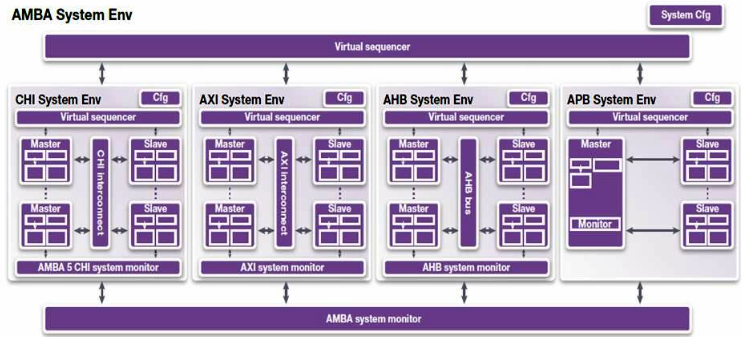

如何验证AMBA系统级环境

基于AMBA的子系统:验证它们需要什么

AMBA:将所有内容拼接到ACE您的测试

AMBA:将所有内容拼接到ACE您的测试

评论