7系列设备在ILOGIC块中具有专用寄存器,用于实现输入双倍数据速率(DDR)寄存器。此功能用于实例化IDDR基元。

输入I/O tile的所有时钟都是完全多路复用的,即在ILOGIC和OLOGIC区块之间没有时钟共享。IDDR原语支持以下操作模式:

•OPPOSITIE_EDGE模式

•SAME_EDGE模式

•SAME_EDGE_PIPELINED模式

SAME_EDGE和SAME_EDGE_PIPELINED模式与Virtex-6相同。这些模式允许设计者通过ILOGIC块中的域将下降沿数据传输到上升沿,这样可以节省CLB和时钟资源并增加性能。这些模式是使用DDR_CLK_EDGE属性实现的。以下各节详细介绍了每种模式。

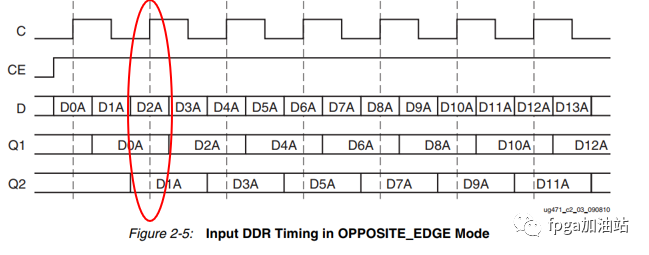

一、OPPOSITIE_EDGE模式

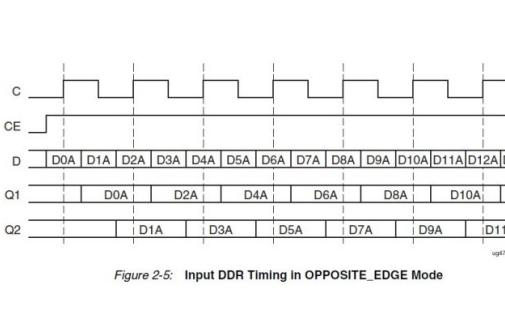

传统的输入DDR解决方案或OPPOSITIE_EDGE模式是通过单个ILOGIC块中的输入来实现的。数据在时钟的上升沿通过引脚Q1输出给FPGA逻辑,在时钟的下降沿通过Q2输出给FPGA逻辑。这结构类似于Virtex-6的FPGA实现。图2-5显示了使用OPPOSITIE_EDGE模式的输入DDR时序图。

二、SAME_EDGE模式

在SAME_EDGE模式中,数据在同一时钟沿上呈现到FPGA逻辑中。这种结构类似于Virtex-6的FPGA实现。

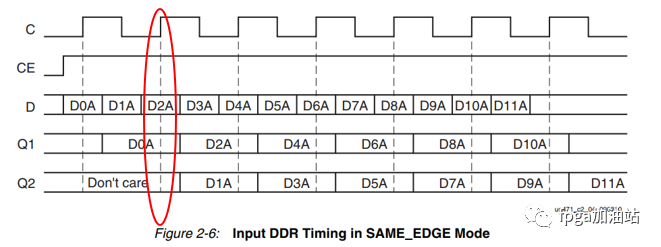

图2-6显示了使用SAME_EDGE模式的输入DDR的时序图。可以看到,从Q1和Q2引脚输出的第一对数据不再是Q1(D0A)和Q2(D1A)。相反,第一对呈现的是Q1(D0A)和Q2(Don’t care),紧接着的下一对数据是Q1(D2A)和Q2(D1A)。

三、SAME_EDGE_PIPELINED模式

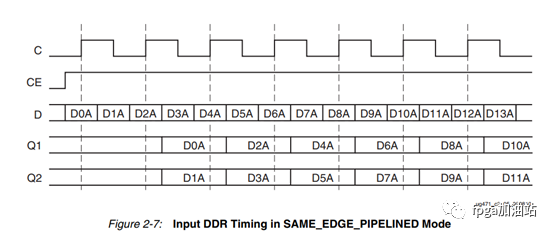

在SAME_EDGE_PIPELINED模式中,数据在同一时钟沿上呈现到FPGA逻辑中。与SAME_EDGE模式不同,数据对不被一个时钟周期分隔。然而需要额外的时钟延迟来消除SAME_EDGE模式的分离效应。图2-7显示了使用SAME_EDGE_PIPELINED模式的输入DDR的时序图。输出对Q1和Q2被同时提供给FPGA逻辑。

总结

| OPPOSITIE_EDGE模式 | 在该模式下,上升沿采样到的数据(如D0A)和下降沿采样到的数据(如D1A),可以在下一个时钟周期的上升沿从Q1,Q2端口读取。 |

| SAME_EDGE模式 | 在该模式下,上升沿读取的数据,可以在下一个时钟周期的上升沿从Q1端口读取,而下降沿读取的数据,可以在下下个时钟周期的上升沿从Q2端口读取。 |

| SAME_EDGE_PIPELINED模式 | 在该模式下,上升沿和下降沿捕获的数据将可以在下下个时钟周期的上升沿从Q1,Q2端口读取。 |

审核编辑:汤梓红

-

寄存器

+关注

关注

31文章

5317浏览量

120003 -

Xilinx

+关注

关注

71文章

2163浏览量

121005 -

时钟

+关注

关注

10文章

1720浏览量

131362 -

IDDR

+关注

关注

0文章

3浏览量

9478

原文标题:【Xilinx源语】Input DDR Overview (IDDR)介绍(一)

文章出处:【微信号:fpga加油站,微信公众号:fpga加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于Xilinx 和FPGA的DDR2 SDRAM存储器接口

利用IDDR简化亚稳态方案

Xilinx DDR3 资料

无法高速使用IDDR2

什么是IDDR与ODDR看了就知道

FPGA双沿采样之IDDR原语实现 精选资料推荐

Xilinx 7系列FPGA SelectIO IDDR的操作模式详细概述

Xilinx源语:Input DDR Overview(IDDR)介绍

Xilinx源语:Input DDR Overview(IDDR)介绍

评论