Hari Balisetty,Broadcom

如您所知,USB3.0 有一个名为 LTSSM(链路训练和状态状态机)的状态机,它负责

- 初始化和链路训练

- 电源管理转换

- 链路错误恢复和其他连接问题。

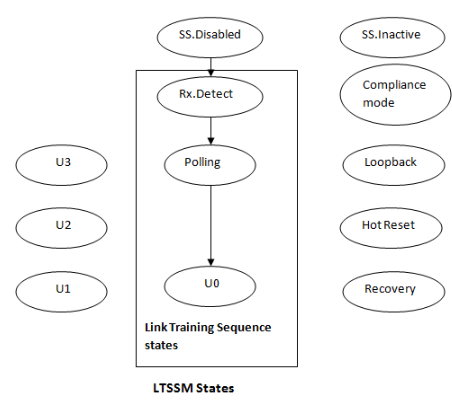

LTSSM 有 12 个高级状态,如下所示。在这篇博客中,我们将检查链接训练中涉及的状态,并了解链接伙伴如何移动到实际传输开始的状态 U0。

链路训练是在上电复位后或热复位时在链路初始化期间发生的一系列事件。这基本上是为了检测链路伙伴并在开始对链路进行任何类型的传输之前训练链路。如上图所示,链路训练序列从 Rx.Detect(上游端口和下游端口的开机状态)开始,以出口到 U0 结束,这是发送和接收数据包的正常操作状态。在链路训练之前,上游和下游端口都将处于 SS 状态。禁用状态(删除端口的超高速连接的状态)。在轮询状态下,通过 LFPS(低频周期信号)握手启用链路训练,该握手用于在没有 SS 信令的情况下传达信息

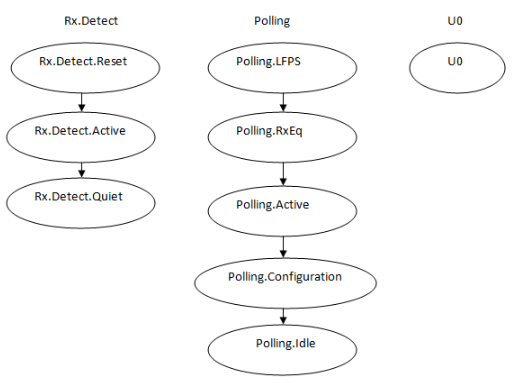

下图显示了链接训练状态及其子状态。

如何配置验证 IP 以与 DUT 同步完成超高速链路训练序列?Synopsys 的 USB 3.0 和 3.1 验证 IP 定义了多个具有适当默认值的计时器和参数,这使得实现这一目标变得简单。其中一些参数映射到 USB 规范,添加一些参数是为了帮助验证 DUT 在正常或错误条件下的运行情况。默认值可确保您可以启用链接训练序列,而无需覆盖任何参数值。

在某些情况下,您可能需要调整参数以尝试不同的极端情况或进一步减慢链接训练所需的时间。在这里,我们将专门查看链路训练序列(由于热复位或上电复位),并将关联 VIP 中影响该序列的参数。

斜体中提到的所有名称都是 USB VIP 中svt_usb_configuration类中的变量,方括号 [] 中的名称/值是 USB 规范名称/值。如果未提及端口方向,则将其视为上游(主机)和下游(设备)端口。

Rx.检测.重置

进入此状态可能是由于热复位或开机复位。当物理电源进入 P2 状态时,请注意以下参数。根据以前的物理电源状态,VIP 使用以下一个(或多个)计时器值。

- p0_to_p2_transition_time

- p3_to_p2_transition_time

- p3_to_p0_transition_time

- allow_p2_p3_direct_transition

如果该条目不是由于热重置,则它直接移动到 Rx.Detect.Active。如果条目是由于热重置,则转换取决于端口 VIP 配置为的类型。

- 如果将 VIP 配置为下游端口(主机),则它会在 t_reset_timeout[tReset] 时间内传输 LFPS。这称为热复位序列。一旦计时器到期,VIP 就会停止发送 LFPS 并移动到 Rx.Detect.Active。

- 如果将 VIP 配置为上游端口(设备),则在主机(连接到 VIP 的 DUT)完成发送 LFPS 热复位信号后,将转换为 Rx.Detect.Active。

Rx.Detect.Active

此状态用于检测另一端的链路伙伴。在此状态下,如果检测到“接收器终止”,VIP 将执行“接收器终止”检测 (receiver_detect_time) 并移动到 Polling.LFPS。如果未检测到接收器终止,则执行以下操作。

- 如果VIP是下游端口(主机),则它将移动到Rx.Detect.Quiet。

- 如果VIP是上游端口(设备),则它会移动到Rx.Detect.Quiet rx_detect_termination_detect_count[8]次。如果即使在此之后仍未检测到低阻抗端接,则移至SS。禁用。

Rx.Detect.Quiet

在这里等到rx_detect_quiet_timeout[12ms计时器]到期,然后移回Rx.Detect.Active。

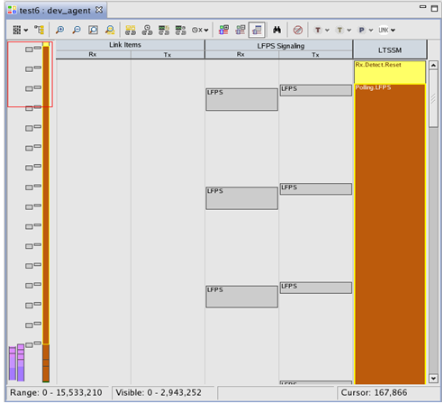

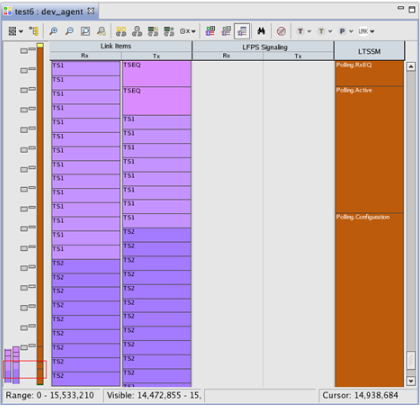

图 1:轮询中的 LFPS 信令。

Polling.LFPS

一旦检测到链路伙伴处于 Rx.Detect 状态,两个(上游和下游)端口都将进入轮询状态以训练链路。在此状态下,VIP 将传输 LFPS,直到突发计时器 polling_lfps_burst_time) 过期。它还计算收到的突发次数,并检查是否满足退出条件(检查下面的退出标准)。如果不满足退出条件,则VIP将等待“重复计时器”(polling_lfps_repeat_time)过期,然后再次启动上述过程(传输LFPS)。

退出到 Polling.RxEq 的退出条件。

- polling_lfps_sent_count(发送的LFPS突发数量)[16]

- polling_lfps_received_count (收到LFPS数量) [2]

- polling_lfps_sent_after_received_count(从链路伙伴接收到第一个 LFPS 后发送的 LFPS 突发数)[4]

在 [360ms 计时器] 到期之前满足退出条件非常重要polling_lfps_timeout。如果超时过期,则 VIP 根据端口的方向执行以下操作之一

- 如果下游端口(主机),则移动到 Rx.Detect

- 如果上游端口(设备),则它移动到SS。禁用

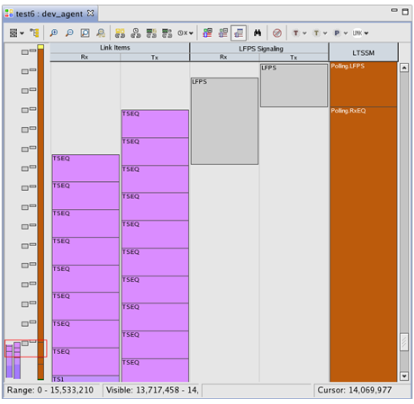

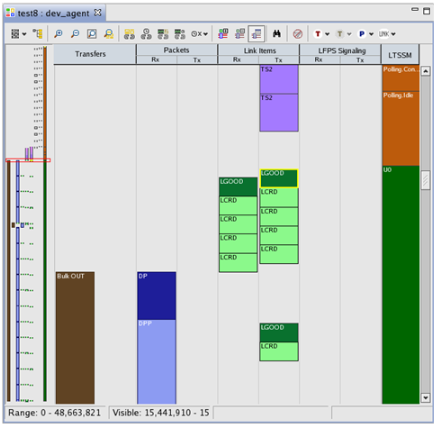

图 2:在轮询期间交换 TSEQ。

Polling.RxEq

此状态用于通过交换 TSEQ(均衡训练序列)有序集来训练均衡逻辑。可以通过启用ltssm_skip_polling_rxeq来跳过此状态。传输polling_rxeq_tseq_count [65,536] 个 TSEQ 订购集 VIP 的数量将移动到轮询活动。

轮询.活动

在此状态下,VIP 将继续发送 TS1,直到连续收到polling_active_received_ts_count数量的 TS1/TS2。每次收到不同的序列时,VIP 都会重置计数器。因此,它确保连续接收 TS1 或 TS2 polling_active_received_ts_count [8] 次。

请务必在 [12ms 计时器] 到期之前满足退出条件polling_active_timeout。如果此超时过期,则 VIP 将执行以下操作之一:

- 如果它是下游端口(主机),它将移动到 Rx.Detect

- 如果它是上游端口(设备),那么它将移动到 SS。禁用。

图 3:在轮询中交换 TS1 和 TS2。活动和轮询。配置

轮询.配置

在此状态下,VIP 将开始发送 TS2,但只有在从链路伙伴收到第一个 TS2 后才会开始计数。

退出条件:满足以下计数后,将退出此状态。

- polling_configuration_received_ts2_count [8] //收到 TS2 的编号

- polling_configuration_sent_ts2_count [16] //从链路伙伴处收到第一个 TS2 后发送的 TS2 编号

在 [12ms 计时器] 到期之前满足退出条件非常重要polling_configuration_timeout。如果超时过期,则 VIP 执行以下操作之一

- 如果是下游端口(主机),则移至 Rx.Detect

- 如果它是上游端口(设备),它将移动到 SS。禁用。

轮询.空闲

在此状态下,VIP 要做的第一件事是检查在轮询配置中接收的 TS2 中是否设置了复位位,以及端口方向是否在上游(设备)。如果检测到这两种情况,VIP 将直接进入 LTSSM 的热重置状态。

如果上述条件为假,则在达到以下“计数”时退出 U0。

- polling_idle_received_idle_count [8] // 收到的闲置数

- polling_idle_sent_idle_count [16] // 从链接伙伴收到第一个空闲后发送的空闲编号。

这里重要的一点是在 [2ms 计时器] 到期之前满足polling_idle_timeout退出条件。如果超时过期,则 VIP 执行以下操作之一

- 如果下游端口(主机),则移至 Rx.Detect

- 如果上游端口(设备),则移至SS。禁用。

图 4:链路训练结束时的 U0 状态

完成轮询.空闲后,链路将变为 U0 状态,此时物理功率更改为 P0,实际传输开始。在任何给定时间点通过此序列,上游端口(设备)移动到 Rx.Detect 在热复位时。大多数VIP可以选择从U0状态(usb_ss_initial_ltssm_state)开始,以便用户可以跳过整个初始链路训练,并且可以从模拟开始就开始传输。有时连接到VIP的DUT可能没有跳过链路训练的选项,在这种情况下,我们建议使用本博客中提到的配置参数,以尽量减少链路训练中的模拟时间。

审核编辑:郭婷

-

usb

+关注

关注

60文章

7979浏览量

265605 -

计时器

+关注

关注

1文章

426浏览量

32807 -

DUT

+关注

关注

0文章

189浏览量

12460

发布评论请先 登录

相关推荐

USB3.0与USB2.0的差别

HD3SS6126用于USB3.0信号切换,是否可以级联是用,最多可以级联几级?

USB3.0的连接问题

请问USB3.0中HS和SS信号什么情况下可以分开使用?

USB3.0和USB2.0

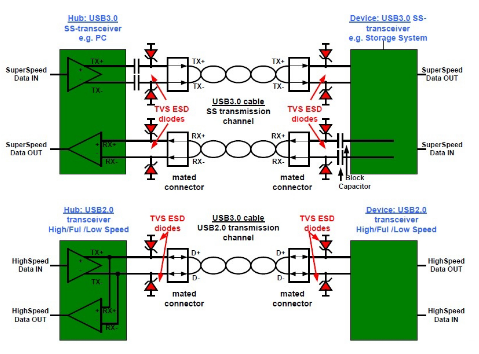

USB3.0系统的ESD防护设计方案

FPGA和USB3.0通信-USB3.0 PHY简介

什么是USB3.0?usb3.0与usb2.0有什么区别?

USB3.0如何辨别

USB3.0中SS链路训练的来龙去脉

USB3.0中SS链路训练的来龙去脉

评论