验证复杂的 SoC 需要付出很多努力。我们的用户调查显示,流片复杂SoC所涉及的工程资源中约有70%用于验证,其中一半时间用于调试。

如果没有经过深思熟虑的验证环境,验证团队会浪费大量时间在 SoC 级别重新创建验证环境以实现芯片级验证,因为他们不考虑重用最初开发的环境来验证其块级 IP。即使跨相同的抽象级别,也无法重用相同的验证IP和环境来支持仿真和仿真,也会导致延迟,并消耗不必要的工程资源。

能够在整个 SoC 项目中一致地重用验证环境,可显著提高验证效率。但是,要从这些生产力优势中获益,核查团队需要仔细规划其验证过程所有阶段的方法。

验证范围

通常,验证团队会开发单独的流来支持块和 SoC 级别的验证。除了支持这些不同抽象级别之间的重用外,验证环境还应可在验证过程的不同阶段重用,以最大程度地减少工作量。

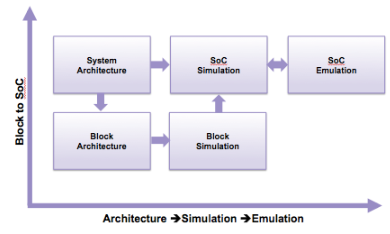

图1:验证光谱的两个维度

每个设计的起点通常是系统架构,因为它定义了整体性能要求或约束。从设计和验证的角度来看,目标应该是在后续阶段重用这些性能约束,并确保设计在集成 RTL 和设计发展时继续满足这些约束。

例如,当系统架构师的约束(如总线吞吐量和延迟)已在块级别进行验证时,验证团队如何确保在 SoC 级别满足这些约束?

为此,验证团队应旨在重用组件,通常是在块和 SoC 级别监控这些约束的验证 IP。验证负责人必须提出具有通用方法、环境和验证IP的测试平台架构,该架构可在块和SoC级别重用。当然,协议验证 IP 必须能够利用系统架构师提供的性能约束,并突出显示整个系统互连中的任何违规行为。同时,为了最大限度地提高工作效率,团队应确保为块级验证编写的测试也能在 SoC 级别工作,并在模拟和仿真中工作。

一致性是关键

系统架构师最有可能使用事务级建模 (TLM) 技术。重用的关键是确保 API 在环境和抽象级别之间保持一致。例如,TLM API 应该与用于仿真的 C API 保持一致——无论团队正在处理验证流程的哪个阶段。

每个 API 下的内容(驱动程序)对于每个环境都是唯一的,例如,用于模拟的 SystemVerilog 驱动程序和用于仿真的 RTL 驱动程序。无论 API 在驱动程序级别与什么接口,重用验证 IP 的 API 的能力都是支持重用的关键。

支持块到 SoC 重用

虽然一致的 API 支持在整个验证范围内重用,但 IP 到 SoC 重用是提高生产力的关键领域之一。它需要一种基于遵守最佳实践准则、一致的验证环境和一致的 VIP 的方法。

一致的语言和方法

在模块和SoC级别以及所有验证IP中使用通用语言(如SystemVerilog和UVM),可以更轻松、更快速地在每个级别集成和测试设计。

通用验证计划

再利用原则应尽可能扩大到核查计划。在块级别定义验证计划所做的工作应转移到 SoC 级别。这应包括验证团队可以重用的功能覆盖定义和测试。

共享功能覆盖数据库

在一开始就拥有一致的覆盖率数据库可以节省将多个专有数据库手动合并为通用格式的大量时间。一致的数据库将使验证团队能够轻松快速地比较不同抽象级别的结果。

通用序列库和调试

通过使用通用序列库,能够在模块和SoC级别之间轻松重用激励,这将提高验证效率。

设计和验证团队在调试上花费了大量时间。在 SoC 级别发现错误时,工程师可能必须转回 IP 级别来调查问题。能够在单个通用调试环境中执行此操作,可以最大限度地减少团队在学习和熟悉不同环境上花费的时间。

验证团队还可以从整个测试台的可见性中受益。能够在 IP 和 SoC 级别查看调试器代码窗口中的事务,可以节省在不同调试环境之间切换的时间。

通用语言、方法、规划和调试是在验证环境的不同阶段实现块到 SoC 重用的先决条件。

有了正确的基础设施,团队就可以专注于构建与模块接口的测试套件。

测试套件

对针对块级的测试套件采用错误的方法,使得在 SoC 级别重用块级验证环境和测试变得困难。

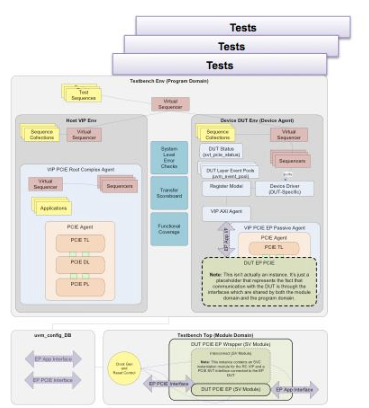

图 2 显示了如何配置测试套件以支持在块级别验证 PCI Express IP,这也适合在 SoC 级别重用。

图 2:PCI Express 设计的测试套件

测试套件设计为模块化。图 2 右上角的模块显示了如何将 PCI Express 端点 RTL、AXI 接口和相关驱动程序封装到一个环境中。关系图的左上角显示了封装在另一个环境中的根复杂 VIP。将整体环境与“底层”隔离开来是实现块级和 SoC 级验证之间平稳过渡的关键。

在实现测试套件时,目标应该是避免进行会阻碍重用的更改;以避免多次“触摸”测试。即使是相对较小的任务,如更改属性的分层路径,如果必须更改数百甚至数千个测试,也会产生大量工作。

为了最大程度地减少更改,验证团队在规划和编写测试时应考虑块级别和 SoC 级别之间可能更改的内容,并确保测试不引用内部环境。最好的方法是创建“配置感知”的测试,即测试应该了解整体环境和配置。测试应传递配置的名称,并让驱动程序决定如何应用信息。

验证团队必须将所有这些原则付诸实践,以便实现从块到 SoC 级别的重用。弄错它们会产生额外的工作,以便将IP测试套件过渡到芯片级别。

新思科技VC验证IP

Synopsys 在构建其下一代验证 IP 解决方案时广泛使用 SystemVerilog,以支持易用性和重用性。例如,Synopsys 为符合 UVM(通用验证方法)的测试套件提供 SystemVerilog 源代码,这可以节省大量开发时间并减少对内部专业知识的需求。内置功能使工程师能够在整个验证范围内应用一致的方法,以便在模块和 SoC 级别进行高效验证。

Synopsys 验证 IP 和测试套件解决方案支持从架构分析到模块验证、互连设计、SoC 集成,最后到仿真中的软硬件协同验证的整个验证过程。广泛的 Synopsys 验证 IP 产品组合包括验证复杂 SoC 设计所需的最新协议、接口和存储器。Synopsys VIP 部署在数千个项目中,支持 AMBA、PCI Express、USB、MIPI、DDR、LPDDR、HDMI、以太网、SATA/SAS、光纤通道、OCP 等。

总结

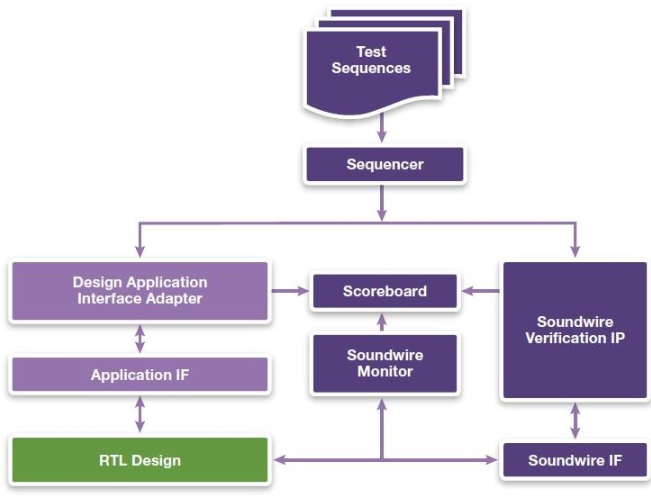

验证 IP 已成为验证流程的关键部分,支持广泛的任务,例如性能分析、IP 模块、互连和 SoC 的 RTL 验证,以及以具有仿真功能的事务处理器的形式实现全芯片验证,包括硬件-软件协同验证。

验证环境中的 IP 到 SoC 级重用可以提高整个验证过程的工作效率。这种方法要求验证团队使用相同的语言、方法和验证 IP 开发可重用的块测试环境,所有这些都必须专门构建以支持重用,并具有一致应用的指南。

审核编辑:郭婷

-

soc

+关注

关注

38文章

4118浏览量

217923 -

IP

+关注

关注

5文章

1647浏览量

149325 -

仿真

+关注

关注

50文章

4040浏览量

133411

发布评论请先 登录

相关推荐

[启芯公开课] SystemVerilog for Verification

混合信号SoC助力模拟IP发展

基于C的测试和验证套件集成到常规UVM测试平台的方法

基于C的测试和验证套件集成到常规UVM测试平台的方法

SOC测试访问机制

CoreSight SoC-400综合套件解决方案

MIPI声线测试套件

SystemVerilog测试套件加速IP到SoC的重用

SystemVerilog测试套件加速IP到SoC的重用

评论