随着实习面试的临近、秋招的逐步靠近,愈发觉得知识需要成系统,让它们串接起来。不然,太容易忘了

1、单比特信号

1.1电平同步

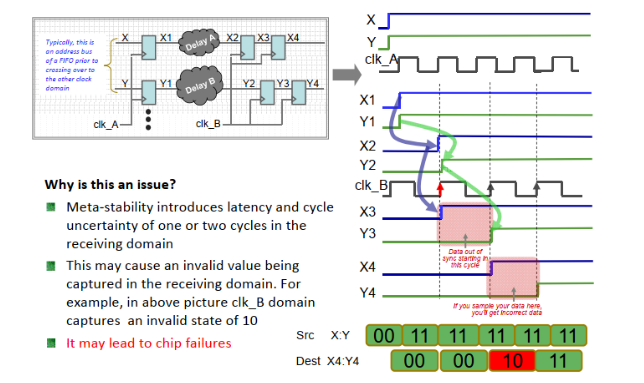

当我们需要在两个时钟域间传输一个电平信号,这里的电平信号表示信号能够维持一定的时间(如在原时钟域内至少维持两个周期),可以采用两个触发器打拍。

类似下面这种,持续一定时间,能在亚稳态稳定后采样到稳定的值,即第一个周期可能同步失败,但第二个周期有机会采样稳定的值,不发生亚稳态

1.2、脉冲同步

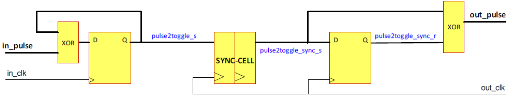

当信号在发送端时钟域内只能持续一个周期时,可以称为脉冲信号。要注意的是,发送的是脉冲,收到的也应该是脉冲。

为了让脉冲能够被接收端采样,可以将脉冲信号在发送时钟域内变成电平信号。即采样到in_pulse为1,则翻转Q,将脉冲变成边沿。

只要脉冲有足够的间隔,就能保证接收端能够边沿检测,从而输出一个接收时钟周期的脉冲

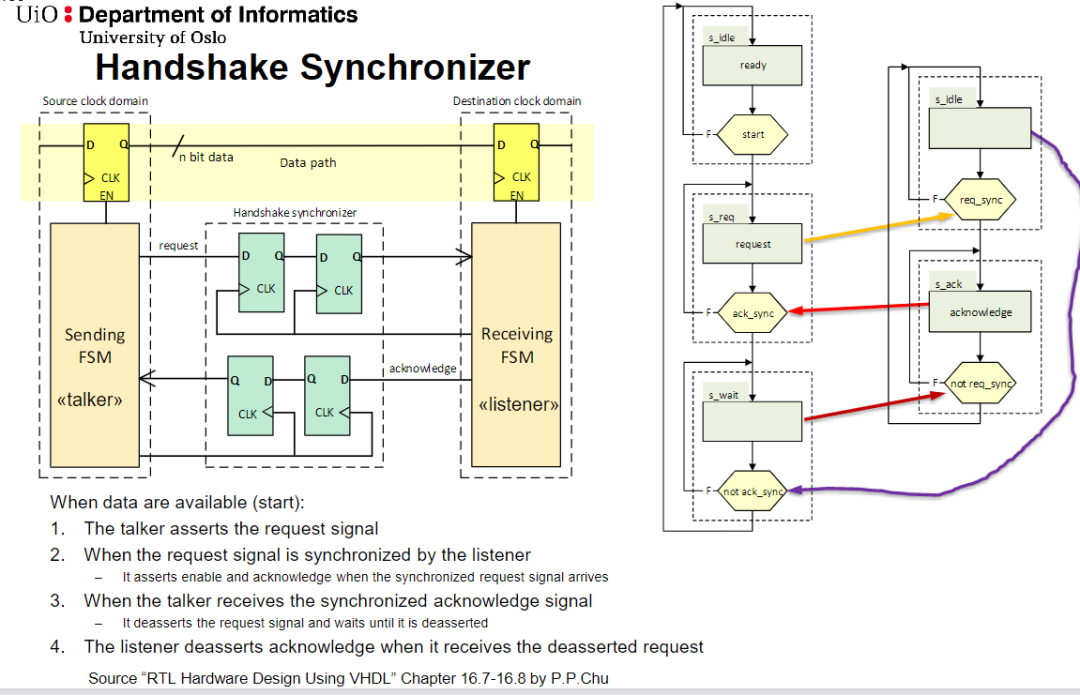

1.3 握手

很显然,上面两种方式不存在接收方对发送方的反馈。

也可以使用握手协议,确保一笔一笔的完成传输,只有完成一笔传输,才会改变数据。

见:握手信号传输跨时钟域数据

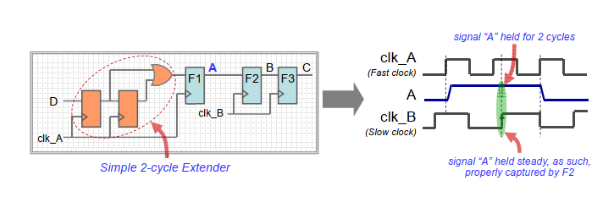

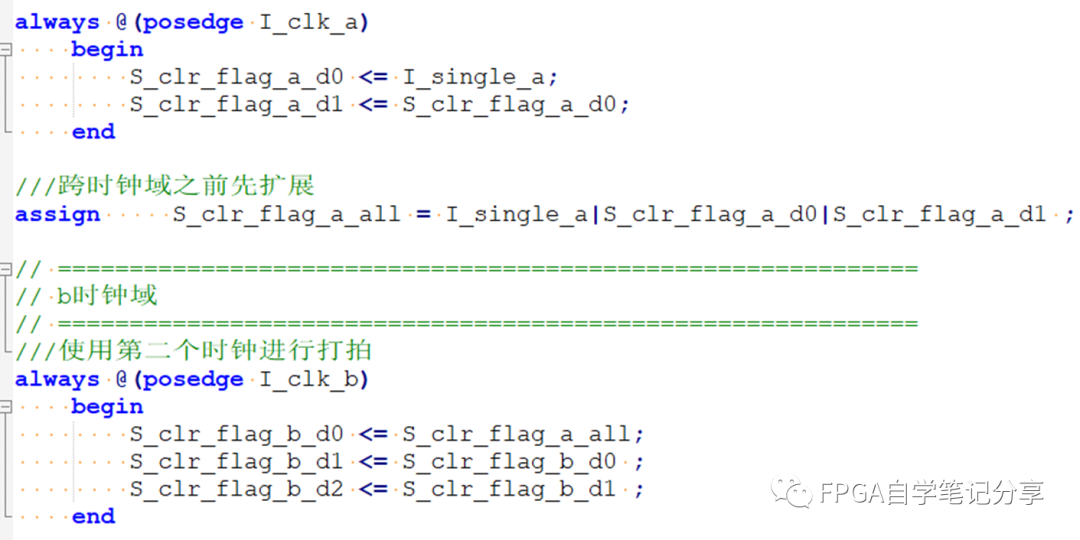

1.4 展宽

当信号宽度不够,可以使用展宽的方法,如在发送域打拍,然后取或

2、多bit

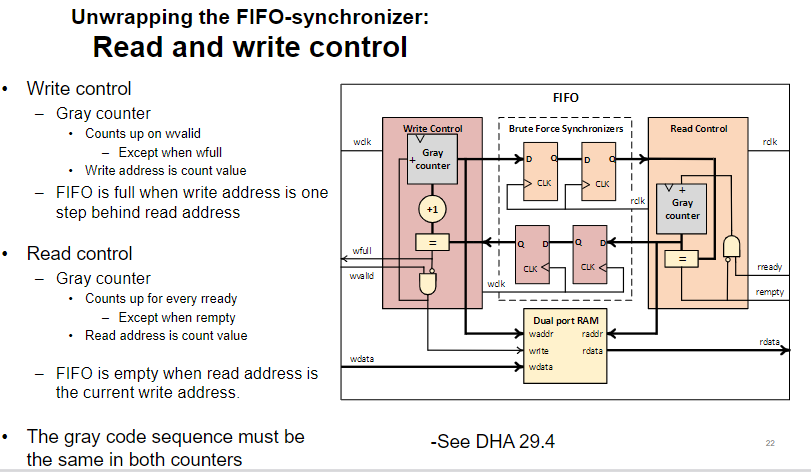

2.1 异步FIFO

使用异步FIFO传输数据--格雷码计数器实现

使用异步FIFO传输数据--对以前的强烈批判

2.2 多路复用

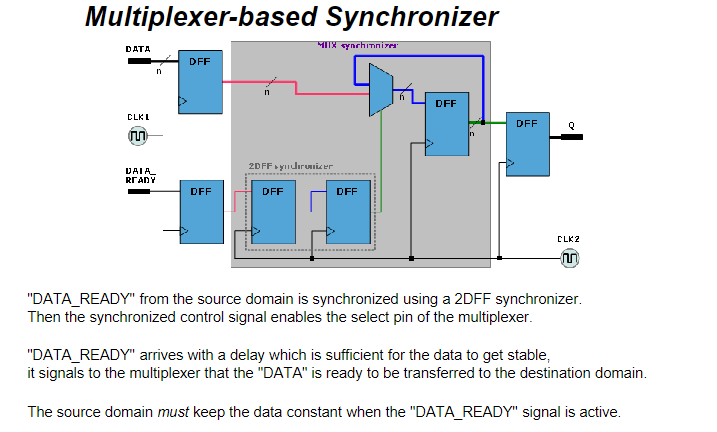

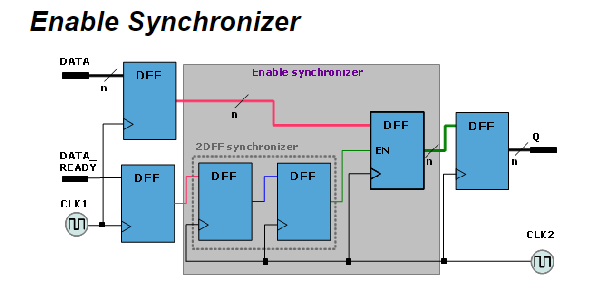

DMUX数据有效会搭配一个标志信号data_ready,对标志信号进行同步,将同步后的标志信号作为MUX的选通信号。

在发送时钟域内,标志信号和数据是同步的,在同步器内,标志信号同步有延迟。这样即使数据和标志信号在接收时钟上升沿附近变化,data_ready可能发生亚稳态,亚稳态结束后,同步后的标志信号可以正常工作。而数据在这些延迟内,能够达到稳定,即接收方采样的data是不变的,当然不会违反建立保持时间

这要求当data_ready=1时,data要保持

换种方式,我们可以将标志信号作为于触发器使能端。道理是类似的,en=0,并不会使能触发器的采样

2.3 握手

和单bit类似,协议让数据维持足够的时间

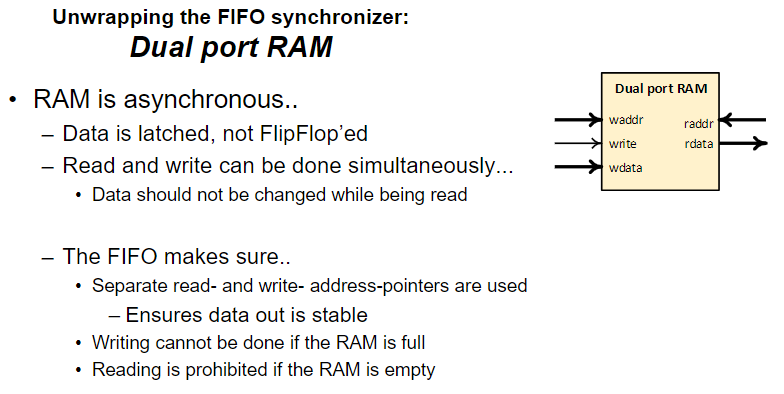

2.4 双口RAM

双口RAM可以同时读写

增加读写控制逻辑,很像异步FIFO,不多说

3、收敛

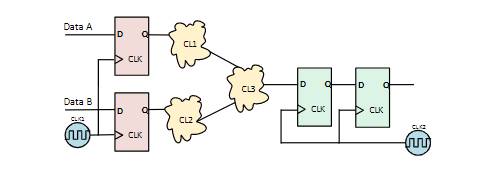

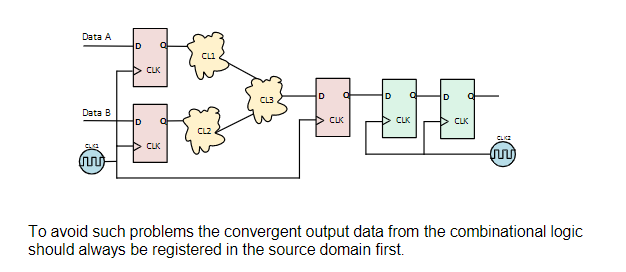

当出现信号的合流时,如下图所示,dataa和datab将经过组合逻辑变成1bit。由于组合逻辑的延迟不同,可能出现毛刺,可能传输到错误的信号,

解决办法就是发送方再打拍

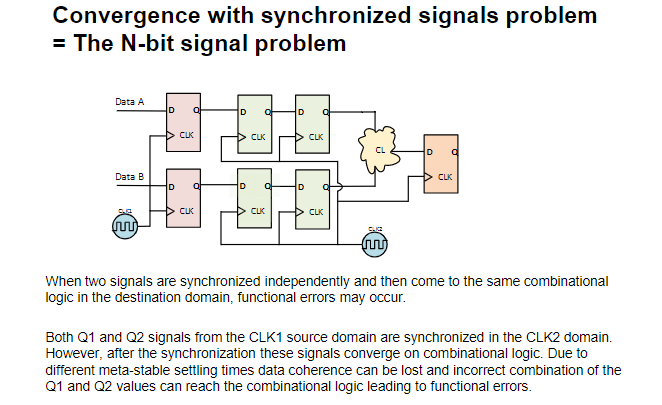

还要注意的是,两级同步后,也应该避免多比特使用组合逻辑,原因在于亚稳态恢复的数据不确定

4、发散

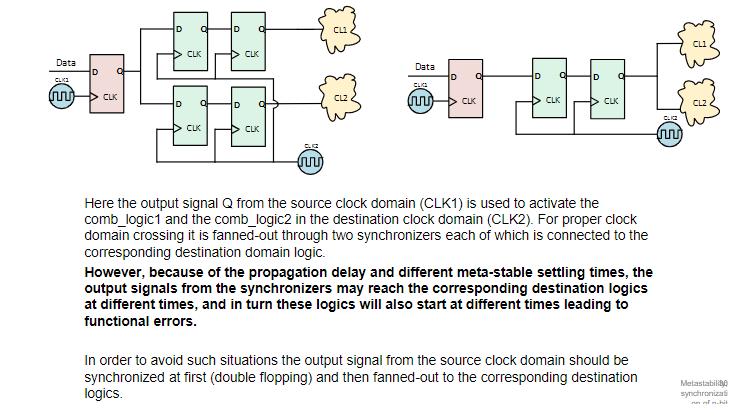

当信号要作用于接收方的不同逻辑时,即有多个扇出,由于传播延时和不同的亚稳态解决时间meta-stable settling time,输出也可能不同。

因此只能先同步然后使用,避免分别同步使用

审核编辑:汤梓红

-

脉冲

+关注

关注

20文章

892浏览量

95673 -

fifo

+关注

关注

3文章

389浏览量

43746 -

信号

+关注

关注

11文章

2794浏览量

76896 -

Mux

+关注

关注

0文章

38浏览量

23405 -

时钟域

+关注

关注

0文章

52浏览量

9542

原文标题:跨时钟域梳理

文章出处:【微信号:Hack电子,微信公众号:Hack电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

跨时钟域知识点梳理

跨时钟域知识点梳理

评论