您可以在手持设备的空间中装入多少个晶体管?这个数字每过十年就会增加几个数量级。便携式音乐播放器说明了这一点。1979年,晶体管收音机需要大约200个晶体管。1984年,CD播放器需要大约1,500个晶体管。1990年,MP3播放器需要大约10,000个晶体管。对于2015年的数字音频播放器,大约有1,000,000个晶体管。工艺技术的进步使这些增长成为可能,如今,主要由先进的AI和5G应用驱动的多芯片系统正在帮助实现另一个巨大的飞跃。事实上,在 2023 年,一部典型的智能手机拥有超过 10 亿个晶体管!用户优势显而易见。就音乐而言,这意味着更好的保真度,更多的空间来播放,存储和流式传输您喜欢的音乐,共享,播放,与其他设备的互操作性等方面的更多功能等等。但复杂性并非没有设计挑战。

对计算资源的增加需求实际上与本地服务器的资本支出或安装它们所需的时间不一致。面对成本压力、不断缩小的市场窗口和市场需求(更好的性能和更多的功能),本地存储是许多企业无法再承受的负担。在云中对IC设计的计算资源进行弹性扩展的需求已经到来。

第一个使您能够利用云进行 IC 设计的大规模 SaaS 解决方案是 Synopsys Cloud。Synopsys 云将高级计算和存储基础架构的可用性与按需无限制地访问 EDA 软件许可证相结合。作为台积电开放创新平台®(OIP)生态系统的一部分,新思科技最近与台积电和微软合作,使用Synopsys IC验证器™物理验证(Synopsys Cloud产品)在台积电N3E流程的Microsoft Azure云中执行设计规则检查(DRC)的测试用例。

结果呢?云中的 DRC 可以帮助您更快地完成下一个大型复杂 IC 设计 - 方法如下。

显著缩短设计规则检查的运行时间

那么,为什么我们选择DRC作为我们的测试用例呢?DRC 确保设计正常运行,并且可以在铸造厂制造。使用传统的本地计算资源执行它们可能需要宝贵的时间,尤其是在设计变得更大、越来越复杂的情况下。

由于当今的设计尺寸更大,因此流程规则的数量也有所增加。事实上,当今许多设计中的流程规则可能达到数千条,而增加的设计复杂性可能导致数百个步骤。对于拥有数十亿个晶体管的多芯片系统,DRC 或布局与原理图 (LVS) 作业可以运行数天并利用数百个 CPU 内核。

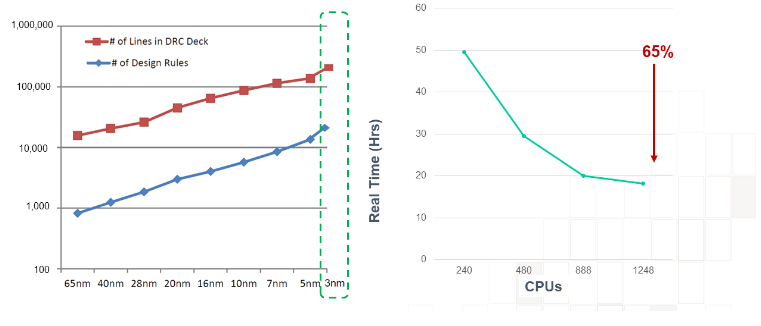

在较短的上市时间 (TTM) 窗口中需要增强的计算能力会导致物理验证挑战。当工艺节点从 7nm 推进到 5nm 再到 3nm 甚至更高时,尤其如此。例如,在 3nm 时,一个运行集可以包含超过 15,000 个复杂规则,并且需要 10 倍的 DRC 计算操作来执行规则。因此,仅一次迭代,全芯片 DRC 签核就可能消耗数万个 CPU 小时。虽然物理验证一直是计算密集型的,但当今设计的尺寸和复杂性将这一挑战提升到了一个全新的水平。

运行 DRC 和 LVS 作业的串行依赖关系意味着购买更多计算能力并不一定等同于更快的运行时间。需要计算规模的IC验证意味着在串行操作期间,部分计算能力有时会处于空闲状态。如果您没有找到针对此类场景优化计算资源的方法,这将影响您的底线 - 您将为那些未使用的资源付费。

使用云计算进行 IC 验证可以帮助您消除这种情况。通过云验证,您可以从数百个本地 CPU 内核扩展到云中的数千个 CPU 内核。这种弹性为您提供了灵活性、敏捷性和可扩展性,可在需要时仅使用所需的计算资源。运行集中的 DRC 可以分布在多个内核中并行运行,从而优化计算资源,从而节省时间和金钱。

云中的 IC 设计如何将验证时间缩短 65%

在 Synopsys、台积电和微软的合作中,我们根据内部部署验证评估了云验证。为了启动测试,台积电的工艺设计套件 (PDK) 和 DRC 被上传到 Synopsys 云环境。我们根据 Synopsys IC 验证器中的设计类型选择了不同的资源,这是 Synopsys Cloud 环境中用于物理验证的单独应用程序,并且为资源预先选择了计算选项。在我们上传运行测试用例所需的脚本并选择 Microsoft Azure 实例(FX 和 Mdsv2 计算以及用于共享存储的 Azure Netapp Files (ANF))之后,我们只需单击一下即可创建虚拟机 (VM) 群集,其中包括数百个 CPU 内核。

我们的实验流程在几个小时内就可以执行了,我们快速执行了一个大型测试用例,以比较使用台积电 N3E 流程在云中运行的作业和台积电本地运行的作业的结果。所有结果(云和本地)都使用XOR操作保存在GDSII文件中,并且两次运行中的任何错误都必须完全匹配才能获得干净的结果。

云作业的实时运行小时数从大约 50 小时减少到 20 小时以下,与本地作业相比,云中的运行小时数提高了 65%。此外,与本地相比,在云中的测试运行中,CPU 小时数和成本降低了 25%。

云端IC设计 台积电N65E工艺运行时间缩短3%

图片来源:台积电

新思科技 IC 验证器是现代设计的物理验证工具

Synopsys IC 验证器是一种物理验证工具,可以在数千个 CPU 内核之间分配作业。这项技术成功的核心是调度程序,它为每个内核的命令排队,以使用 DRC 序列优化文件位置。它还估计和平衡内核之间的内存需求,并最大限度地减少峰值磁盘使用,动态监控每个内核上的负载并调整系统以提高内核和内存利用率。由于它在异构配置中工作,通过容错功能具有实际延迟,因此它可以检测主机重新启动、网络和套接字故障、计算机崩溃和磁盘空间限制并从中恢复。

IC 验证器动态弹性 CPU 管理可与流行的作业队列系统(如负载共享设施 (LSF) 和太阳网格引擎 (SGE) )无缝协作。它可以用于不同类型的计算网络,例如本地和云。其资源和成本优化的同时,它加速了时序收敛以满足流片计划,使用高达 40% 的计算资源,同时保持与传统 DRC 和 LVS 作业相似的性能。这意味着在云中节省了成本,其中资源和存储按时计费。

除了这些好处之外,IC 验证器不需要等到所有资源都可用才能开始工作。它可以以最少的资源立即启动,并在可用时使用更多的资源。Microsoft Azure CycleCloud 和加速网络(单根 I/O 虚拟化,SR-IOV,可以将 Azure 的大部分软件定义网络堆栈从 CPU 卸载到 FPGA 智能网络接口卡或 NIC),以帮助确保分别针对虚拟机优化的扩展和增加的数据吞吐量。

确保云中的 EDA 安全无虞

除了所有时间和成本优势之外,您还可以通过采取措施确保您的系统得到适当保护,从而确保云部署中的 EDA 安全。与最新标准保持同步,并确保您的网络安全系统是最新的。拥有管理良好且隔离的虚拟网络 (VNET) 是关键。

审核编辑:郭婷

-

IC设计

+关注

关注

38文章

1297浏览量

104075 -

服务器

+关注

关注

12文章

9227浏览量

85620 -

DRC

+关注

关注

2文章

149浏览量

36211

发布评论请先 登录

相关推荐

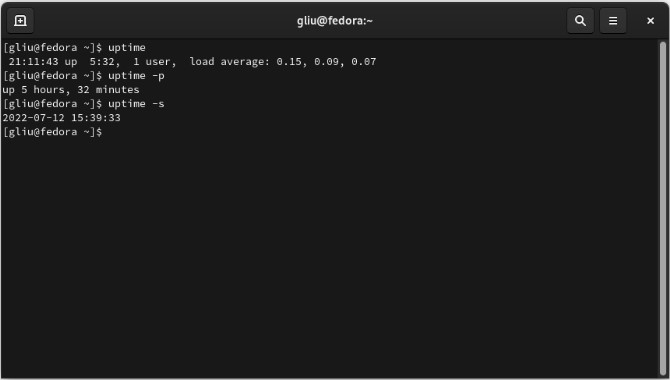

如何检查Linux服务器的运行时间

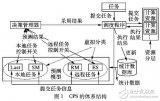

基于本地任务与远程任务运行时间的CPS和PAA的概念

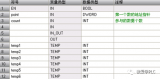

电机运行时间进行排列 是分为两个部分来完成这个程序的设计的

MOSIS在领先的FinFET工艺设计中为DRC和LVS signoff部署IC Validator

如何高效测量ECU的运行时间

浅析STM32代码运行时间的技巧

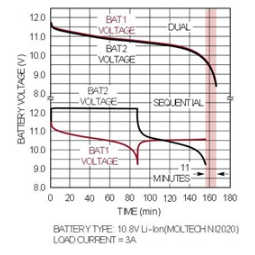

双电池电源管理器将运行时间延长12%,充电时间缩短一半

单片双电池电源管理器可延长运行时间并缩短充电时间

ch32v307记录程序运行时间

西门子SCL编程50台电机运行时间累计方法

云IC验证如何将DRC运行时间缩短65%

云IC验证如何将DRC运行时间缩短65%

评论