目标

本实验活动的目标是进一步强化上一个实验活动 “ADALM2000实验:使用CD4007阵列构建CMOS逻辑功能” 中探讨的CMOS逻辑基本原理,并获取更多使用复杂CMOS门级电路的经验。具体而言,您将了解如何使用CMOS传输门和CMOS反相器来构建D型触发器或锁存器。

背景知识

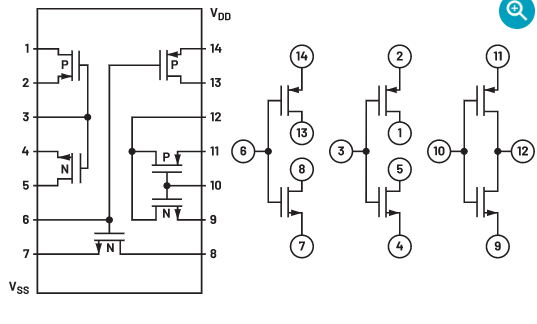

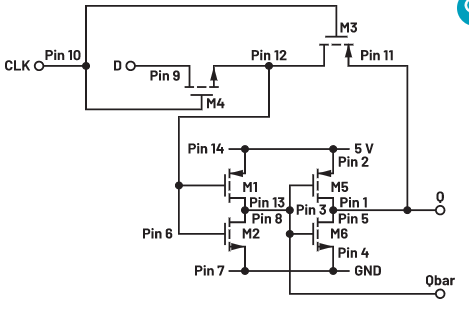

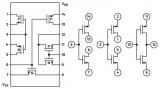

为了在本实验活动中构建逻辑功能,需要使用 ADALP2000模拟部件套件中的CD4007 CMOS阵列和分立式NMOS和PMOS晶体管(ZVN2110A NMOS和ZVP2110A PMOS)。CD4007由3对互补MOSFET组成,如图1所示。每对共用一个共栅(引脚6、3和10)。所有PMOSFET(正电源引脚14)以及NMOSFET(地引脚7)的衬底都共用。左边的互补MOSFET对,NMOS源极引脚连接到NMOS衬底(引脚7),PMOS源极引脚连接到PMOS衬底(引脚14)。另外两对均为通用型。右边的互补MOSFET对,NMOS的漏极引脚连接到PMOS的漏极引脚,即引脚12。

图1. CD4007功能框图。

CD4007是一款多功能IC,我们在上一个实验活动中已有所了解。例如,单个CD4007可用于构建一个反相器链(包括三个反相器)、一个反相器加上两个传输门或其他复杂的逻辑功能,如NAND和NOR门。反相器和传输门尤其适合构建D型锁存器或主/节点触发器。

静电放电

CD4007与许多CMOS集成电路一样,很容易被静电放电损坏。CD4007包括二极管,可防止其受静电放电的影响,但如果操作不当仍可能会损坏。使用对静电敏感的电子产品时,通常会使用防静电垫和腕带。然而,在家里(正规的实验环境之外)工作时,可能没有这些物品。避免静电放电的一种低成本方法是在接触IC之前先使自己接地。在操作CD4007之前,使积聚的静电放电将有助于确保在实验过程中不会损坏芯片。

材料

ADALM2000 主动学习模块

无焊试验板

1个CD4007(CMOS阵列)

2个ZVN2110A NMOS晶体管

2个ZVP2110A PMOS晶体管

说明

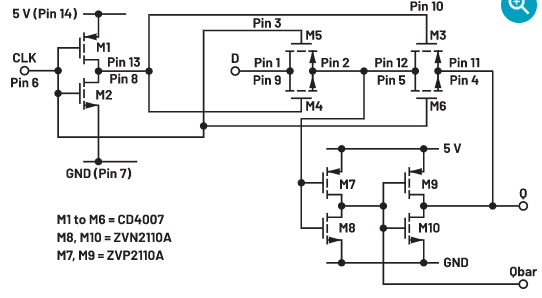

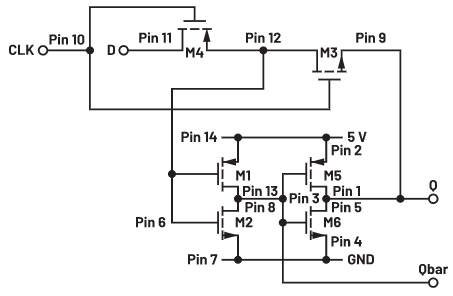

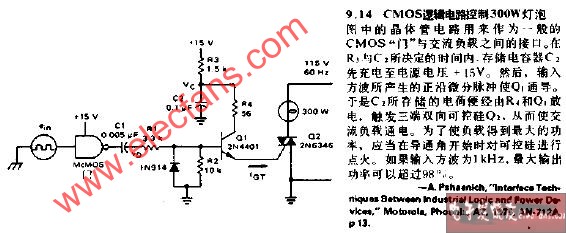

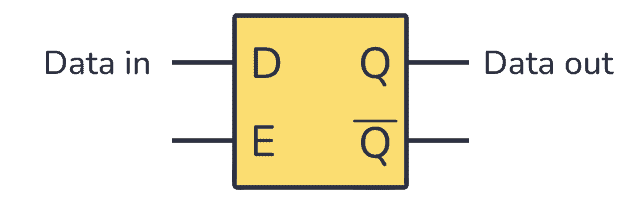

现在我们将结合使用之前练习中的反相器链构建的双传输门来构建D型锁存器,如图2所示。两个传输门协同工作以实现D型锁存器。在锁存器的透明模式下,当CLK=0时,第一个传输门(左)打开,同时第二个传输门(右)关闭。D通过第一个传输门和两个串联的反相器传输至输出端(Q)。在锁存器的保持模式下,当CLK=1时,第一个传输门关闭,但第二个传输门打开。因此,输入端D中的任何变化都不会反映在输出端Q上。不过,现已开启的第二个传输门可确保通过在两个串联的反相器周围形成的闭合正反馈回路来保留Q上先前的逻辑电平。在无焊试验板上构建图2所示的D型锁存器电路。器件M1至M6采用CD4007 CMOS阵列,两个反相器级中的每一级(反相器级M7和M8,以及M9和M10)使用一个ZVN2110A NMOS和一个ZVP2110A PMOS。电路使用ADALM2000的固定5 V电源供电。

图2. D型锁存器。

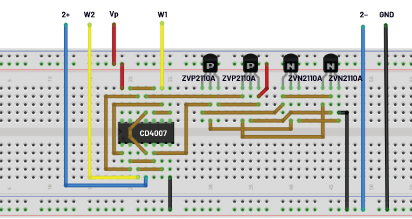

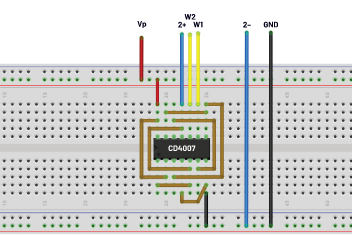

硬件设置

在实验最初,将两个AWG输出配置直流源。根据需要,示波器通道将用于监控电路的输入和输出。固定5 V电源用于为电路供电。在此实验中,应禁用固定–5 V电源。

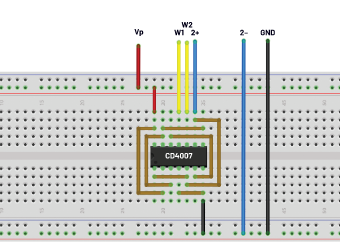

图3. D型锁存器试验板连接。

程序步骤

连接引脚1和9,锁存器的D输入端连接到AWG1的输出端。连接引脚4和11,锁存器的Q输出端连接到示波器通道2。连接引脚6,作为连接到AWG2的CLK。确保打开固定5 V电源。

首先,打开AWG控制界面并将AWG2设置为0 V直流电压,对CLK施加逻辑低电平。将AWG1设置为5 V直流电压,对D输入端施加逻辑高电平。

观察示波器通道2上锁存器的输出端Q。示波器界面上应显示稳定的5 V电压。捕获屏幕截图。

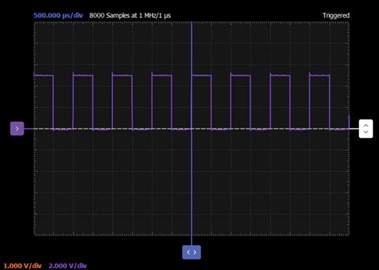

图4. Scopy屏幕截图。

将AWG1设置为0 V直流电压,对D输入端施加逻辑低电平。观察示波器上的输出。这是锁存器的透明模式。此时应能看到示波器通道2也是0 V直流电压。现在将AWG2设置为5 V直流电压,对CLK施加逻辑高电平。同时将AWG1设置为5 V直流电压,对D输入端施加逻辑高电平。

观察示波器界面上的Q输出。由于D输入端之前为低电平,因此尽管将D更改为逻辑高电平,仍会显示稳定的低电平。捕获屏幕截图。这是电路的保持模式。

图5. Scopy屏幕截图。

现在将两个AWG通道均配置为峰峰值为5V的方波。将AWG1设置为1 kHz频率,将AWG2设置为2 kHz频率或AWG1频率的两倍。将AWG2的相位设置为0度。确保将AWG设置为同步运行。

观察示波器界面上在上述CLK和D输入下相应的Q输出。捕获各种波形并保存截图,用于包含在实验报告中。

图6. Scopy屏幕截图。

现在将AWG2的相位设置为90度。再次观察示波器界面上在此时CLK和D输入下相应的Q输出。与AWG2相位为0度时相比有何变化?说明原因。捕获各种波形并保存截图,用于包含在实验报告中。

图7. Scopy屏幕截图。

问题

单个D型锁存器将使输入信号延迟1/2时钟周期。说明时钟相位相反的两个串联D型锁存器如何构成主节点D型触发器,可以使输入信号延迟一个完整的时钟周期。

如果还有CD4007阵列可用,可构建主节点D型触发器作为额外的练习。

替代形式

图2所示的D型锁存器使用具有NMOS和PMOS晶体管的互补传输门。单个NMOS或PMOS无法传递具有相同强度(即导通电阻)的高低逻辑电平。单个NMOS器件可以传递强逻辑电平0,但会传递弱逻辑电平1。相反,单个PMOS器件可以传递强逻辑电平1,但会传递弱逻辑电平0。

在许多集成电路设计案例中,内部信号仅在内部电路模块之间传递,此时单个NMOS或PMOS晶体管传递的非对称驱动不是主要问题。在这种情况下,锁存器中固有的正反馈可能会有所帮助。可以采用简化的D型锁存器,即只使用6个器件而不是图2中使用的10个器件,如图8(锁存器在上升沿)和9(锁存器在下降沿)所示。

图8. 6晶体管上升沿D型锁存器。

图9. 6晶体管下降沿D型锁存器。

硬件设置

图10. 6晶体管上升沿D型锁存器试验板连接。

图11. 6晶体管下降沿D型锁存器试验板连接。

说明

对试验板进行任何更改之前,确保关闭固定5 V电源。在无焊试验板上,将图2中的电路重新配置为图3中的电路。确保打开固定5 V电源。重复相同的步骤,将AWG1连接到D输入端,将AWG2连接到CLK输入端。验证锁存器的工作情况,它将在输入时钟的适当边沿锁存逻辑0和逻辑1输入。

最后,将无焊试验板上的电路重新配置为图4中的电路。确保打开固定5 V电源。重复相同的步骤,将AWG1连接到D输入端,将AWG2连接到CLK输入端。验证锁存器的工作情况,它将在输入时钟的适当边沿锁存逻辑0和逻辑1输入。

替代元件选择

使用四个独立NMOS和PMOS晶体管(ZVN2110A和ZVP2110A)构建的反相器对也可以由第二个CD4007 IC构成,也可以使用例如 74HC04 或CD4049 等六反相器 IC 的 CMOS 反相器。

审核编辑:郭婷

-

CMOS

+关注

关注

58文章

5806浏览量

236695 -

锁存器

+关注

关注

8文章

918浏览量

41772 -

触发器

+关注

关注

14文章

2024浏览量

61488

发布评论请先 登录

相关推荐

CMOS逻辑电路,CMOS逻辑电路是什么意思

ADALM2000实验:CMOS逻辑电路、D型锁存器

CMOS逻辑电路、D型锁存器

CMOS逻辑电路、D型锁存器

评论