封装和层次结构

TLM接口的使用将验证环境中的每个组件与其他组件隔离。验证环境实例化一个组件,并完成其ports/exports的连接,不需要进一步了解验证组件具体的实现。

较小的验证组件可以组合成较大的验证组件,此时上一级组件就是一个简单的引出包含多个子组件的容器。

层次化连接

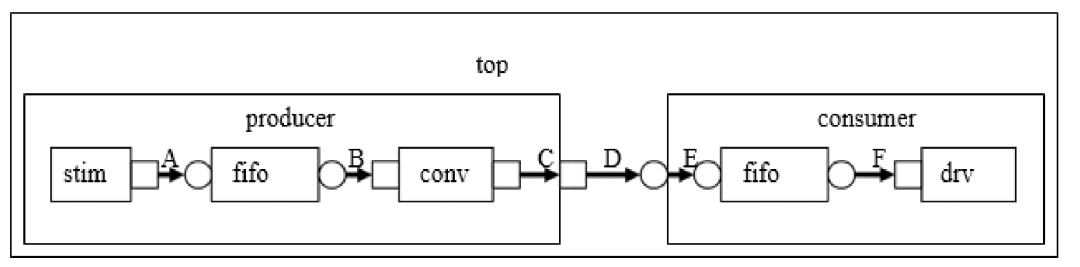

建立跨层次连接涉及到一些额外的问题,考虑下图所示的分层设计。

这个设计的层次包含两个组件,producer和consumer。producer包含三个组件,stim、fifo和conv。consumer包含两个组件,fifo和drv。这两个fifo都是uvm_tlm_fifo 组件的例化。

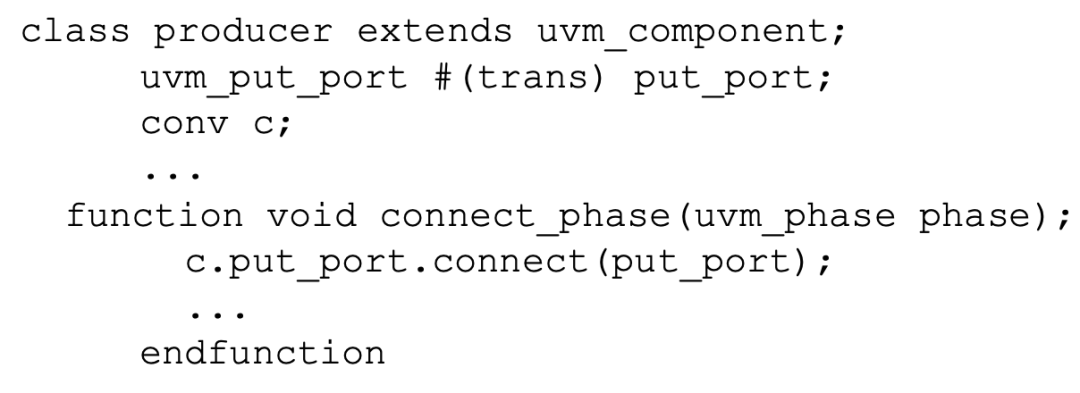

从顶层角度看,producer的put_port与consumer的put_export相连。在上图中,A、B、D和F是标准的 peer-to-peer连接。连接A的代码为:

stim.put_port.connect(fifo.put_export);

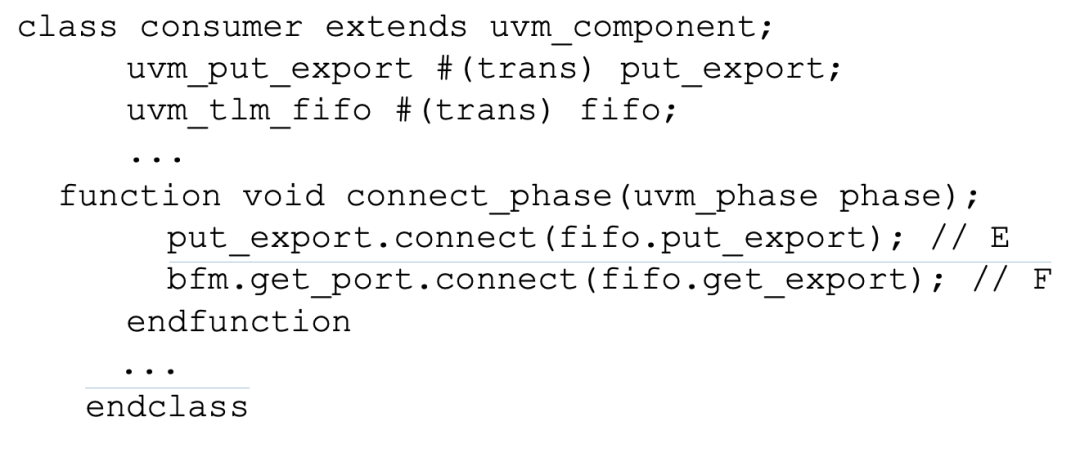

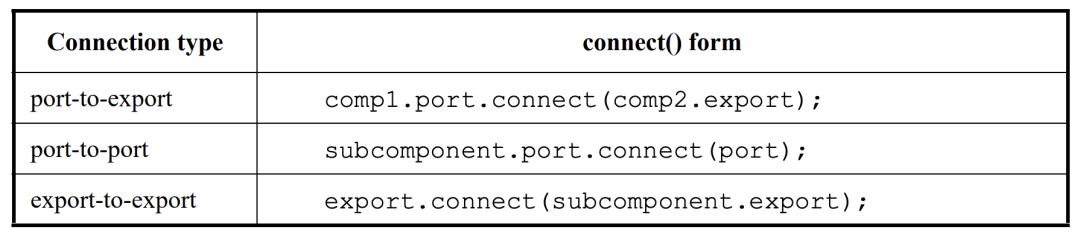

连接C和E有所不同,C是port-to-port的连接,E是export-to-export的连接。这两种连接对于完成层次化连接是必要的。

连接E的代码为:

连接C代码为

连接类型

port.connect()方法的参数可以是一个export和port,这取决于连接的性质(即peer-to-peer或者hierarchical)。

export.connect()的参数总是一个子组件的export。

审核编辑:汤梓红

-

接口

+关注

关注

33文章

8728浏览量

152105 -

封装

+关注

关注

127文章

8033浏览量

143535 -

UVM

+关注

关注

0文章

182浏览量

19240 -

代码

+关注

关注

30文章

4841浏览量

69196 -

TLM

+关注

关注

1文章

32浏览量

24785

原文标题:层次化的UVM TLM连接

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

关于层次化符号的管脚的一个疑问

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...

什么是uvm?uvm的特点有哪些呢

请问一下在UVM中的UVMsequences是什么意思啊

谈谈UVM中的uvm_info打印

海信TLM3229G、TLM3729G彩电电路图

ASIC芯片设计之UVM验证

典型的UVM Testbench架构

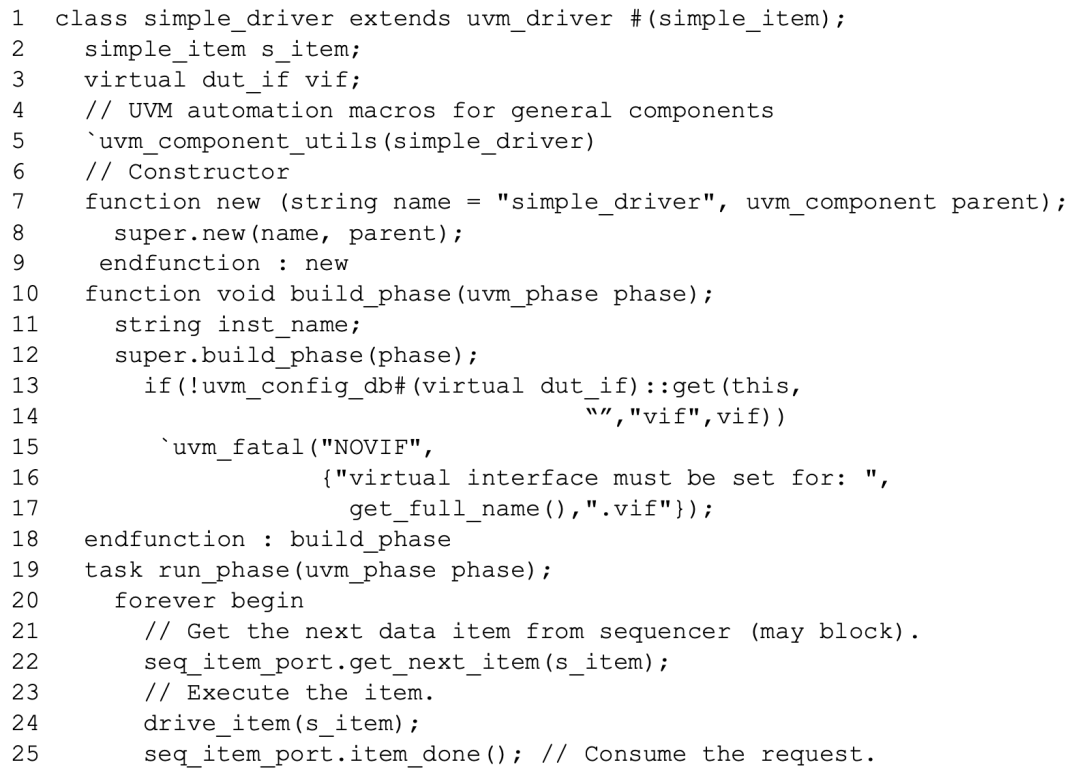

创建UVM Driver

Easier UVM Code Generator Part 4:生成层次化的验证环境

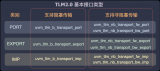

数字IC验证之基本的TLM通信

层次化的UVM TLM连接

层次化的UVM TLM连接

评论