除通过外部多功能IO来选择之外,易灵思通过内部重配置实现远程更新操作也非常简单。

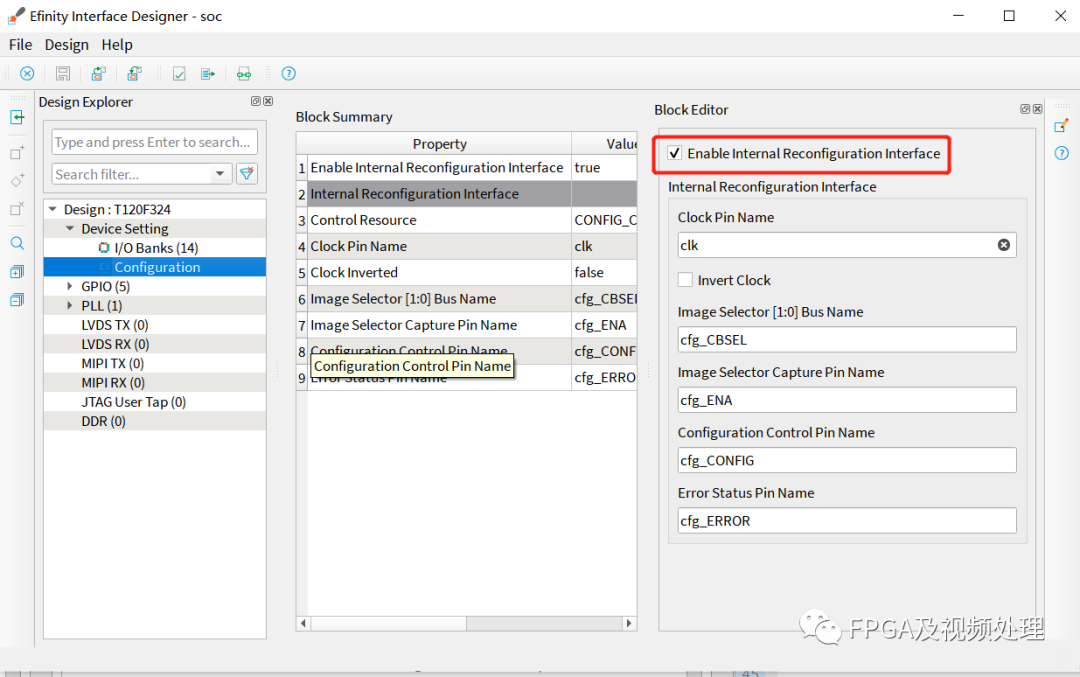

(1)使能内部重配置接口

1、在interface Designer中选择Device Setting ->Configuration

2、打开EnableInternalReconfigurationInterface

3、生成例化接口添加到top文件。

关于重配置接口就以下几个信号

inputcfg_ERROR, output[1:0]cfg_CBSEL, outputcfg_CONFIG, outputcfg_ENA

其中_CBSEL就是选择那个image的。ENA拉高就可以启动相应image加载。

(2)重配置过程操作

1、通过_CBSEL选择相应的image;

2、拉高_ENA;

3、使能_CONFIG为高;

4、如果_ERROR为0重配置成功。

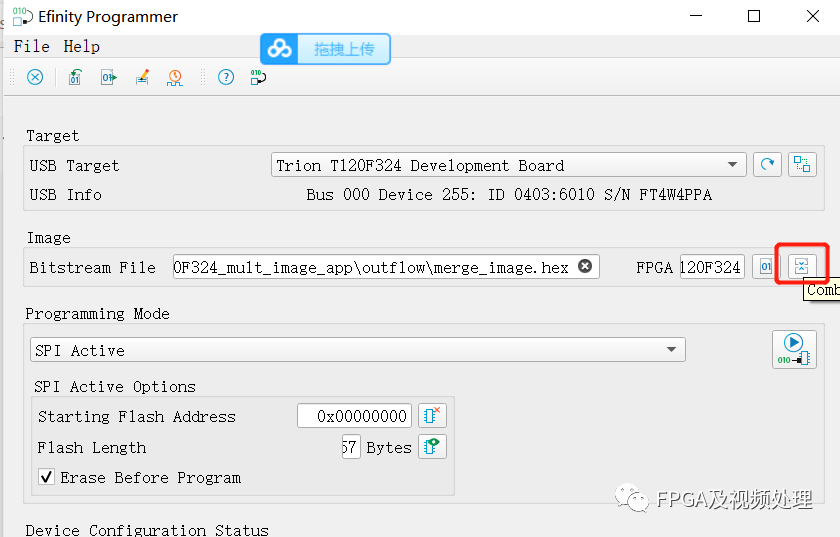

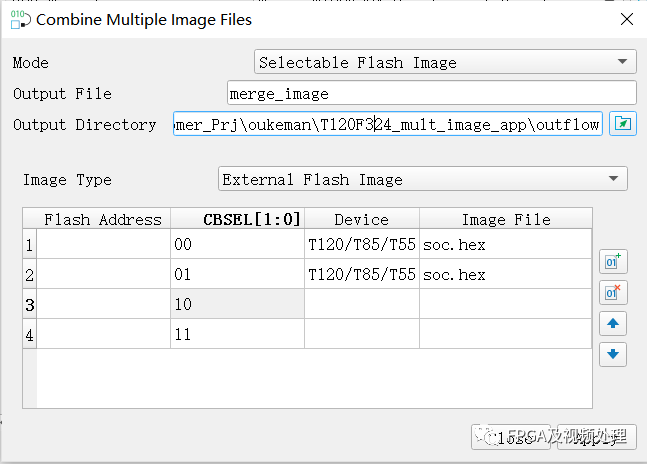

(3)组合image文件的生成

1、在Efinity Programmer中,点击combine multiple Image Files项。

(2)在CBSEL为00的地方添加golden image,其余添加APP_image即可以,地址如果不给定,会自动分配。填写输出文件,点击apply生成即可。

更详细的信号请参考易灵思AN010.

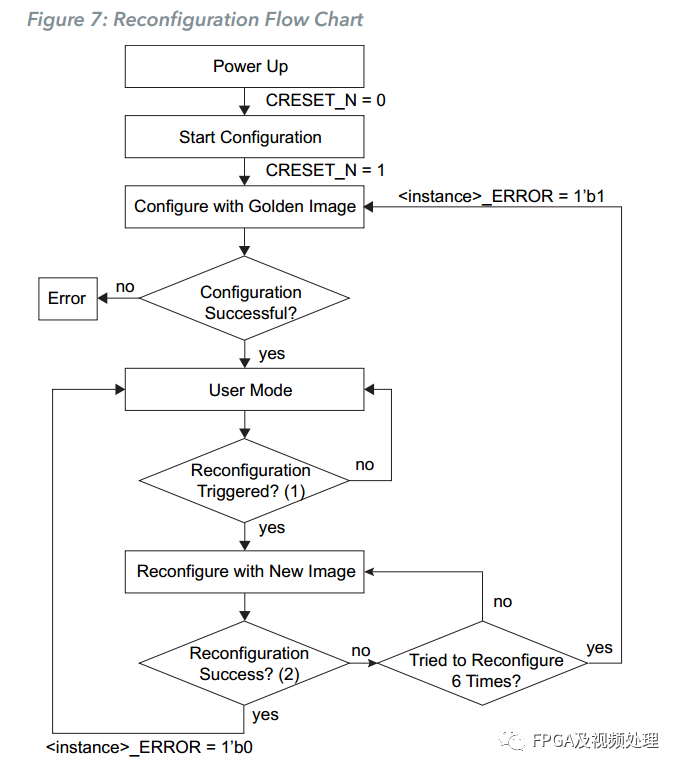

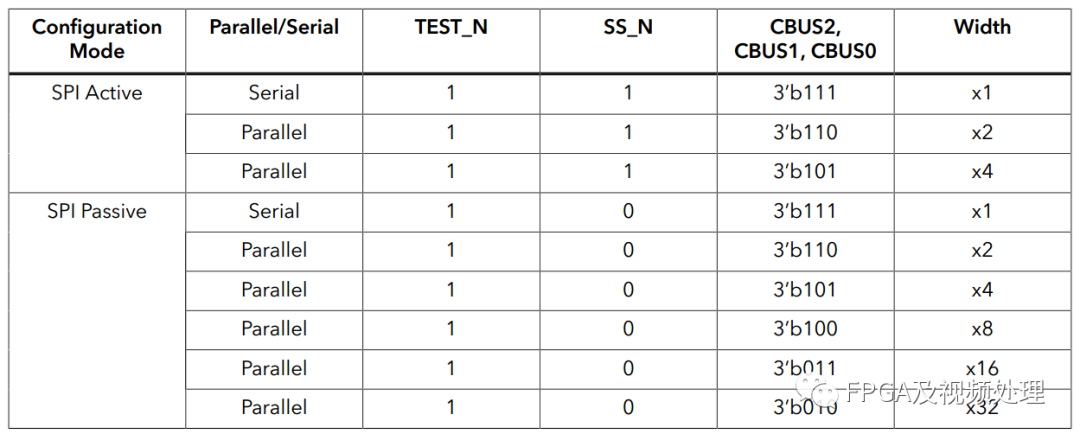

1、通过内部重配置远程更新也要注意在上电时外部CSEL管脚的状态,如果没有指向goden image或者app image,那么会要等待一段时间,文档说应该会加载6次,大概41s。

2、下面是重配置流程图。

(1)上电之后,CRESET_N上升沿触发配置过程。

(2)golden image加载完成之后进入user mode;

(3)用户启动重配置触发,配置新image;

(4)如果配置成功则进入user mode,如果没有配置成功则会加载6次;

(5)6次之后_ERROR拉高,并再次加载golden image;

(6)如果不想反复以上操作可以通过检测_ERROR来禁止下次的New image配置触发。

下面提供一个demo,CONFIG只需要拉高一个时钟周期即可

审核编辑:汤梓红

-

接口

+关注

关注

33文章

8691浏览量

151824 -

流程图

+关注

关注

2文章

63浏览量

18789 -

触发

+关注

关注

1文章

89浏览量

22668 -

远程更新

+关注

关注

0文章

8浏览量

7624 -

易灵思

+关注

关注

5文章

48浏览量

4924

原文标题:易灵思内部重配置实现远程更新 -v1

文章出处:【微信号:gh_ea2445df5d2a,微信公众号:FPGA及视频处理】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

赛灵思发布ISE12.2强化部分可重配置FPGA技术

赛灵思公司在2017年闪存峰会上展示可重配置存储加速解决方案

采用FPGA实现DisplayPort详细教程【赛灵思内部资料】

Xilinx的可重配置加速堆栈为云级应用提供业界最高计算效率

谈谈赛灵思的局部重配置技术

赛灵思可重配置加速堆栈方案,旨在快速开发和部署加速平台

基于SRAM的可重配置电路PLD

赛灵思的局部重配置技术(Partial Reconfiguration)

易灵思IDE更新ROM可以不用全编译了

易灵思FPGA软件更新的节奏,也许能磨出一个好产品

易灵思内部重配置实现远程更新

易灵思内部重配置实现远程更新

评论