1 引言

芯片是推动信息社会蓬勃发展的基石,掌握高端 芯片的制造技术关乎国家未来在人工智能、高性能计 算、5G/6G通信和万物互联等关键领域的全球竞争力。由于集成电路的纳米制程工艺逐渐逼近物理极限,通 过芯片三维异质集成来延续和拓展摩尔定律的重要 性日趋凸显。异质集成以需求为导向,将分立的处 理器、存储器和传感器等不同尺寸、功能和类型的芯 片,在三维方向上实现灵活的模块化整合与系统集成。此时,如何实现互连芯片之间高带宽、低延迟和低损 耗的信号传输,成为突破高端芯片内存墙、速度墙和 功耗墙等瓶颈的关键。据台积电测算,若芯片堆叠 的垂直互连间距从现有的36μm降至0.9μm,互连密 度至少可增加3个数量级,实现10倍以上的通信速 度、20倍的能源效率和近2万倍的带宽密度提升。以 芯片封装互连密度来表述的摩尔定律也获得了广泛 共识。由此可见,高密度三维互连技术将成为未来推 动芯片持续向高性能和微型化发展的关键引擎。

随着芯片模块化思想及芯粒(Chiplet,一类在独立 裸片上设计、采用不同工艺制程制作并可复用集成的 芯片)技术的提出和发展,芯片设计、工艺制程和封装 测试由单片一体化向多模块灵活整合发展,因此封装技术需进行相应的深度开发和模块化整合。21世纪 以来,美国国防部高级研究计划局(DARPA)、欧洲微 电子研究中心(IMEC)、德国Fraunhofer、法国Leti、新 加坡IME、美国麻省理工学院、佐治亚理工学院等单 位均陆续投入大量资源,开展深入的三维异质集成研 发工作。加入封装交流群,加VX:tuoke08。这些顶尖研究机构借助系统集成方面的基础 优势,针对多芯片三维异质集成技术的开发一直走在 世界前列。值得注意的是,2022年初,英特尔、台积 电、三星、高通、谷歌等行业领先企业成立了通用Chiplet高密度互连联盟(UCIe),旨在整合推广三维芯片 互连及异质集成的技术标准并构建完善生态,这也标志 着异质集成技术进入了发展及产业应用的关键阶段。

事实上,异质集成技术开发与整合的关键在于融合实现多尺度、多维度的芯片互连,从而提高带宽和电源效率并减小延迟,为高性能计算、人工智能和智 慧终端等提供更小尺寸和更高性能的芯片。芯片的垂 直方向互连依赖硅通孔(TSV)或玻璃通孔(TGV)等技 术,水平方向上通过再布线层(RDL)技术进行互连。本 文综述了TSV、TGV、RDL等芯片三维互连技术,分析基于这些互连技术的三维异质集成方案及应用,阐述 当前研究现状,并探讨存在的技术难点及未来发展趋势。

2芯片三维互连技术

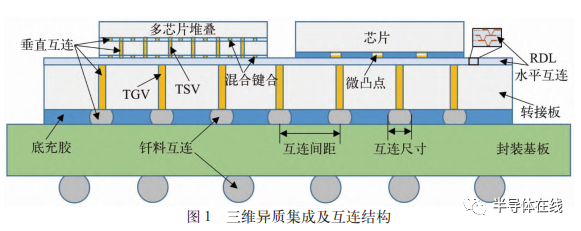

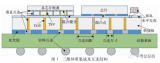

通过垂直方向上的TSV/TGV技术与水平方向上 的RDL技术的配合,对芯片进行三维互连,可将不同 尺寸、材料、制程和功能的Chiplet异质集成到1个封 装体中,形成的三维异质集成及互连结构如图1所示。

2.1 TSV 技术

TSV主要用于实现垂直方向上的信号连接,其中Cu-TSV的应用最为广泛。典型的Cu-TSV制造工艺包 括以下关键步骤:深孔刻蚀、形成绝缘层/粘附阻挡层/种子层、电镀Cu填充、去除多余Cu及背面的TSV-Cu外露。目前用于三维异质集成的TSV直径约为10μm,深宽比约为10∶1。与半导体领域的其他技术发 展方向类似,TSV的直径、间距和深度等关键尺寸亟 需缩小。TSV直径的减小,不但能够减少其占用面积、 提高互连密度,还可以显著减少Cu-TSV附近的应力, 避免影响器件性能。根据TSV的直径及深宽比的路线 图,未来先进TSV工艺的直径有望减小到1μm,深宽 比达到20∶1。国际上重要的半导体科研机构和领先 企业已经开始研究亚微米直径的TSV技术。

细小直径、高深宽比的TSV加工的主要难点包括 如何形成连续均匀的绝缘层/粘附阻挡层/种子层和 无缺陷的超共形电镀Cu填充等。由于物理气相沉积 (PVD)、化学气相沉积(CVD)在微米尺度深孔内覆盖 率低,通过PVD、CVD沉积绝缘层、粘附阻挡层和种 子层不利于TSV尺寸的进一步缩小。原子层沉积 (ALD)可制备小直径、高深宽比的共形薄层,成为突 破PVD工艺瓶颈的关键技术。ALD具有的优势包括:较低的工艺温度,比现有CVD及PVD工艺更好的深 孔覆盖能力,介质沉积前无需表面处理,更薄的介质 层减少了TSV的抛光处理时间。2015年,IMEC报道 了直径为3μm、深度为50μm的TSV制造工艺,采用ALD沉积氧化绝缘层、WN扩散阻挡层,利用化学镀NiB作为电镀种子层,快速深孔电镀工艺实现TSV填 充。日本学者研究了直径为2μm、深度为30μm的TSV结构,在ALD-Ru、ALD-W上化学镀沉积铜,然后 完成TSV电镀铜填充,化学镀铜和ALD-Ru之间的结 合强度大于100 MPa。然而,当前工艺探索和研究 还缺乏系统性,深孔电镀/化学镀填充、ALD沉积形 成多界面材料和结构的电学特性、可靠性以及失效机 理都还需要深入研究。

2.2 TGV 技术

TGV作为TSV的低成本替代方案,逐渐受到广 泛关注。TGV无需沉积绝缘层,具有高频电学特性优 良、工艺流程简单的特点。此外,玻璃的机械稳定性 强、翘曲小且成本低,大尺寸玻璃易于获取。TGV在射 频组件、光电集成和MEMS器件等三维封装领域具有 广阔的应用前景。

以盲孔为例的TGV的工艺流程包括:首先制备TGV盲孔;其次通过物理气相沉积的方法在TGV盲 孔内部沉积Ti/Cu种子层(工艺温度为250~400℃);接着利用TGV深孔电镀,自底而上进行孔内填充,实 现TGV无孔洞填充并退火。近年来,关于TGV的成 孔方法被广泛研究报道,如喷砂法、光敏玻璃法、等离 子刻蚀法、激光烧蚀和激光诱导湿法刻蚀法等。其 中,激光诱导湿法刻蚀技术具有快速高效成孔、工艺 简单、侧壁光滑、高精度成孔等显著优点,被广泛应用 于各种玻璃材料的三维微流道加工。2014年,德国LPKF公司的OSTHOLT等人利用激光诱导湿法刻 蚀技术率先制备出应用于玻璃三维集成的TGV。结果 显示,对于厚度为50~200μm的玻璃,通过改变氢氟 酸(HF)蚀刻参数可以得到直径为10~50μm、节距不 小于50μm的TGV。然而,其侧壁垂直度较差,锥度均 大于5°,对电学性能及可靠性都有负面影响。另外,TGV的深宽比往往可决定芯片的集成度,该方法制备 的TGV深宽比一般不大于6∶1,远小于先进TSV工艺 所能达到的20∶1。CHEN等人采用皮秒激光对硼硅 酸盐玻璃进行改性时,发现在激光束传播路径的影响 区出现的一系列纳米孔洞增强了玻璃样品在HF溶液 中的选择性蚀刻能力。通过调节激光脉冲和HF溶液 浓度等,可针对特定成分的玻璃改善TGV侧壁垂直 度。刻蚀液选择性蚀刻的原因及蚀刻速率随激光脉冲 能量改变的机理仍有待阐明;超/兆声振动、温度和蚀 刻液浓度等因素及多场耦合对蚀刻速率和选择比的 影响等重要问题仍未得到研究。

目前,垂直TGV通孔的电镀填充方式一般为蝶 形填充,其与TSV硅基半导体工艺自下而上的盲孔电 镀填充具有本质差别[20]。与盲孔填充相比,通孔填充在 流体力学与质量传输方面均存在明显差异。盲孔填充 时,镀液在孔内很难流动;而在通孔内部,镀液可以流 动从而加强内部的传质。且通孔与盲孔的几何形状不 同,没有盲孔底部,不会产生自下而上的填充方式。TGV通孔与盲孔在几何形状、流场、质量传输等方面 的差异,导致用于盲孔填充的电镀配方及工艺无法直 接用于TGV通孔。另一方面,由于TGV的直径、深宽 比、表面粗糙度及垂直度等均与印制电路板(PCB)通 孔有显著差异,现有通孔填充理论应用于TGV电镀 填充具有很大的局限性,需综合考虑电流密度、添加 剂、流场和传质等多因素耦合,但目前仍缺乏相关研究。

TGV、TSV以外,通模通孔(TMV)、封装通孔 (TPV)等技术也是满足微电子封装高密度和多功能要 求的潜在解决方案。TMV是一种在封装尺度上的 工艺,通过垂直通孔与RDL技术,可有效地为封装上 封装(PoP)与多芯片嵌入式堆叠封装中的不同封装提 供垂直互连。目前用于垂直互连的TMV孔径一般为25~150μm,深度为100~1 000μm。此外,获得高质量 的TMV仍需解决制备TMV过程中管壁平整度、通孔 中的残渣和散热导致的芯片与模具分层等问题。具有细间距TPV的薄玻璃中介层因其具有绝缘性能、大 面板可用性和与硅匹配的热膨胀系数,而能够作为3D集成的低成本和高I/O基板。在玻璃上实现TPV的 一般方法有激光烧蚀法、深反应离子蚀刻及光化学蚀刻法。作为TSV的替代方案,实现更小尺寸的TPV直 径与金属化仍需深入研究。

2.3 RDL 技术

RDL是实现芯片水平方向互连的关键技术,可将 芯片上原来设计的I/O焊盘位置通过晶圆级金属布线 工艺变换位置和排列,形成新的互连结构。借鉴PCB铜布线工艺,RDL可通过加成法、半加成法等方法加工。典型的RDL半加成工艺包括:(1)形成钝化绝缘 层并开口;(2)沉积粘附层和种子层;(3)光刻显影形成 线路图案并电镀填充;(4)去除光刻胶并刻蚀粘附层和 种子层;(5)重复上述步骤进行下一层的RDL布线。高 密度的RDL布线可借鉴半导体铜互连的大马士革工 艺进行加工,引入化学机械抛光进行平坦化,并去除 多余的铜及粘附层/种子层。

目前,高密度互连有机RDL线宽/线间距(L/S)约 为6μm,微孔直径为20μm、间距为50μm,可实现每 平方毫米每层约40个I/O的密度。然而,为了进一 步提高I/O密度,需要具有1μm线宽/线间距以及1~ 2μm直径微孔的RDL。RDL技术的进步对于实现高 密度、高带宽(每平方毫米每层超过500个I/O、带宽 大于500 Gbit/s)的芯片互连具有极为重要的意义。高 密度RDL有4个关键问题:(1)细线条光刻L/S为1μm;(2) 微孔加工是限制RDL实现高I/O密度和精 细I/O间距的最主要的障碍;(3)低介电常数和低耗损 因子的介电材料;(4) 半加成法是实现高密度RDL的 普遍工艺。

3 基于 TSV 及 RDL 的异质集成方案

经过多年发展,TSV封装技术的发展经历了从TSV简单互连、2.5D TSV转接板、微凸点3D集成到 目前最为关注的无凸点3D集成。从应用的角度看,已 进入量产的基于TSV的封装技术主要集中在高端可 编程器件、图像处理器、存储芯片以及传感器芯片等 领域。

3.1基于TSV及RDL互连的晶圆级封装

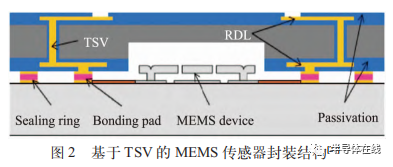

用TSV简单互连代替引线键合,实现硅背面与正 面有源区或金属布线之间的电气导通,是TSV在批量 生产中的首次使用。其典型应用包括图像、指纹、滤波 器、加速度计在内的传感器的封装,基于TSV的MEMS传感器封装结构如图2所示。使用TSV可减 小传感器模块的封装尺寸,利于进行晶圆级封装,提 高生产效率并降低成本。近年来发展出的基于后通孔TSV的埋入硅基三维异质集成技术,提供了1种低成 本、高性能的异质集成方案。2016年,华天科技有限公 司开发出硅基埋入扇出(eSiFO)技术,使用硅片作为 载体,将芯片置于在12英寸硅晶圆上制作的高精度凹 槽内,重构出1个晶圆;然后采用可光刻聚合物材料填 充芯片和晶圆之间的间隙,在芯片和硅片表面形成扇 出的钝化平面;再通过光刻打开钝化层开口,并采用 晶圆级工艺进行布线和互连封装。硅基埋入封装具有 超小的封装尺寸、工艺简单、易于进行系统封装和高 密度三维集成等优点。同时,可通过制备背面RDL和Via-last TSV,实现异质集成多芯片的三维堆叠封 装。其基本工艺流程包括:将测试正常的芯片嵌入单 个eSiFO封装体,然后分别在eSiFO封装体的正面和 背面形成RDL,再通过微凸点和Via-last TSV实现多 个独立的eSiFO封装体与嵌入式芯片之间的电信号 互连。eSiFO技术可以将由不同设计公司、晶圆厂设计 制造的各种晶圆尺寸和特征尺寸的不同系统或不同 功能的芯片集成到1个芯片中,从而实现真正的不同 封装体之间的三维异质集成封装。

3.2 2.5D TSV转接板异质集成

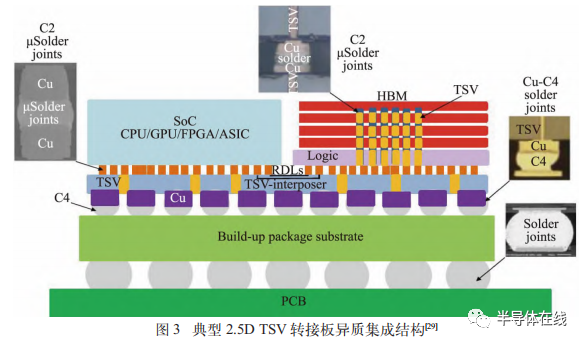

2.5D TSV转接板技术是为解决有机基板布线密 度不足、信号延迟大、带宽限制等问题而开发的带有TSV垂直互连通孔和高密度金属布线的新型基板技 术。通过带有TSV垂直互连通孔的无源或有源载板,实现多个芯片间的高密度连接,再与有机基板互连以 提高系统集成密度,解决芯片管脚密度与有机基板引 出结构无法兼容的问题。典型2.5D TSV转接板异质 集成结构如图3所示,采用TSV及微凸点(包括可 控塌陷C4凸点和铜柱C2凸点)实现垂直互连,通过 高密度RDL实现水平互连,实现中央处理器(CPU)、 图形处理器(GPU)、高带宽内存(HBM)等Chiplet的 异质集成。

IMEC、Fraunhofer、Leti、IME、台积电、联电等半导 体顶尖研究机构和企业均陆续推出各自的2.5D TSV转接板异质集成方案。其中,台积电于2011年推出的2.5D封装衬底上晶圆级芯片封装(CoWoS)技术最具 代表性,并成功实现大规模量产。该技术通过芯片到 晶圆工艺将芯片连接至硅转接板上,再把堆叠芯片与 基板连接,实现芯片-转接板-基板的三维封装结 构。该技术采用前道工艺在转接板上制作高密度的互 连线,通过转接板完成多个芯片的互连,可以大幅提 高系统集成密度,降低封装厚度。基于台积电的CoWoS技术,Xilinx推出“Virtex-7 2000T”产品,该产 品将4个采用28 nm工 艺的现场可编程 门 阵 列 (FPGA) 芯片通过TSV转接板互连,实现了在单个FPGA模组里集成数个FPGA的功能,超越了摩尔定 律的限制[31]。此后推出的基于CoWoS技术的产品包括 华为海思Hi616、英伟达TESLA显卡和Fujistu A64FX超级计算芯片等。针对高性能计算应用,台积电于2020年进一步开发了集成深沟槽电容 (DTC)的CoWoS技术,其电容密度高达300 nF/mm2,漏电流小 于1 fA/μm2,该CoWoS具有更低的功耗和更好的数 据传输性能。到2021年,CoWoS技术已经发展至第 五代,转接板面积可达2 500 mm2,单个转接板可集 成8个HBM和超过3个芯片级系统(SoC)/Chiplet模 块;同时集成DTC以增强电源完整性,并发展出相应 的5层亚微米尺度的铜RDL互连技术。近年来,人工 智能、高性能计算等对超强算力的需求迅猛增长,大 力推动了2.5D TSV转接板封装技术的应用。通过异 质集成CPU、GPU和HBM获得更高的带宽密度,成 为提高算力的关键途径。根据对TOP500超级计算机 系统的分析,2020年基于CoWoS技术的总计算能力 占所有TOP500系统总计算能力的50%以上。

3.3基于TSV和微凸点的三维异质集成

3D集成将芯片在垂直方向通过TSV和微凸点进 行堆叠,可以实现高性能、低功耗、高宽带、小形状因 子等目的,充分发挥晶圆级堆叠和TSV技术互连线长 度短的优势。该技术早期主要应用于动态随机存取存 储器(DRAM)、高带宽内存等。典型产品如2014年三 星基于TSV和微凸点互连量产的64 GB DRAM,互连TSV尺寸为7μm×50μm;与采用引线键合的内存相 比,信号传送速率提升一倍,而功耗减少一半。

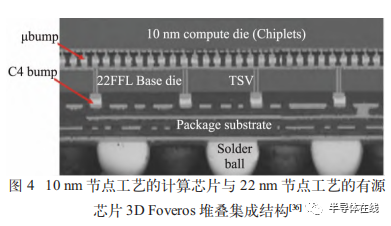

近年来,基于TSV和微凸点的三维集成技术不断 拓展到逻辑芯片的三维堆叠集成。2019年,英特尔推 出基于TSV和微凸点的新型3D集成技术Foveros,该 技术能够实现逻辑芯片的面对面堆叠,首次将芯片堆 叠从传统的无源中介层和内存等扩展到高性能逻辑 芯片,例如CPU、GPU和AI处理器等。10 nm节 点工艺的计算芯片与22 nm节点工艺的有源芯片3D Foveros堆叠集成结构如图4所示。采用Foveros封 装技术的英特尔Lakefield处理器于2020年投入市场。三星也于2020年发布了X-Cube三维集成技术,利用TSV和微凸点技术将HBM芯片与逻辑芯片进行堆 叠,在速度、功率、效率方面实现显著飞跃。

3.4基于无凸点混合键合的三维异质集成

一直以来,3D集成广泛采用Sn基钎料微凸点和TSV实现高效的垂直互连。然而,当间距减小到20μm以内,热压键合过程中的细微倾斜将使钎料变形挤出 而发生桥连短路。同时,液-固反应形成的金属间化合 物(IMC)将占据凸点的大部分体积,使之转变为脆性 连接。并且,表面扩散及柯肯达尔孔洞等问题的影响 急剧增加,难以进一步缩减互连间距,微凸点的微型 化遭遇前所未有的瓶颈。基于Cu/绝缘层混合键合的无凸点3D集成可实现:(1)刚性互连,避免出现桥 连问题;(2) 与集成电路后道工序及TSV铜互连相兼 容,无需底充胶;(3)芯片堆叠中多次热压工艺无影响 (铜的熔点为1 083℃);(4) 无脆性相IMC形成;(5) 优异的电、热、机械和抗电迁移性能。因此,无凸点Cu/绝缘层混合键合在超细间距(小于10μm)芯片垂直互 连中的应用具有无可比拟的优势。

对于Cu-Cu直接键合及Cu/绝缘层混合键合的 研究已持续了几十年,然而由于当时的市场需求有限 并且工艺难度过大,其一直未引起过多关注。直到2015年,索尼获得Ziptronix公司的混合键合技术授 权,首次推出了基于无凸点混合键合的高性能图像传 感器产品。半导体业界逐渐意识到混合键合将成为 突破微凸点微型化瓶颈的有效途径。此后英特尔、台 积电、华为、长江存储、IMEC、IME、Leti等领先机构和 企业陆续对混合键合技术进行了深入研发。英特尔 推出了基于无凸点混合键合的Foveros三维集成技 术,但未披露过多细节。台积电则较为详细地公布了 其基于无凸点混合键合的三维异质集成技术,将之称 为集成片上系统(SoIC),其混合键合工艺温度与 无铅焊料回流工艺温度相当。SoIC集成采用超薄芯 片,以实现大深宽比和高密度的TSV互连。为此,台积 电提出并优化2条工艺路线:(1)芯片-晶圆键合后再 背面露铜,首先将芯片面对面混合键合,随后对芯片 背面减薄,背面露铜后沉积绝缘层和Cu盘,再次与另 一芯片Cu-Cu键合并重复以上工艺,实现芯片堆叠;(2)背面露铜后再进行芯片-芯片键合,首先将晶圆临 时键合于玻璃载板并进行背面减薄,背面露铜后沉积 绝缘层和Cu盘,晶圆与载板解键合后切割成单颗芯 片,单颗芯片再分别进行Cu-Cu键合以实现芯片堆 叠。基于混合键合的SoIC及其改进版本SoIC+可以 获得超细间距和超高密度的互连。它比倒装芯片技术 具有更好的电气性能,插入损耗几乎为零,远远小于2D并排倒装芯片技术的插入损耗。与台积电采用的传 统微凸点3D TSV集成对比,无凸点SoIC集成的12层存储器在垂直方向上的尺寸下降高达64%,带宽密 度则增加28%,而能源消耗下降19%。

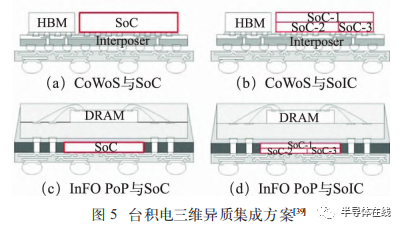

由此可见,无凸点3D集成技术可实现超高密度 的芯片垂直互连,继续推动芯片向高性能、微型化和 低功耗方向发展。同时,以台积电无凸点3D集成SoIC技术为例,SoIC可与CoWoS、集成扇出型封装等技术 实现深度异质集成整合,三维异质集成方案如图5所 示。原来需要放到1个片上系统SoC芯片上实现的 方案,现在可以转换成多个Chiplet来做。这些分解开 的Chiplet再通过集成SoIC实现灵活整合,其芯片产 品具有设计成本低、速度快、带宽足和低功耗的优势。因此,基于无凸点混合键合的三维异质集成技术若真 正实现量产,无疑是集成电路行业划时代的革新技 术。然而,当前该技术在设计规则、平整度、清洁度、材 料选择和对准等方面仍面临诸多挑战。

4基于玻璃基板的异质集成方案

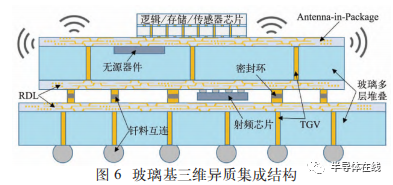

玻璃基板具有较多优势:玻璃的低损耗使其传输 性能优良,高平整度的表面可以进行细间距的布线, 以及可调的热膨胀系数使得异质集成的应力问题减 少。TGV的加工比TSV更为简单高效,机械、激光或 刻蚀等方法组合使用,均可批量进行玻璃打孔。由于 玻璃本身的绝缘特性,仅需沉积粘附层与种子层即可 进行电镀填充。同时,玻璃基板封装可以通过玻璃面板级工艺进行大批量的制造,具有成本优势。玻璃基 三维异质集成结构如图6所示。

4.1基于TGV及RDL的异质集成

佐治亚理工学院在2014年提出的三维极薄玻璃 转接板厚度约为30~50μm,转接板位于三维堆叠存 储芯片与逻辑芯片之间,取消了逻辑芯片的TSV通 孔,其TGV间距为20~50μm,与3D-IC中所需的TSV间距一致。与此同时,TGV展示出了更低的插入 损耗、更小的延时和串扰。三维极薄玻璃转接板技术 可有效地降低成本及工艺难度,提升转接板整体性能 并降低整体厚度。欣兴电子在2014年提出玻璃转接板 嵌入式载板,将厚度为100μm、孔径为30μm的玻 璃转接板埋入层压板后进行标准的层压板工艺,实现 转接板与层压板的互连。此结构减少了焊球数量,在 使整体封装结构更薄的同时减少了底填所带来的热 膨胀问题,可以减少传统工艺中转接板与基板组装造 成的损耗,采用镀铜而不是焊料连接的方式将转接板 与基板直接连接,可以提高可靠性和电性能。2016年, 格罗方德、IBM以及加州大学伯克利分校联合发表了 针对系统小型化的端到端集成的多芯片玻璃转接板 方案。该方案的TGV最终高度为55μm,上、下直径 分别为25μm和12μm,在芯片键合端采用大马士革工 艺制造最小特征尺寸为2.5μm的金属布线。这项工作成 功地将TSV转接板的设计方案复刻到TGV转接板中, 在转接板的上方利用大马士革工艺制造精细铜布线。

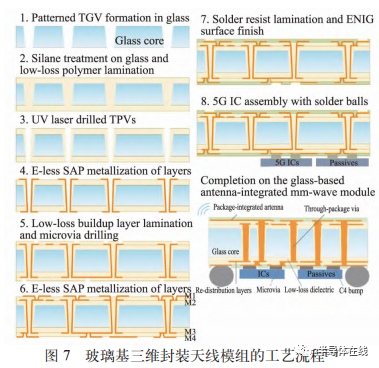

2020年,佐治亚理工学院发表了28 GHz频段的 面板级超薄玻璃基片上的AiP异质集成,玻璃基三 维封装天线模组的工艺流程如图7所示。在玻璃基 板上制作的八木-宇田天线,其中心频率为25.85 GHz, 分数带宽为28.2%,覆盖了28 GHz频段,基板的背面 集成了有源集成电路以及离散无源组件。天线在目标 频率范围内还具有广角主瓣,具备良好的信号发射和 接收覆盖能力。模块级表征结果显示其具有低互连信 号损耗,在28 GHz时TPV损耗为0.021 dB。此项工作 表明玻璃基AiP异质集成可以为毫米波通信模组提 供1个高性能的解决方案。本文作者团队探索了多 层玻璃的天线集成技术,采用激光诱导湿法刻蚀玻璃 技术制备TGV,随后在玻璃表面进行金属布线,并采 用钎料进行多层玻璃堆叠键合,开发出采用5层玻璃 堆叠的方案,制作工作频段在75~90 GHz的天线。辐 射部分由4个微带贴片组成,封装总尺寸为10 mm×9 mm×1 mm。TGV和RDL形成的互连可实现层间的 直接传输和信号耦合,以提高传输效率。此外,低介电 常数确保了玻璃的微弱表面波效应。实验和仿真结果 表明,该系统的回波损耗小于25 dB,增益大于7 dBi。

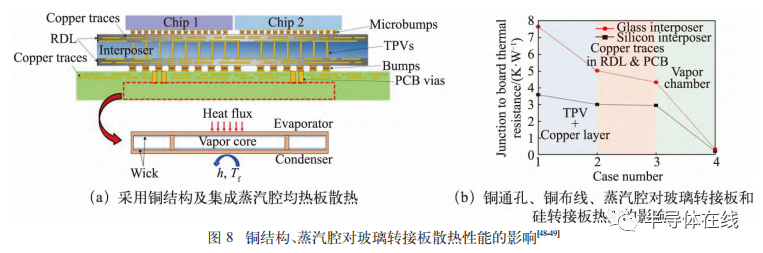

然而,玻璃的主要问题在于导热系数低导致的散 热不良。CHO等人研究发现,玻璃转接板通孔、接 地铜结构等可提供有效的热传导途径,引入大量铜通 孔、铜布线等结构可以显著提高玻璃转接板的散热性 能,同时可实现在硅材料中难以实现的逻辑器件和存 储器件之间的良好热隔离。在PCB中引入蒸汽腔均热 板可以进一步提高散热性能,克服玻璃的低热导率问 题,获得和硅转接板几乎相当的散热性能。铜结构、蒸 汽腔对玻璃转接板散热性能的影响如图8所示。

4.2埋入玻璃式扇出型异质集成

佐治亚理工学院在2019年针对高效高带宽异质 集成发表了TGV三维封装方案———嵌入平板玻璃技 术,实现了逻辑芯片和存储芯片的面对面式三维集 成。100μm厚度的逻辑芯片被埋入110μm深度的玻 璃盲槽中,并将介质真空压入芯片与盲槽的侧壁间, 再用光刻打开开口,实现其与存储芯片的直接互连。相较于目前的2.5D封装结构和3D-IC,这种结构有着 更高的I/O密度、更佳的性能、更低的成本以及更好的 可靠性。该种结构无需对处理器芯片进行TSV工艺,同 时可实现超短互连和高效的超高带宽,具有较大的潜力。

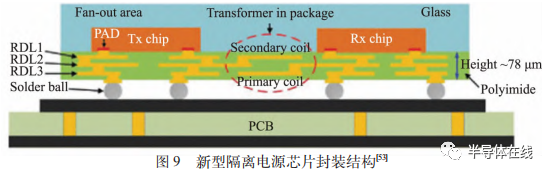

本文作者研究团队基于玻璃成孔工艺开发了埋 入玻璃式扇出型(eGFO)异质集成技术,并成功应用于 电源芯片、滤波器、超声换能器、毫米波雷达天线等集成封装。其中新型隔离电源芯片封装结构如图9所 示,基于eGFO异质集成技术将接收和发射线圈通过 封装表面上的RDL制成的微型变压器异质集成在一 起。电源芯片实现了46.5%的峰值转换效率和最大1.25 W的输出功率,而封装尺寸仅有5 mm×5 mm,在 目前所报道的无磁芯隔离电源芯片中效率和功率密 度均为最高。针对超声换能器阵列不耐高温的特性, 团队开发了低温RDL优先的eGFO技术。通过临时 键合在载板上制作3层RDL及铜柱凸点,使用低固化 温度的各向异性导电胶实现超声换能器阵列与临时 玻璃基板之间的电学连接;以玻璃代替有机塑膜材 料,通过胶带转移法制作了包含超声换能器阵列器件 的重构晶圆;通过晶圆级键合实现了超声换能器阵列 与临时玻璃基板之间的批量键合,避免了在长期预热 条件下的失效问题。

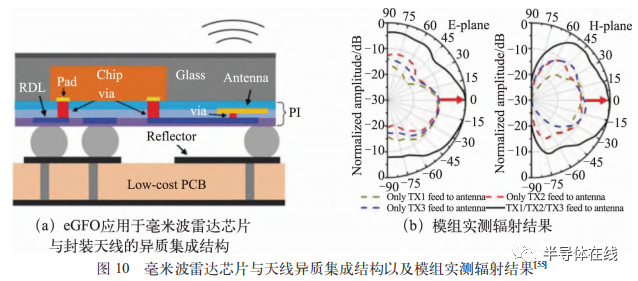

同时,eGFO还可应用于毫米波雷达芯片和封装 天线的异质集成,其结构如图10(a)所示,模组实测 辐射结果如图10(b)所示。仿真及实测结果表明,接收 天线阵列实现了10.5 dBi的增益,发射天线阵列实现 了9 dBi的增益。基于此技术,中国电子科技集团公司 第三十八研究所在ISSCC 2021国际固态电路会议上 发布了一款高性能的77 GHz毫米波芯片及模组,其 集成封装尺寸仅为23.1 mm×10.7 mm×220μm,在国际 上首次实现2颗3发4收毫米波芯片及10路毫米波 天线单封装集成,其探测距离达到38.5 m,刷新了全球 毫米波封装天线最远探测距离的新纪录。

5 结束语

异质集成技术开发与整合的关键在于融合实现 多尺度、多维度的芯片互连,芯片在垂直方向上的TSV、TGV互连技术与水平方向上的RDL互连技术 相配合,可将不同尺寸、材料、制程和功能的Chiplet异 质集成整合到1个封装体中,从而提高带宽、延迟和电 源效率,为高性能计算、人工智能和智慧终端等提供 更小尺寸和更高性能的芯片。

TSV作为三维异质集成的核心技术,其关键尺寸 需要不断地缩小,细小直径、高深宽比TSV加工的主 要难点包括:形成连续均匀的绝缘层/粘附阻挡层/种子层和无缺陷的超共形电镀Cu填充等。通过TSV与RDL互连技术的融合,基于TSV互连的晶圆级封 装、2.5D TSV转接板、微凸点3D集成和无凸点3D集 成等异质集成方案相继被推出,并在高端可编程器 件、图像处理器、存储芯片以及传感器芯片等领域实 现量产。

目前,无凸点3D集成技术可实现超高带宽密度 的芯片垂直互连,并可与其他封装技术实现深度异质 集成整合,将分解开的Chiplet互连封装成片上集成系 统,在降低芯片设计成本和芯片功耗的同时提升带宽 和计算速度。基于无凸点混合键合的三维异质集成技 术若真正实现量产,无疑是集成电路行业划时代的革新技术。然而,当前该技术在界面设计规则、平整度、 清洁度和材料选择等方面仍面临诸多挑战。

基于玻璃TGV的转接板异质集成的优势包括:玻璃表面较高的平整度可以进行细间距的RDL布线;玻璃的低损耗特性使得TGV/RDL传输性能优良;玻 璃具有可调的热膨胀系数,使得异质集成应力问题减 少;同时玻璃转接板可以通过玻璃面板级工艺进行大 批量制造而具有成本优势。因此,这一技术在5G通讯 射频器件、无源器件、MEMS器件等领域具有广阔的 应用前景。

审核编辑:刘清

-

传感器

+关注

关注

2551文章

51171浏览量

754220 -

PCB板

+关注

关注

27文章

1448浏览量

51698 -

MEMS器件

+关注

关注

2文章

46浏览量

12912 -

TSV封装

+关注

关注

0文章

12浏览量

2371

原文标题:芯片三维互连技术及异质集成研究进展

文章出处:【微信号:半导体封装工程师之家,微信公众号:半导体封装工程师之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于弹性互连的三维射频前端模组的设计

新型铜互连方法—电化学机械抛光技术研究进展

薄膜锂电池的研究进展

世界级专家为你解读:晶圆级三维系统集成技术

光互连技术的研究进展

基于LTCC技术的三维集成微波组件

芯片三维互连技术及异质集成研究进展

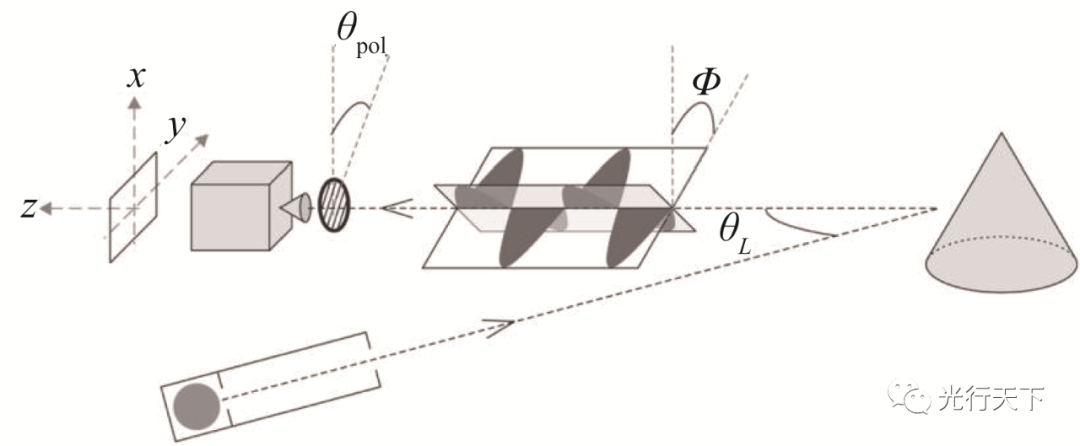

偏振三维成像技术的原理和研究进展

芯片三维互连技术及异质集成研究进展

芯片三维互连技术及异质集成研究进展

评论