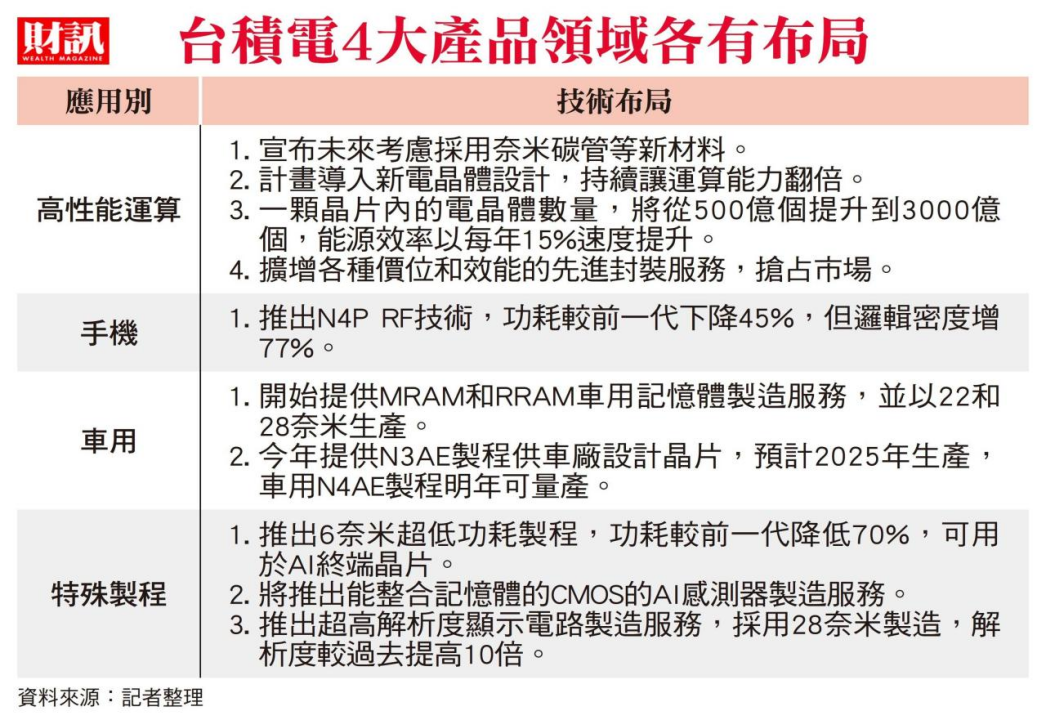

今年台积电技术论坛上,揭露了2nm后的发展路径图,特殊制程和先进封装将扮演更重要角色。

今年下半年,台积电将开始用3nm制程为苹果制造芯片,接下来2nm制程也将在2025年推出。但随着半导体线宽微缩越来越逼进物理极限,台积电还能继续维持高速成长,甩开对手吗?

后摩尔定律时代局势大变

对台积电的长期投资者来说,另一个挑战是,数十年来推动半导体产业前进的摩尔定律,效用似乎逐渐降低。过去,半导体产业每隔一段时间,生产同样数量电晶体的成本就会下降一半,但近几年半导体设备越来越贵,每片晶圆的售价不断升高。

5月11日,台积电在技术论坛上,对许多未来发展的关键问题给出了答案。在后摩尔定律时代,台积电会持续高速成长,但从材料、技术到市场,都将出现重大改变。

台积电总裁魏哲家在开幕演讲里明示改变将至。他说,虽然台积电努力降低成本,但俄乌冲突让台积电花比原本高6~7倍价格,才能买到生产晶圆用的氖气;他半开玩笑地说:“你们老板的脑海里马上会想,这小子是不是想涨价!”

魏哲家也提到,线宽微缩技术的空间已经越来越少,1台用来生产高阶芯片的EUV(极紫外光曝光机),“价格可以盖两百栋房子”,这是他十几年前想不到的。台积电用600美元把芯片卖给客户,做成服务器后,却得花20万美元买,价值增加了330倍。

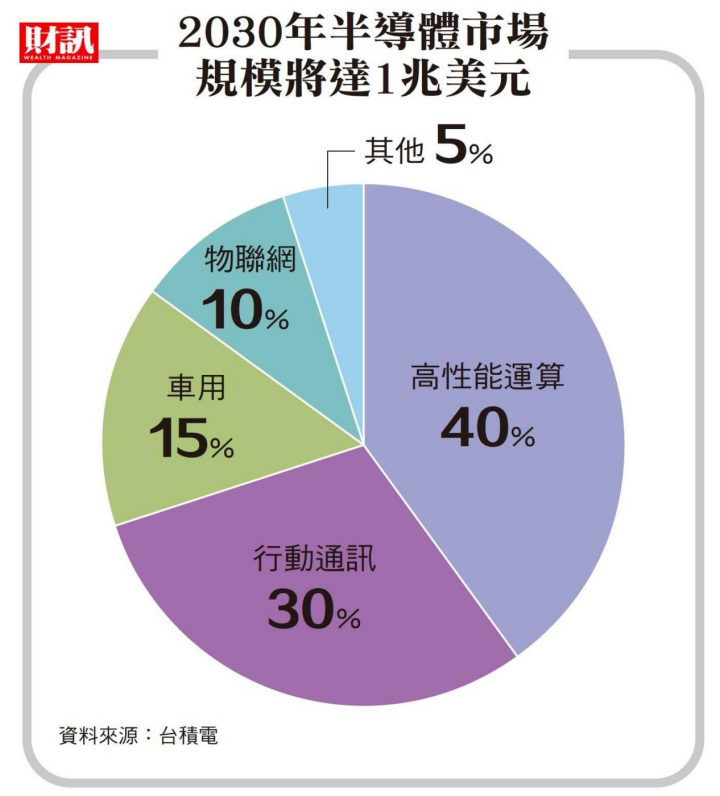

会中,台积电打出一张投影片。根据台积电的估算,2030年时,全球半导体产值将达1兆美元;这个数字相当惊人,因为根据美国半导体产业协会估计,2022年时,全球半导体产业规模为5741亿美元,意指未来7年,半导体产业还会再成长超过7成。

台积电预期,未来需求最大的是高性能运算,其次是行动通讯,不过这两种应用的占比和现在差不多,分别为4成和3成;但车用芯片的占比则将翻扬1倍,占市场需求的15%,物联网也将占有整个市场10%的需求。

在这次大会中,台积电也揭露了2nm之后的发展路径。台积电的专家介绍一种称为CFET的新型电晶体结构,改用这种新设计,台积电可以在同样的面积生产出两层电晶体结构,运算效能马上多出1倍。同时,1nm以下,硅的限制越来越大,就要改用纳米碳管、二维半导体材料来制造芯片,虽然还要一段时间,但半导体材料发展将出现新的转折。

魏哲家强调,半导体要继续进步,除了架构要改变,更需要产业上下游的合作。这次会议中,台积电展示了新版的3D封装技术,原本台积电的先进封装技术可分成SOIC、CoWoS和InFO 3种,现在这3种技术都分别演化出高性能版和平价版,而且每1种台积电都能独立完成制造、封装、测试。

台积电副总张晓强表示,这是技术发展的需要,因为发展AI芯片,除了要求提升能源效率、降低耗电率,同时还需要芯片和存储器的高速整合。像ChatGPT等AI应用,都需要计算巨量参数的变化,逻辑芯片透过先进封装整合存储器,需求相当强劲。

节省能源先进制程关键点

至于摩尔定律未来是否能持续?张晓强表示:“以前大家理解摩尔定律的时候,是在单一的芯片上看摩尔定律,将来摩尔定律是要在系统阶层上面,你如果把先进封装算进来,摩尔定律的经济效率还是存在的。例如在资料中心,你把今年运算用的芯片,从5nm搬到3nm,光省下的电费就足够支付你所有芯片的更新。”换句话说,能节省多少能源,是驱动先进制程发展的关键。

今年5月,三星电子会长李在镕和特斯拉执行长马斯克单独会面,外界解读是为争夺车用自驾芯片商机。台积电也在这次大会上,公布两种车用芯片的新制程N4AE和N3AE;台积电表示,过去车用芯片鲜少采用先进制程,由于车用芯片验证时间长,现在车厂已能用4nm和3nm技术来设计车用芯片,等到明后年车用4nm和3nm制程上线,马上就能生产先进车用芯片,明显要阻断三星靠车用芯片超车的计划。

介入存储器领域踢馆三星

与此同时,台积电也大力投资特殊制程,在日本等地建立12到28nm成熟制程新厂。台积电资深处长刘信生比喻,就像人有眼耳鼻舌身意等感知能力,制造这些感测芯片都要靠特殊制程,因此从2017年到2022年,台积电特殊制程投资的年复合成长率超过4成,而现在到2026年,特殊制程产能还要再增加5成。

这些特殊制程的投资,很多是用来创造更先进的感知能力。刘信生解释,像智能车、机器人需要更多的摄影镜头,这些镜头和拍照用的手机不同,要能看到人看不到的讯号,或是未来的镜头感测元件里,还可以加上AI逻辑运算,让AI可以普及到终端装置上,甚至台积电也用28nm制程制造显示器控制电路,这些用在AR装置上的新型显示器,解析度可达4000PPI,这足以把1台4K显示器放进你的眼镜。

现在,台积电也用22、28nm制程制造MRAM和RRAM存储器,供智能车使用,当三星想用车用芯片攻进台积电擅长的逻辑领域,台积电也把影响力延伸至三星擅长的存储器领域。今年开始,先进封装和特殊制程都将扮演比过去更重要的角色,而从台积电产能增加的速度看来,新一轮半导体产值的大成长正刚刚开始。

台积电为2纳米节点增加两个变体,英特尔会赶上吗?

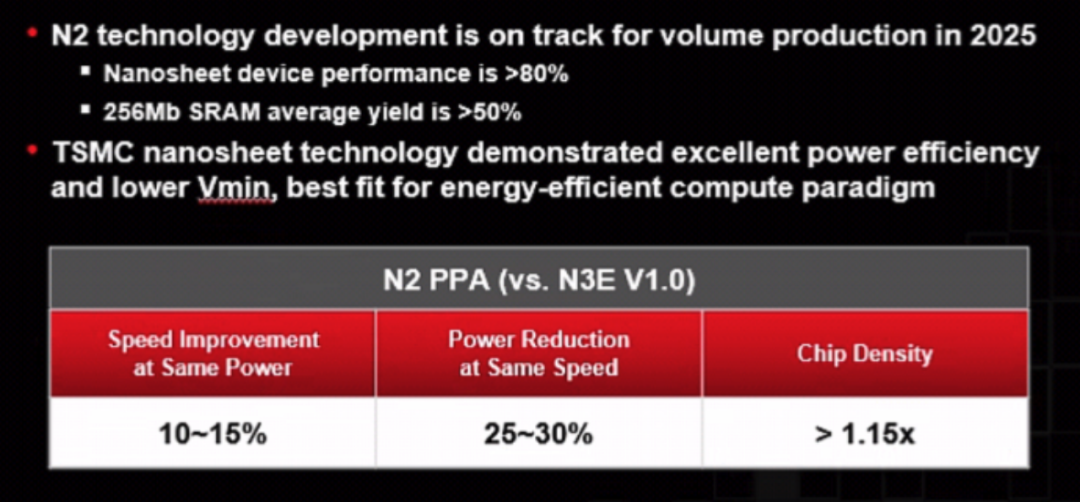

根据台积电在加利福尼亚州圣克拉拉举行的 2023 年北美技术研讨会上提供的详细信息,台积电的 2 纳米芯片制造工艺(广为人知的 N2)有望在 2025 年投产。中国台湾的大型晶圆厂还将在 2026 年为其 N2 技术添加两种变体:具有背面供电的 N2P 和用于高性能计算的 N2X。

N2 及其变体将成为台积电第一个采用环栅 (GAA) 晶体管(台积电称之为纳米片晶体管)的制造节点,以提高逻辑、SRAM 和模拟电路的性能、能效和晶体管密度.GAA 技术有助于降低漏电流,因为栅极存在于通道的所有四个侧边。此外,GAA 晶体管提高了调整通道宽度的能力,以实现更高的性能或更低的功耗。

两个 N2 变体的发布是研讨会最突出的亮点之一。来源:台积电

在座谈会上,台积电声称其新型纳米片晶体管已达到 80% 的目标性能规格,而 256-Mb SRAM 的平均良率目前超过 50%。而半导体代工厂还有两年的时间来改善这些数字。

据台积电称,N2 将在与 N3 相同的功率下提供 10% 至 15% 的性能提升,或者在相同时钟下将功率降低 25% 至 20%。该工厂还声称,对于包含逻辑、SRAM 和模拟的混合芯片,N2 的密度将比 N3E(N3 制造节点的增强版)高 15%。

座谈会主要提供了去年公布的N2工艺节点的细节。来源:台积电

虽然有关台积电 N2 技术的细节已经流传了一段时间,但随着这项先进的制造技术延伸到 2026 年,有关 N2 制造节点的两个新版本的公告是最新的。开始研究 2 纳米芯片制造的台积电2020年的工艺,多年来一直不懈地追求这一尖端芯片制造技术。

以下是有关 N2 制造节点变体(N2P 和 N2X)的一些详细信息,它们预计将于 2026 年投入生产,并且在这些节点上制造的芯片可能会在 2027 年到货。

N2P制造节点

早些时候,当台积电宣布采用纳米片设计的 N2 生产计划时,它发誓要在未来的版本中增加背面供电;该版本的 2 纳米制造被命名为 N2P。就像英特尔和三星分别采用的PowerVia和BSPDN制造技术一样,将晶体管夹在供电网络和信号网络之间,以提高晶体管性能并降低功耗。

背面供电通过将电源轨移至背面来分离 I/O 和电源布线,解决了后端线路 (BEOL) 中过孔电阻升高等挑战。因此,当芯片制造商一直在与芯片供电电路中的阻力作斗争时,背面供电可提高晶体管性能、降低功耗并消除数据和电源连接之间的一些潜在干扰。

Applied Materials 估计背面供电有助于减少 20% 到 30% 的逻辑单元面积。尽管台积电尚未提供有关 N2P 技术的任何细节,但发表在AnandTech上的一份报告称,背面电源轨可以带来两位数的晶体管密度改进和个位数的效率提升。

N2X制造节点

台积电还在准备 N2X,这是一种为高性能计算 (HPC) 设备量身定制的制造工艺,例如需要更高电压和时钟速度的高端 CPU 和 GPU。N2X 将在 N2P 之后出现,因此有关 HPC 应用程序的这种 N2 变体的信息更加稀缺。

英特尔会迎头赶上吗?

在这里值得一提的是,英特尔在其 20A 工艺上遵循类似的 2 纳米制造工艺轨迹,该工艺还采用背面供电技术。英特尔计划在2024年底将其2nm PowerVia制程节点推向量产,如果这家位于加州圣克拉拉的芯片制造商能够成功执行这一计划,它将在实施晶背供电传输的竞赛中超前台积电近两年。然而,考虑到英特尔在执行先进制程节点方面的发展记录,以及其于获得ASML最新的EUV微影设备方面的挑战,能不能做到这一点仍有待观察。尽管如此,除了三星,台积电在纳米竞赛中也出现了第二家竞争对手。

编辑:黄飞

-

台积电

+关注

关注

44文章

5623浏览量

166346 -

存储器

+关注

关注

38文章

7470浏览量

163705 -

摩尔定律

+关注

关注

4文章

633浏览量

78969 -

封装技术

+关注

关注

12文章

545浏览量

67981

原文标题:台积电2纳米制程路线图公布

文章出处:【微信号:ICViews,微信公众号:半导体产业纵横】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

后摩尔定律时代局势大变 台积电公布2nm后的发展路径图

后摩尔定律时代局势大变 台积电公布2nm后的发展路径图

评论