众所周知,***作为芯片生产过程中的最主要的设备之一,其重要性不言而喻。

先进的制程工艺完全依赖于先进的***设备,比如现阶段台积电最先进的第二代 3nm 工艺,离不开 EUV ***。

然而,前不久麻省理工学院(MIT)华裔研究生朱家迪突破了常温条件下由二维(2D)材料制造成功的原子晶体管,每个晶体管只有 3 个原子的厚度,堆叠起来制成的芯片工艺将轻松突破 1nm。

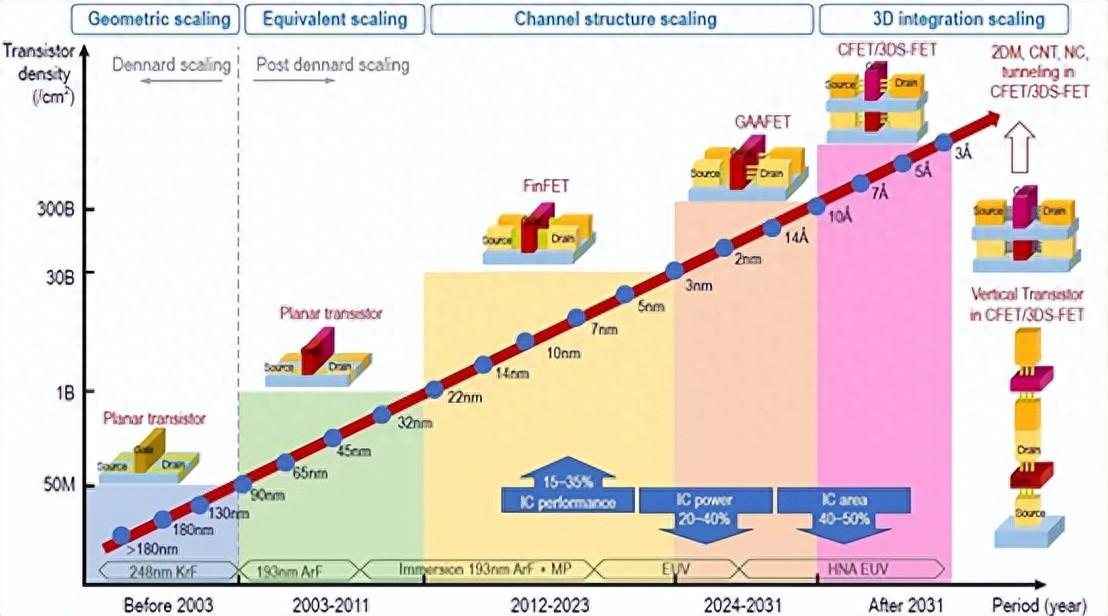

目前的半导体芯片都是在晶圆上通过光刻/蚀刻等工艺加工出来的三维立体结构,所以堆叠多层晶体管以实现更密集的集成是非常困难的。

而且,现在先进制程工艺的发展似乎也在 1~3nm 这里出现了瓶颈,所以不少人都认为摩尔定律到头了。

但是由超薄 2D 材料制成的半导体晶体管,单个只有 3 个原子的厚度,可以大量堆叠起来制造更强大的芯片。

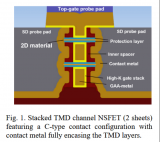

正因如此,麻省理工学院的研究人员研发并展示了一种新技术,可以直接在硅芯片上有效地生成二维过渡金属二硫化物 (TMD) 材料层,以实现更密集的集成。

但是,直接将 2D 材料生成到硅 CMOS 晶圆上有一个问题,就是这个过程通常需要约 600 摄氏度的高温,但硅晶体管和电路在加热到 400 摄氏度以上时可能会损坏。

这次麻省理工学院(MIT)华裔研究生朱家迪等人的研究成果就是,开发出了一种不会损坏芯片的低温生成工艺,可直接将 2D 半导体晶体管集成在标准硅电路之上。

此外,这位华裔研究生的新技术还有两个优势:拥有更好的工艺+减少生成时间。

之前研究人员是先在其他地方生成 2D 材料,然后将它们转移到晶圆上,但这种方式通常会导致缺陷,进而影响设备和电路的性能,而且在转移 2D 材料时也非常困难。

相比之下,这种新工艺会直接在整个 8 英寸晶圆上生成出光滑、高度均匀的材料层。

其次就是能够显著减少生成 2D 材料所需的时间。以前的方法需要超过一天的时间来生成 2D 材料,新方法则将其缩短到了一小时内。

“使用二维材料是提高集成电路密度的有效方法。我们正在做的就像建造一座多层建筑。如果你只有一层,这是传统的情况,它不会容纳很多人。但是随着楼层的增加,大楼将容纳更多的人,从而可以实现惊人的新事物。”

朱家迪在论文中这样解释,“由于我们正在研究的异质集成,我们将硅作为第一层,然后我们可以将多层 2D 材料直接集成在上面。”

随着 ChatGPT 的兴起,带动了人工智能产业的蓬勃发展,AI 的背后就需要强大的硬件算力支持,也就是芯片。

该技术不需要***就可以使芯片轻松突破 1nm 工艺,也能大幅降低半导体芯片的成本,如果现阶段的***技术无法突破 1nm 工艺的话,那么这种新技术将从***手中拿走接力棒,届时***也将走进历史~

审核编辑 :李倩

-

芯片

+关注

关注

458文章

51526浏览量

429464 -

半导体

+关注

关注

335文章

27970浏览量

225117 -

晶体管

+关注

关注

77文章

9829浏览量

139386

原文标题:光刻机将成为历史!麻省理工华裔研究出 2D 晶体管,轻松突破 1nm 工艺!

文章出处:【微信号:robotqy,微信公众号:机械自动化前沿】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

IEDM 2024先进工艺探讨(三):2D材料技术的进展及所遇挑战

金刚石基晶体管取得重要突破

欧洲启动1nm及光芯片试验线

麻省理工科技评论:2025年AI领域突破性技术

IBM与Rapidus在多阈值电压GAA晶体管技术的新突破

MOSFET晶体管的工艺制造流程

麻省理工学院研发全新纳米级3D晶体管,突破性能极限

麻省理工学院推出新型机器人训练模型

NMOS晶体管和PMOS晶体管的区别

2D多鳍FETs的高密度集成,搭台引导外延的科技突破!

GaN晶体管和SiC晶体管有什么不同

微电子所在《中国科学:国家科学评论》发表关于先进CMOS集成电路新结构晶体管的综述论文

麻省理工华裔研究出2D晶体管,轻松突破1nm工艺!

麻省理工华裔研究出2D晶体管,轻松突破1nm工艺!

评论