随着互联网的普及,手机逐渐成为我们的个人标配。手机的关键在于芯片,芯片的质量很大程度上决定了手机的性能,可是手机芯片为什么这么贵呢?

芯片就像手机的大脑,我们将输入信号作为原材料输入手机,通过改变芯片内部的走线、逻辑,就能对输入信号实现不同的处理方式。 也正因此,手机芯片是当今集成度超高的元器件,别看它只有一个指甲盖的大小,里面可是包含了数十亿晶体管呢,苹果的A15仿生芯片包含了150亿个晶体管,每秒可执行15.8万亿次操作。 因此,无论是研发还是制造难度,大家都可想而知。

经常会有新闻讲某某公司在芯片方面投了多少亿,文档君觉得好多好多钱呀,可是了解下去发现,这么多钱竟然只够公司烧一年?今天我们就从芯片的研发与生产两个方面来看看,手机芯片是如何产生的?为啥那么贵? 一款芯片从无到有,要经历两大阶段:研发环节和制造环节。

芯片研发 芯片的研发流程大致可分为:

IP(知识产权)采购

前端设计

验证

DFT(可测试性设计)设计

后端设计

封装设计

回片测试

其中,前端设计、验证、DFT设计、后端设计、封装设计等过程需要大量的研发人员的人力投入和不同团队的分工合作。

芯片制造 比起芯片的研发,芯片制造的难度更大,技术壁垒更高。 芯片的生产与制造可以大体分为晶圆制造、晶圆光刻显影和刻蚀、掺加杂质和封装测试四个步骤。 晶圆制造 晶圆是制造芯片的物质基础,由石英砂精炼得来,晶圆是从99.99%的纯硅圆柱体(也叫“硅锭”)上切下来的(以半导体制造中最常用的尺寸12寸为例,由于芯片的尺寸各不相同,从12英寸的晶圆上可分割出来几十个到数千个芯片),并被打磨得极为光滑,然后再根据结构需求将导体、绝缘体或半导体材料薄膜沉积到晶圆上。当前我国具备一定的晶圆制造能力,基本上可以实现国产自用。

晶圆光刻显影和刻蚀

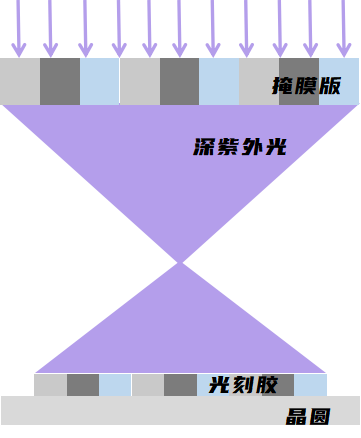

光刻技术决定了芯片上的晶体管可以做到多小。晶圆被放入***中,暴露在深紫外光(DUV)下。光线通过掩模版投射到晶圆上,***的光学系统(DUV系统的透镜)将掩模版上设计好的电路图案缩小并聚焦到晶圆上的光刻胶。

光刻胶,又称光致抗蚀剂,是指通过紫外光、电子束、离子束、X射线等的照射或辐射,其溶解度发生变化的耐蚀剂刻薄膜材料。

当光线照射到光刻胶上时,会产生化学变化,将掩模版上的图案印制到光刻胶涂层上。

刻蚀是为了去除退化的光刻胶,以显示出预期的图案。 在刻蚀过程中,晶圆被烘烤和显影,光刻胶被洗掉,显示出一个开放通道的3D图案。 先进的刻蚀技术使芯片制造商能够使用双倍、四倍和基于间隔的图案来创造出现代芯片设计的微小尺寸。像3D NAND这种高达175层的空腔结构的芯片设计,需要保证空腔深度完全正确,刻蚀过程格外困难。

通过***对指定位置进行刻蚀,这一过程极为精密和复杂,实际上世界上只有荷兰 ASML 公司有能力制造昂贵的***,其 7nm ***售价高达 1 亿美元 。

掺加杂质

掺加杂质可以增加立体结构复杂程度,越是复杂的集成电路,其立体结构就越复杂,掺加杂质的步骤也就越复杂。集成电路的基础是 PN 结,要想形成 PN 结,就必须在不同的晶圆里掺加不同的杂质(本质上而言是加入 P、N 型杂质,改变其导电性质)。

PN结:采用不同的掺杂工艺,通过扩散作用,将P型半导体与N型半导体制作在同一块半导体(通常是硅或锗)基片上,在它们的交界面就形成空间电荷区称为PN结。PN结具有单向导电性,是电子技术中许多器件所利用的特性,例如半导体二极管、双极性晶体管的物质基础。

封装测试

在封装过程中,为了把芯片从晶圆上取出来,要用金刚石锯将其切成单个芯片。从晶圆上分割出来的芯片又称为“裸晶”,随后会被放置在“基板”上——这种基板使用金属箔将裸晶的输入和输出信号引导到系统的其他部分。然后我们会为它盖上具有“均热片”的盖子,均热片是一种小的扁平状金属保护容器,里面装有冷却液,确保芯片可以在运行中保持冷却。

经过上述流程,芯片制造商就完成了从版图到芯片实体的流程,但芯片能否具体工作,其电气性能是否达标,还需要完成测试才能确定。

因此,芯片制造厂商均需要一批后端测试人员对芯片的性能进行测试。

当然,半导体制造涉及到的步骤远不止这些,芯片还要经过测量检验、电镀、测试等更多环节,每块芯片在成为电子设备的一部分之前都要经过数百次这样的过程。

研发成本 了解了芯片的研发和制造过程,文档君带大家继续了解一下芯片为啥这么烧钱呢?

芯片的研发成本主要包含IP采购、前端设计、验证、DFT设计、后端设计、封装设计、回片测试等部分费用。

IP采购

IP采购是芯片研发中不可忽视的一个环节。 费用模式通常分为一次性授权、产品单独授权,或者两者叠加起来。

例如,手机处理器芯片、AI芯片等都需要集成CPU模块,目前国内大部分芯片设计公司都采购ARM的CPU核。 IP核,全称知识产权核 (intellectual property core),是指某一方提供的、形式为逻辑单元、芯片设计的可重用模块。

回片测试 回片测试包含测试硬件、RA(Reliability Test,可靠性测试)实验、ATE(Automatic Test Equipment,集成电路自动测试设备)机台使用以及研发人力投入等成本。

其他 前端设计、验证、DFT设计、后端设计、封装设计支出主要以研发人员的人力投入为主,此外还包含EDA软件的使用费、FPGA和Zebu等验证平台的硬件费用。

生产成本 芯片生产成本主要包括流片、晶圆、CP(Chip Probe,晶圆)测试、封装、FT(Final Test,最终测试)、SLT(System Level Test,系统级测试)等,其中大部分集中在流片和晶圆。

流片成本

流片,是指像流水线一样通过一系列工艺步骤制造芯片,在集成电路设计领域,“流片”指的是“试生产”。

一次性费用,按照掩膜版层数计算。 在芯片设计完成后,会生产复杂的图形文件,一般来说会有几十层到上百层。这些图形文件需要在光罩厂做掩膜版。 工艺节点越高,流片价格越贵,因为高工艺需要更多的掩膜版。在16 nm制程上,需要大约60张,而7nm可能就需要上百张。

目前最便宜的ASIC流片成本也需要几十万一次,180nm的流片成本大概是50万元,55nm的成本约200万元。但是16nm的成本就飙升到了3000万-5000万元,到了7nm最低也要过亿。

但到了量产阶段,尤其是产品的出货量比较大,一次性流片费用平摊到数十万颗芯片上时,相对成本就低了很多。

晶圆成本

按照出货片数每片计算。

晶圆价格也是按照工艺节点区分的。台积电12寸晶圆40nm成本每片大约在1500~2000美元,16nm成本每片大约在4000~5000美元之间,7nm成本每片大约在9300美元左右,5nm代工价格约为17000美元,3nm价格预计会达到30000美元左右。

审核编辑:刘清

-

晶圆

+关注

关注

52文章

4922浏览量

128074 -

晶体管

+关注

关注

77文章

9701浏览量

138386 -

DFT

+关注

关注

2文章

231浏览量

22752 -

半导体二极管

+关注

关注

0文章

35浏览量

10716

原文标题:手机芯片为啥这么烧钱?

文章出处:【微信号:ztedoc,微信公众号:中兴文档】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

手机芯片为啥这么烧钱?

手机芯片为啥这么烧钱?

评论