曾经有一段时间,实际上是几十年,制造更好的计算机芯片所需要的只是更小的晶体管和更窄的互连。DNA那个时代已经一去不复返了,虽然晶体管会继续变得更小,但简单地制造它们已不再是重点。

上周在比利时安特卫普举行的ITF 2023 世界大会上,研究人员认为,现在保持计算速度呈指数级增长的唯一方法是一种称为系统技术协同优化 (STCO) 的方案。它能够将芯片分解成它们的功能组件,为每个功能使用最佳的晶体管和互连技术,并将它们重新拼接在一起以创建一个功耗更低、功能更好的整体。

Imec研发经理Marie Garcia Bardon说:“这将我们引向 CMOS 的新范式。” 正如总部位于比利时的纳米技术研究组织所称,CMOS 2.0 是一个复杂的愿景。但它可能是最实用的前进方式,其中的一部分已经在当今最先进的芯片中得到体现。

我们是怎么到这里的

Imec 研发副总裁Julien Ryckaert说,从某种意义上说,半导体行业在 2005 年之前的几十年里被宠坏了。在那段时间里,化学家和设备物理学家能够定期生产更小、功耗更低、速度更快的晶体管,可用于芯片上的每项功能,这将导致计算能力的稳步提高。

但此后不久,轮子开始脱离该计划。设备专家可以想出出色的新晶体管,但这些晶体管并不能制造出更好、更小的电路,例如构成 CPU 主体的 SRAM 存储器和标准逻辑单元。作为回应,芯片制造商开始打破标准单元设计和晶体管开发之间的障碍。称为设计技术协同优化或 DTCO 的新方案导致专门设计用于制造更好的标准单元和存储器的设备。

但 DTCO 不足以让计算继续进行。物理和经济现实的局限性共同为通用型晶体管的发展设置了障碍。如Imec 的首席工程师Anabela Veloso解释说,物理限制阻止了 CMOS 工作电压降低到大约 0.7 伏以下,从而减缓了功耗的进展。转向多核处理器帮助改善了这个问题一段时间。同时,输入输出限制意味着越来越需要将多个芯片的功能集成到处理器上。

因此,除了具有多个处理器内核实例的片上系统 (SoC) 之外,它们还集成了网络、内存和通常专用的信号处理内核。这些内核和功能不仅具有不同的功率和其他需求,而且它们也无法以相同的速度变得更小。即使是 CPU 的高速缓存 SRAM,也不会像处理器的逻辑那样快速缩小。

系统技术协同优化

让事情摆脱困境与技术集合一样是一种哲学转变。根据 Ryckaert 的说法,STCO 意味着将片上系统视为功能的集合,例如电源、I/O 和缓存存储器。“当你开始对功能进行推理时,你会意识到 SoC 不是这种同质系统,只是晶体管和互连,”他说。“它是功能,针对不同的目的进行了优化。”

理想情况下,您可以使用最适合它的工艺技术来构建每个功能。实际上,这主要意味着在自己的硅片或小芯片上构建每个。然后,您可以使用高级 3D 堆叠等技术将它们绑定在一起,这样所有功能就好像它们在同一块硅片上一样。

这种想法的例子已经出现在高级处理器和人工智能加速器中。英特尔的高性能计算加速器 Ponte Vecchio(现在称为英特尔数据中心 GPU Max)由 47 个小芯片组成,这些小芯片使用两种不同的工艺构建,分别来自英特尔和台积电。AMD 已经在I /O 小芯片上使用了不同的技术并在其 CPU 中计算小芯片,它最近开始为计算小芯片的高级高速缓存分离出SRAM 。

Imec 的 CMOS 2.0 路线图走得更远。该计划需要继续缩小晶体管,将电源和可能的时钟信号移动到 CPU 的硅片下方,以及更加紧密的 3D 芯片集成。Ryckaert 说:“我们可以使用这些技术来识别不同的功能,分解 SoC,然后重新集成它,从而非常高效。”

晶体管将在未来十年内改变形式,但连接它们的金属也会改变。最终,晶体管可能是由二维半导体而不是硅制成的堆叠设备。电力传输和其他基础设施可以分层放置在晶体管下方。

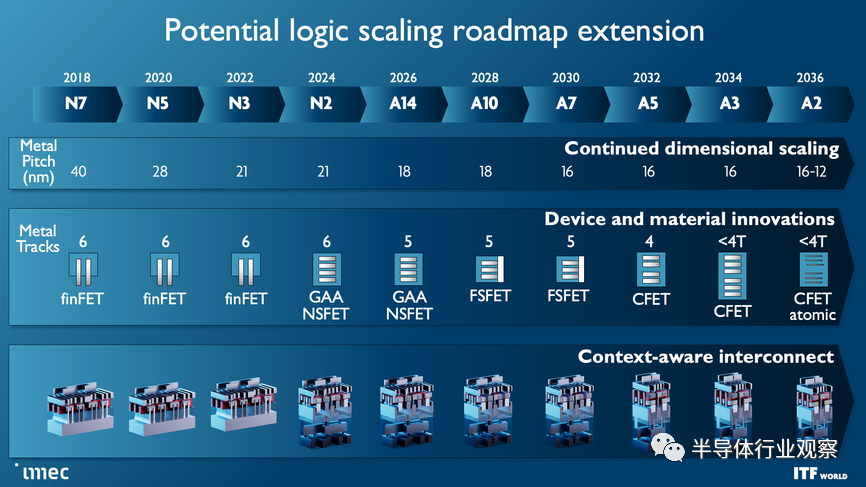

持续的晶体管缩放

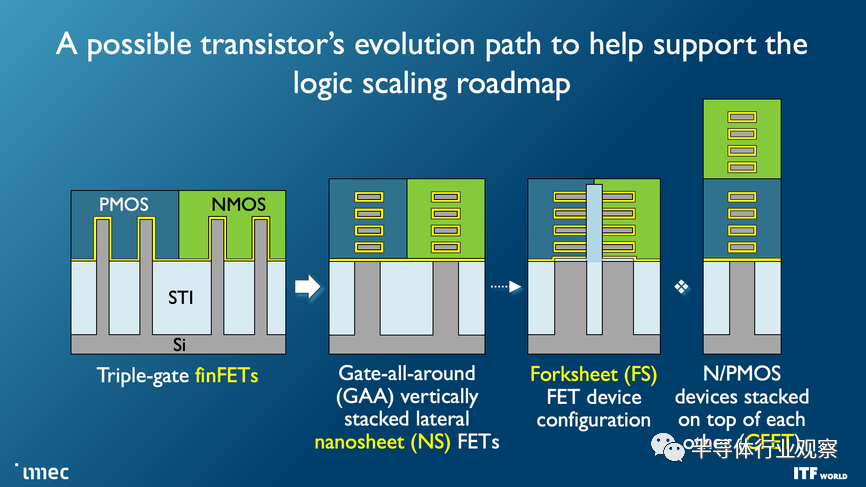

主要芯片制造商已经从为过去十年的计算机和智能手机提供动力的 FinFET 晶体管过渡到一种新的架构,纳米片晶体管。最终,两个纳米片晶体管将在彼此之上构建,形成互补的 FET 或 CFET,Velloso 称其“代表了 CMOS 缩放的终极”。

随着这些设备按比例缩小和改变形状,主要目标之一是缩小标准逻辑单元的尺寸。这通常以“轨道高度”来衡量——基本上,可以安装在单元内的金属互连线的数量。先进的FinFET和早期的纳米片器件是六轨cell。移动到五个轨道可能需要一种称为 forksheet 的间隙设计,它可以将设备更紧密地挤压在一起,而不必使它们更小。然后 CFET 会将单元减少到四个轨道或可能更少。

根据 Imec 的说法,芯片制造商将能够使用ASML 的下一代极紫外光刻技术生产出这一进展所需的更精细的特征。这项称为高数值孔径 EUV 的技术目前正在 ASML 建设中,而 Imec 是下一个交付的。增加数值孔径,一个与系统可以收集光线的角度范围相关的光学术语,可以产生更精确的图像。

背面供电网络

背面供电网络的基本思想是从硅表面上方移除所有发送电力(而不是数据信号)的互连,并将它们放置在硅表面下方。这应该允许更少的功率损耗,因为功率传输互连可以更大且电阻更小。它还为信号传输互连释放了晶体管层上方的空间,可能导致更紧凑的设计。

将来,更多的可能会被转移到硅片的背面。例如,所谓的全局互连——那些跨越(相对)远距离以传输时钟和其他信号的互连——可以位于硅片下方。或者,工程师可以添加有源功率传输设备,例如静电放电安全二极管。

3D整合

进行 3D 集成的方法有多种,但当今最先进的是晶圆到晶圆和芯片到晶圆的混合键合。这两个提供了两个硅芯片之间最高密度的互连。但这种方法要求两个芯片设计在一起,因此它们的功能和互连点对齐,使它们可以作为一个芯片,技术人员的主要成员 Anne Jourdain 说。Imec R&D 有望在不久的将来每平方毫米产生数百万个 3D 连接。

进入 CMOS 2.0

CMOS 2.0 将分解和异构集成发挥到极致。根据哪些技术对特定应用有意义,它可能会产生一个包含嵌入式内存、I/O 和电源基础设施、高密度逻辑、高驱动电流逻辑和大量缓存存储器层的 3D 系统。

要达到这一点,不仅需要技术开发,还需要工具和培训来辨别哪些技术可以真正改进系统。正如 Bardon 指出的那样,智能手机、服务器、机器学习加速器以及增强现实和虚拟现实系统都有非常不同的要求和限制。对一个人有意义的事情对另一个人来说可能是死胡同。

审核编辑 :李倩

-

芯片

+关注

关注

463文章

54593浏览量

470594 -

CMOS

+关注

关注

58文章

6242浏览量

243585 -

机器学习

+关注

关注

67文章

8570浏览量

137381

原文标题:芯片微缩最新路线图,2036年实现0.2nm

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

俄罗斯亮剑:公布EUV光刻机路线图,挑战ASML霸主地位?

全球唯一?IBM更新量子计算路线图:2029年交付!

直播预告|玄铁 x Canonical:从本地推理到 AI 工厂,基于 RISC-V 的 AI 基础设施创新路径探讨

博世SiC路线图:坚守沟槽、全面转向8英寸

博世碳化硅技术路线图持续演进

百亿Token一分钱!云天励飞喊出“推理成本万倍降”,公布三年三芯路线图

天数智芯重磅公布四代架构路线图,对标英伟达

0.2nm工艺节点的背后需要“背面供电”支撑

中国2040年汽车技术路线图发布!内燃机还能再战15年?

纳芯微参编节能与新能源汽车技术路线图3.0正式发布

分享一个驱动开发工程师学习路线图

曦华科技参编节能与新能源汽车技术路线图3.0正式发布

四维图新参与编制两轮车智能化技术发展路线图

华为首次公布昇腾芯片新路线图

芯片微缩最新路线图,2036年实现0.2nm

芯片微缩最新路线图,2036年实现0.2nm

评论