今天给大家分享的是:在电路设计和PCB设计如何防止ESD损坏设备。

在电子行业中,保护设备免受ESD损坏是必须要注意的。静电放电(ESD)是一种非常高的电压尖峰,很容易损坏集成电路和低功率半导体等小信号元件。

常见的ESD是由人体接触电子设备引起的,电荷在人体内累积,然后当身体接触到设备时,电荷就会放电,并伴随着非常高的电压尖峰。

下面介绍在PCB设计中如何减少ESD损害:

一、使用钳位二极管

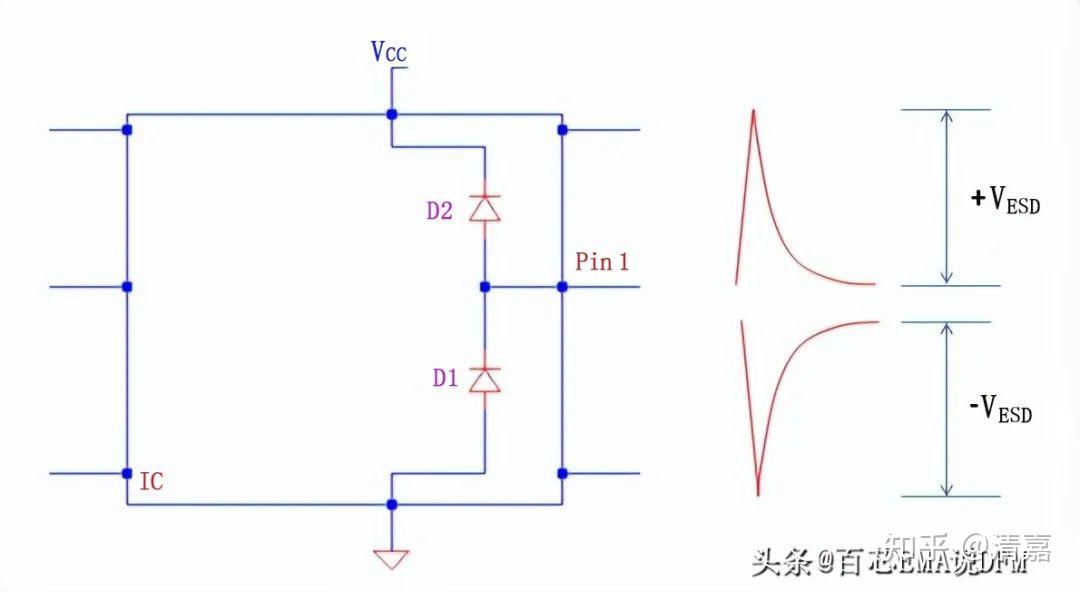

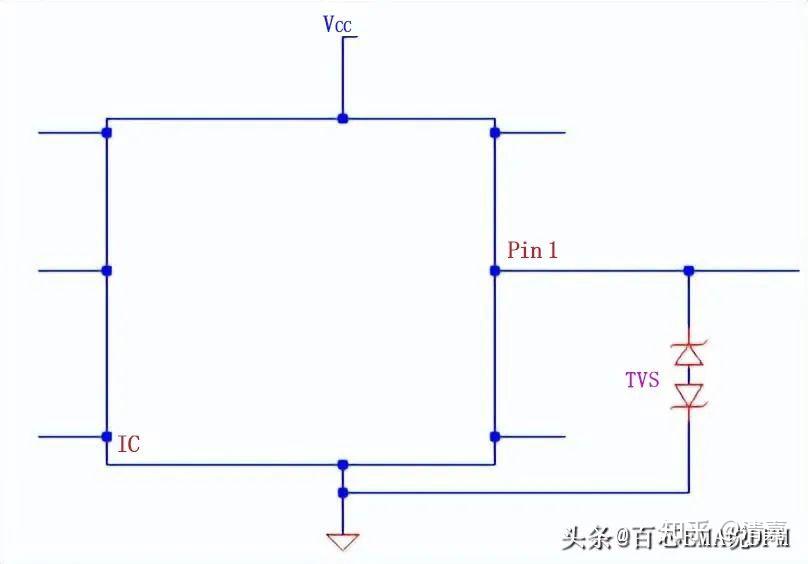

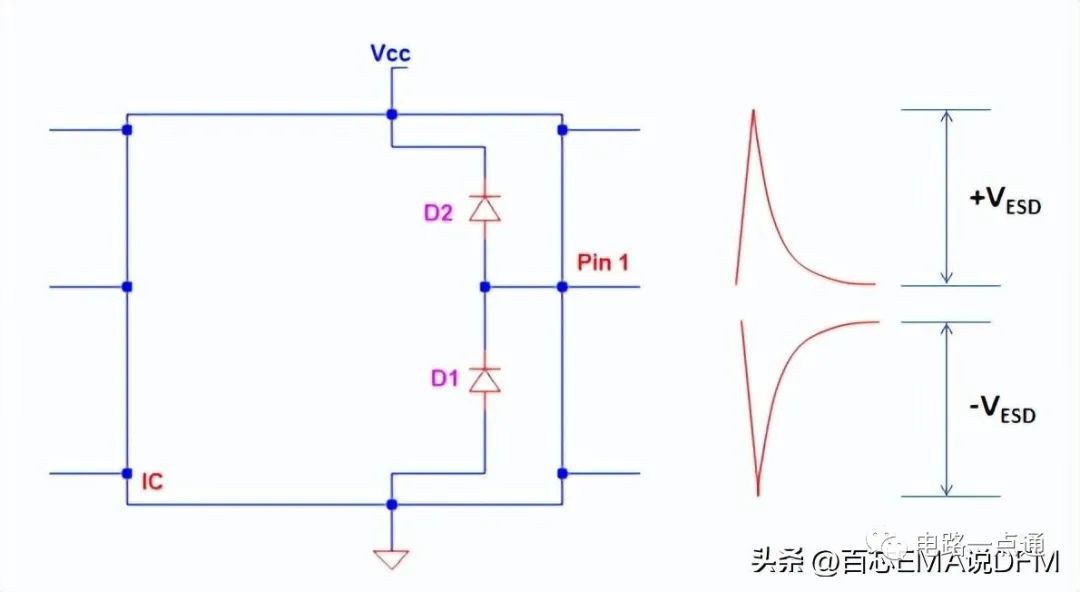

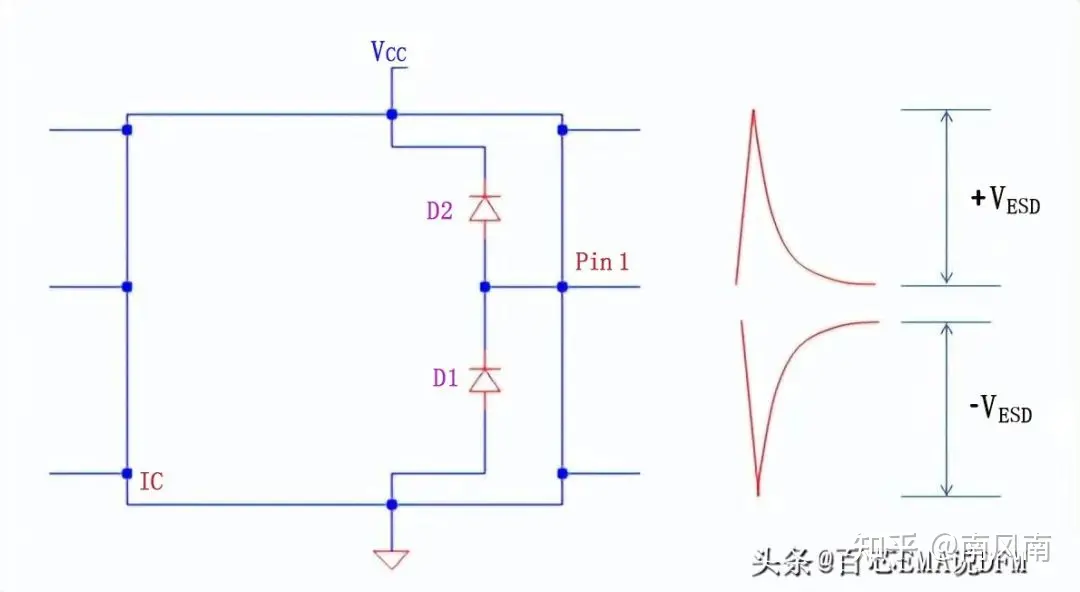

钳位二极管最常用于集成电路中,以保护器件免受ESD的损坏。微控制器、数字信号控制器和处理器都具有内部的ESD钳位二极管。但是在低成本控制器内部有时候会没有钳位二极管,这个时候就需要靠近在外部添加一个钳位二极管。下图是IC固有的ESD钳位二极管。

IC固有的ESD钳位二极管

正常工作时,假设引脚1的电压预计在0-3.3V之间,D1和D2不会干扰。假设高电平为3.3V,则D1反偏不导通,另一方面D2也是不导通的,因为阴极连接到VCC,引脚的高电平等于VCC。当引脚1中的电压为0时,D2反向偏置,D1无偏置。

当存在由ESD引起的高压尖峰时,二极管会导通。例如:尖峰非常高,D2将正向偏置,尖峰将转移到VCC,从而保护IC的内部组件。当存在非常高的负尖峰时,D1将传导并将尖峰转移到地面。

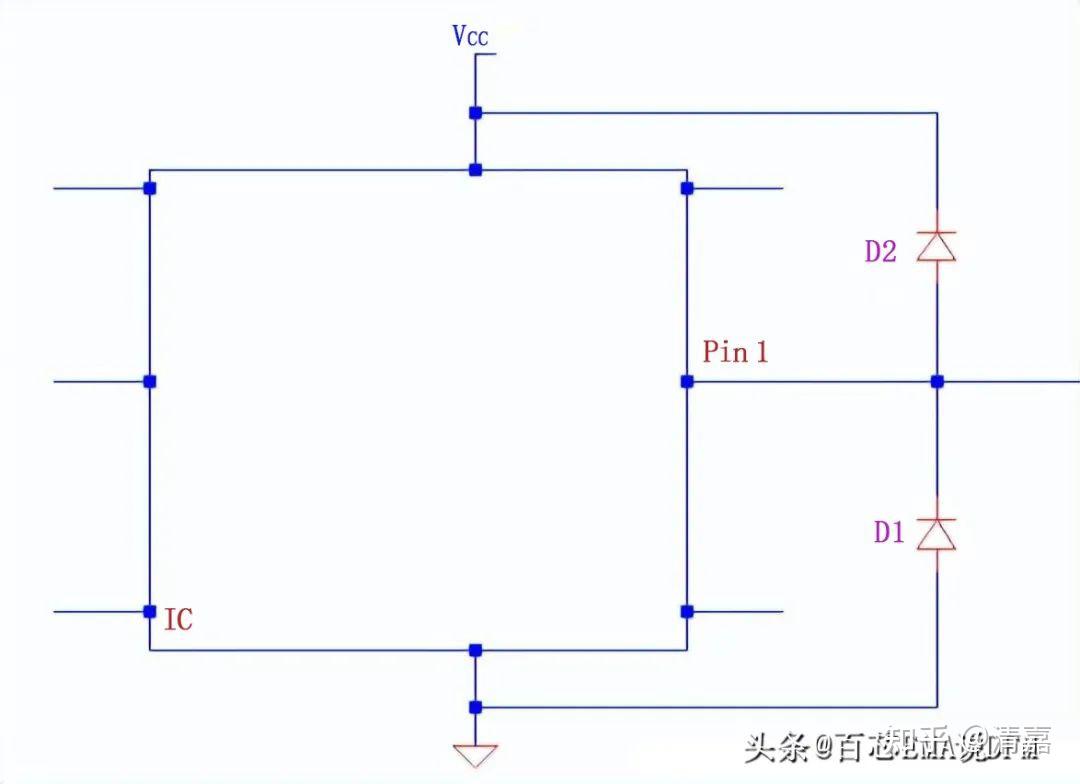

这里必须要了解清楚你使用的IC是否具有保护。如果没有的话,就在外部添加钳位二极管。如下图所示:

在外部添加钳位二极管

如果打算在IC的所有引脚中都添加钳位二极管的话,那是肯定不行,而且成本也会很高。通常来说,在产品制造并放入外壳后,IC将不能再用,钳位二极管需要实现的特性引脚比较少。当然钳位二极管你可以用硅二极管或者肖特基二极管。

下面是通常需要钳位二极管保护的最常见的引脚:

1、编程引脚

通常来说,编程引脚是供工程师使用的。有些产品需要在现场重新编程,编程引脚上发生ESD的可能性比较高。

在编程引脚上添加钳位二极管的另一个原因是因为合规性,如果你是要销售自己的产品,那就必须要遵守ESD标准。在ESD测试中,裸露的引脚是特意注入电压尖峰,产品不能够损坏。

2、重置引脚

一般来说,不会希望产品在没有什么理由的情况下重置或者重启,这个时候复位引脚可从外部访问,当ESD发生时,设备可能会重启启动或者永久损坏。在浪涌等其他合规性测试期间,复位引脚可能会受到干扰,设备将重新启动,这样的情况不希望发生的。(虽然这不是ESD情况,但是由于浪涌电压尖峰的电平非常高,也相当于模拟了ESD)

3、用于检测线路电压或者更高直流电压的IC引脚

这些引脚实际上,从外部是没有办法访问的,ESD在这些引脚上的可能性很小,然后再浪涌测试或者实际浪涌期间,这些引脚可能会遇到更高的尖峰电压,而这些尖峰本质上就像ESD。根据经验松开尖峰,就会容易损坏ESD。

二、使用瞬态电压抑制器

瞬态电压抑制器是快速作用的钳位二极管,不是普通的PN二极管,例如上面的钳位二极管。

TVS在作用和功能方面和钳位二极管差不多。一旦达到其击穿电压,器件就会钳位,否则为开路。

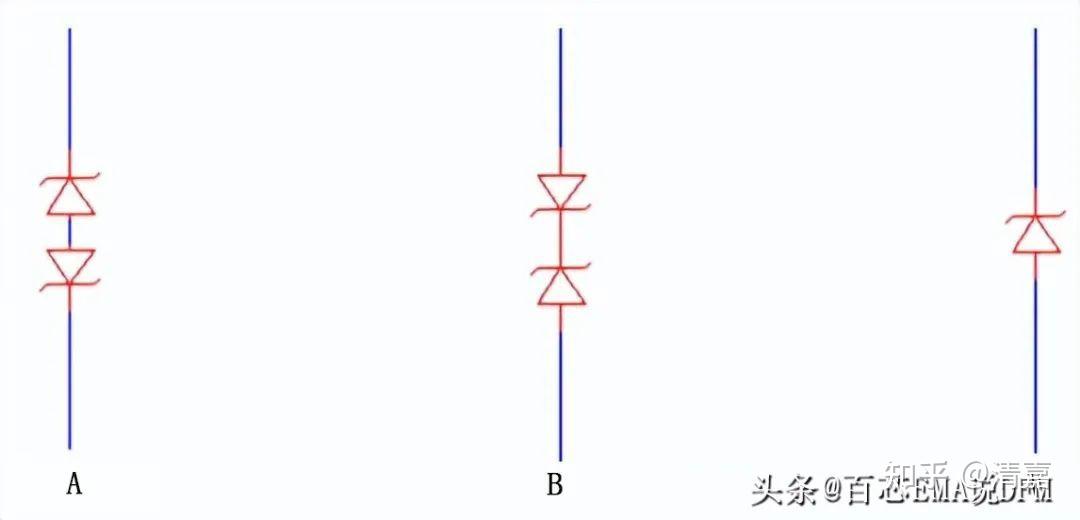

下图显示了常见的TVS符号,图A、B为双向TVS,C为单向TVS。双向TVS可以阻止ESD正向或负向尖峰。另一方面,单向的只能抑制一个定向尖峰。

常见的TVS符号

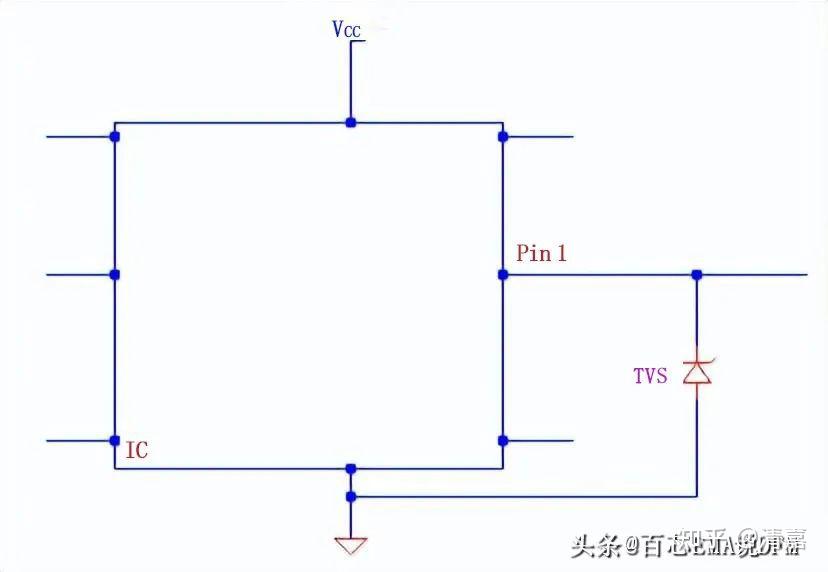

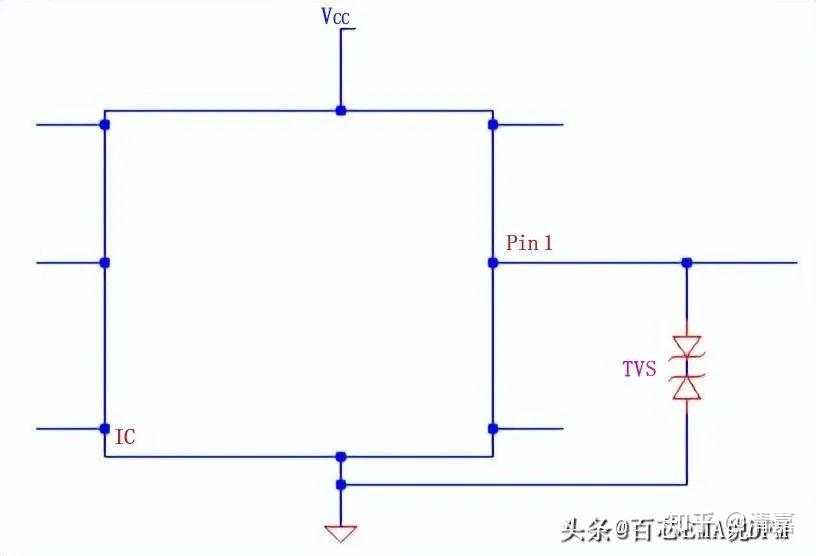

下面3个图是使用TVS保护特定引脚免受ESD影响的示例连接。

1、安装在IC引脚的单向TVS

在电路正常工作时,TVS不导通。但存在正尖峰时,设备将钳位,当存在负尖峰时,设备将正向偏置并将尖峰转移到地面。

安装在IC引脚的单向TVS

2、双向TVS

在正常工作下,TVS不会产生干扰。在正电压尖峰或负电压尖峰期间,TVS将钳位并保护IC。

双向TVS

3、双向 TVS

在正常工作下,TVS 不会产生干扰。在正电压尖峰或负电压尖峰期间,TVS将钳位并保护 IC。

双向 TVS

三、使用齐纳二极管

使用齐纳二极管作为ESD保护与单向TVS原理相同,齐纳二极管的缺点是不如TVS快,并且考虑到TVS相同的尺寸,只能处理较小的能量,需要更大的齐纳二极管来承受能量,但是会占用PCB的空间,成本也会更高。

四、使用高频电容

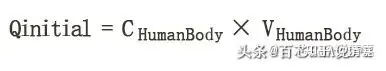

在汽车电路设计中,假定人体具有300PF的等效电容。该电容可以存储高达8KV的电位,当人接触任何东西时,体内的电荷就会放电。如果是小型电子设备,就会损坏。

下面的设置显示了安装在IC引脚中的电容如何受到ESD保护,当人体接触到该引脚时,人体的电容与电容ESD形成并联。正因为如此,人体内的8KV电位才会被抑制。

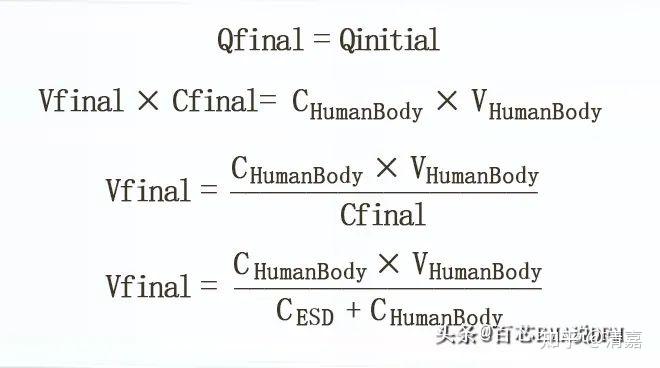

在电荷守恒中,最终电荷等于初始电荷,所以将人体视为初始电荷

当人体接触带有ESD的引脚时,发生充电。然后:

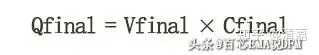

根据电荷守恒:Qinitial=Qfinal。Cfinal是CESD和人体电容的并联组合。Ufinal 是电容器将承受的实际电压。然后:

如上所述,VHumanBody为 8kV,CHumanBody为 330pF。假设我们将选择 33nF CESD,那么最终电压将为:

因此,在引脚上安装33nfESD保护电容后,引脚所承受的电压仅为79.2V,而不是8KV,而电容的额定电压必须高于此值,如果要进一步降低电压水平,只需要增加ESD电容即可。但是进一步增加电容也会增加PCB的尺寸。

以上就是4种防止ESD损坏设备的方法。你可以让任意选择,这4种方法在应用程序中有优点也有缺点,可以在实际测试中验证是否真的有效。

PCB设计可以减少不必要的故障排除和返工成本,下面是在PCB设计中如何防止ESD的措施。

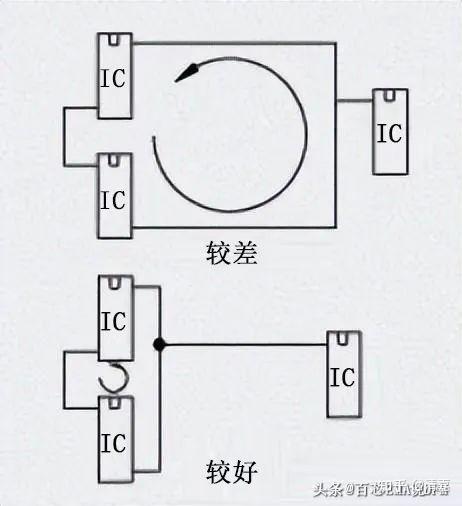

五、减少电路回路面积

电流被感应到闭合且具有变化的磁通量的电路回路中,电流的幅值与回路的面积成正比。也就是说,回路的面积必须减少,因为回路越大,磁通量越大。

减少电路回路面积

电流被感应到闭合且具有变化的磁通量的电路回路中,电流的幅值应与回路的面积成正比,也就是说,回路的面积必须减少,因为回路越大,磁通量越大,在电路中感应出的电流越强。

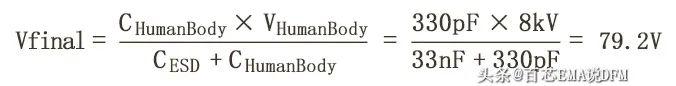

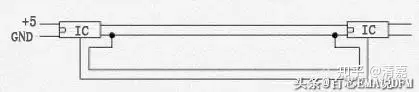

最常见的回路上图所示,由电源和地之间的环路面积,还降低了ESD脉冲产生的高频EMI电磁场。如果不能使用多层电路板,则电源和地线必须如下图所示连接到一个网格上。

电源和地线连接到一个网格

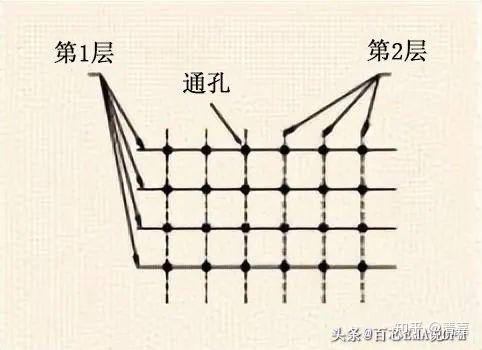

并网连接可以起到电源和地层的作用,各层印刷线路均与过孔相连,过孔之间的连接间距在每个方向上应在6cm以内。另外在布线时,电源和接地印制线尽量靠近也可以减少环路面积,如下所示:

电源和接地印制线尽量靠近也可以减少环路面积

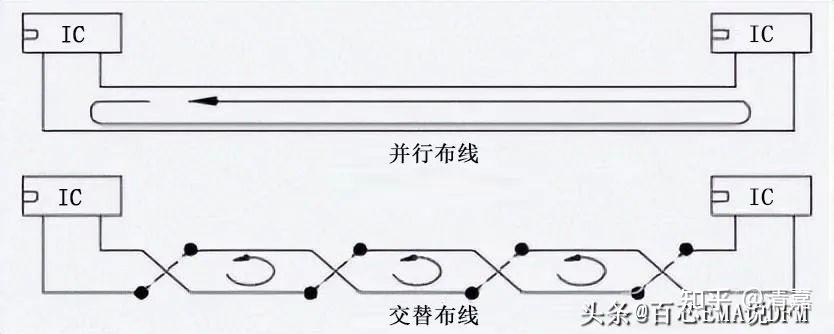

减少环路面积和感应电流的另与一种方法是减少互连设备之间的平行路径,如下所示:

减少互连设备之间的平行路径

当必须使用超过30cm的信号连接线时,可以使用保护线,如下图所示:

使用保护线

更好的一个方法时,在保护线或者接地层13mm以内的信号线附近布设接地信号线,每个传感器或者电源线的长信号线(>30cm)与接地线。

在保护线或者接地层13mm以内的信号线附近布设接地信号线

六、线的长度

长信号线也可以成为接收ESD脉冲能量的天线,使用较短的信号线会降低信号线作为天线接收ESD电磁场的效率,互连相邻位置的设备以减少互连印刷线的长度。

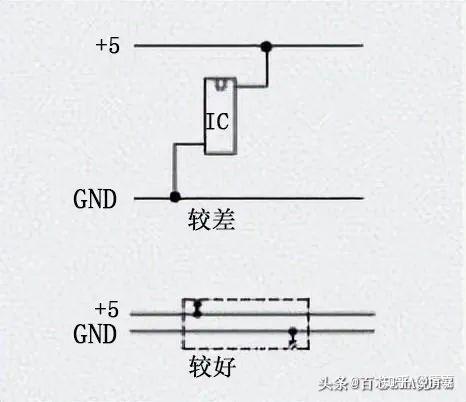

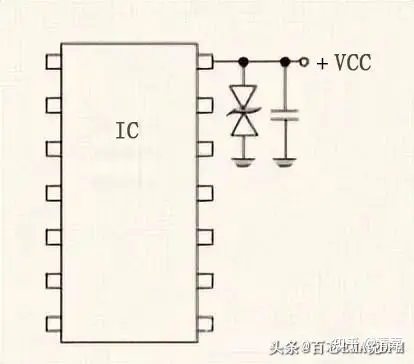

七、减少电荷注入

ESD直接放电到接地层可能会破坏敏感电路。因此,在使用瞬态二极管时,最好在易损元件的电源和地之间防止一个或者多个高频旁路电容。旁路电容减少电荷注入并保持源极和接地端口之间的电压差。TVS分流感应电流,保持TVS钳位间的电压差。TVS和电容应尽可能靠近被保护的IC放置,以确保从TVS到地的路径最短以及定然的长度,以减少寄生电容效应。

减少电荷注入

连接到必须安装到PCB上的铜层,理想情况下,铜层必须与PCB接触层隔离,并通过短导线连接到焊盘。

八、其他的措施

1、避免时钟、复位信号等重要信号线在PCB边缘;

2、将PCB不用的部分设置为地平面;

3、主机壳地线距离信号线至少4mm;

4、保持主壳地线的长宽比小于5:1,减少电感效应;

5、使用 TVS 二极管保护所有外部连接。

审核编辑:汤梓红

-

二极管

+关注

关注

147文章

9624浏览量

166258 -

ESD

+关注

关注

48文章

2026浏览量

172910 -

pcb

+关注

关注

4318文章

23070浏览量

397231 -

电路设计

+关注

关注

6673文章

2449浏览量

204026

发布评论请先 登录

相关推荐

干货 | 电路设计中如何减少ESD?

ESD保护电路的设计pdf

实现 ESD 失效最小化的电路设计原则

PCB抗ESD的设计原则

如何设计ESD保护电路?

ESD保护电路设计法则

CMOS工艺中GG2NMOS结构ESD保护电路设计

集成电路抗ESD设计中的TLP测试技术

电路设计中如何防范ESD

利用仿真减少逆变器电路设计工时的方法

在静电保护电路设计中的ESD器件选型

干货|电路设计中如何减少ESD?

干货|电路设计中如何减少ESD?

评论