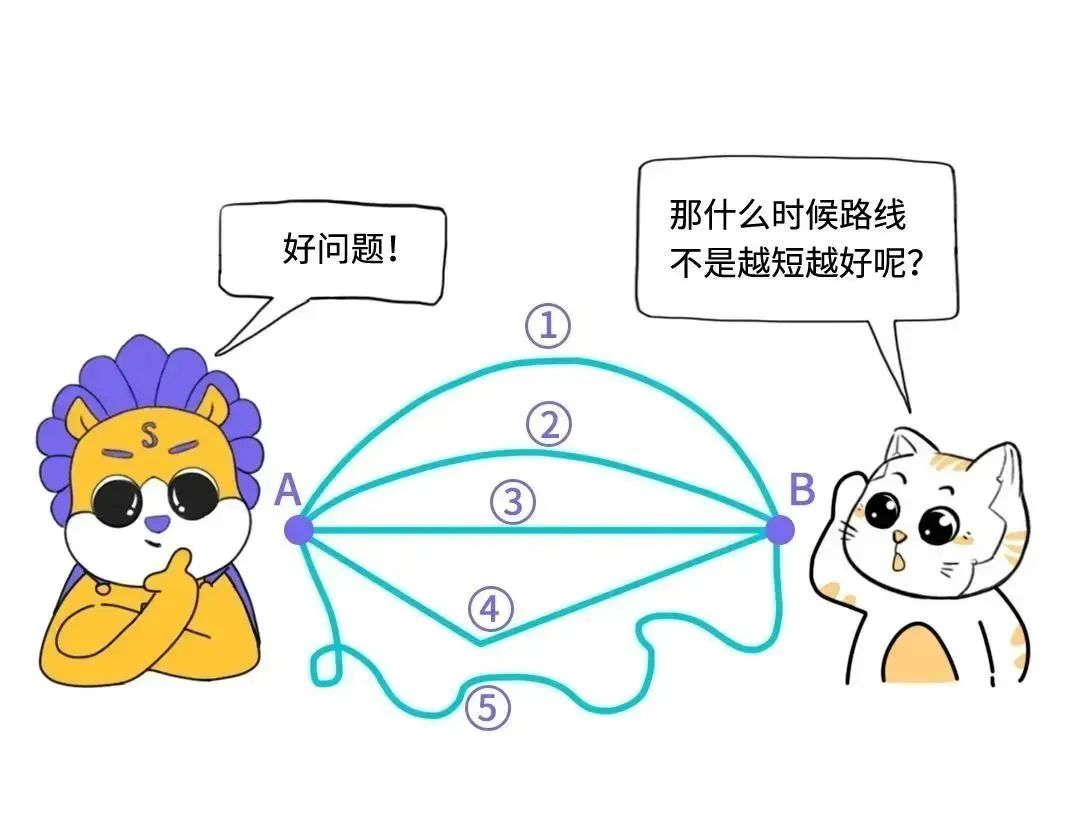

我们都知道:

“两点之间线段最短”、

“走直线,少走弯路”。

然而在芯片界,有时路线却不是越短越好。

人类对便携性的追求,让电子产品越做越小,

内部的电子部分的确是“越来越短”。

比如最初的电脑是个巨无霸,

它有18000个电子管,

占地足足170平方,重达30吨,

这样的电脑可不是随随便便就可以拥有的。

为了让人人都能用上电脑,

体积小、功耗低、更稳定的晶体管

取代了电子管,

集成电路也随之应运而生。

有了晶体管和集成电路,

电路的规模越来越大,

体积却能够越做越小。

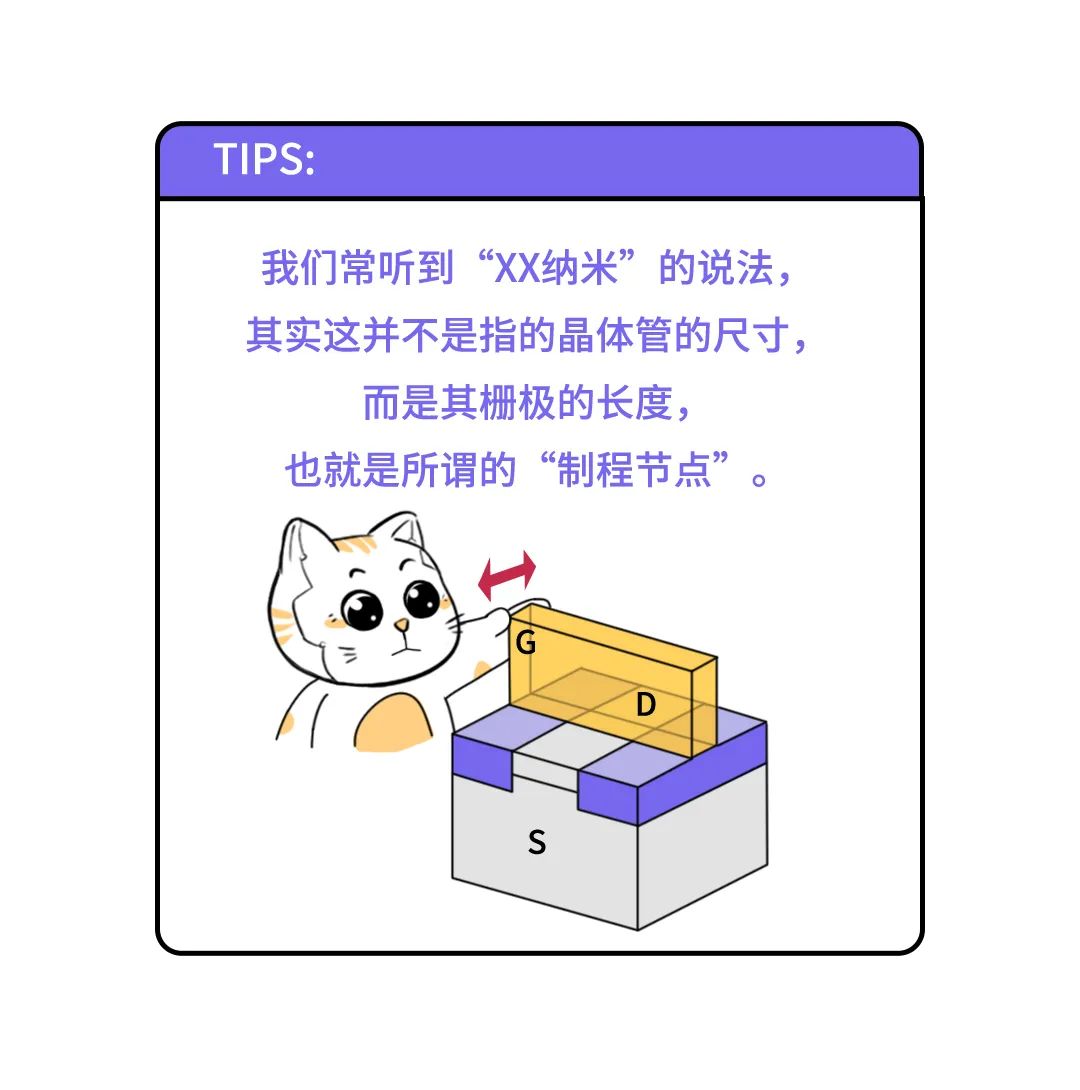

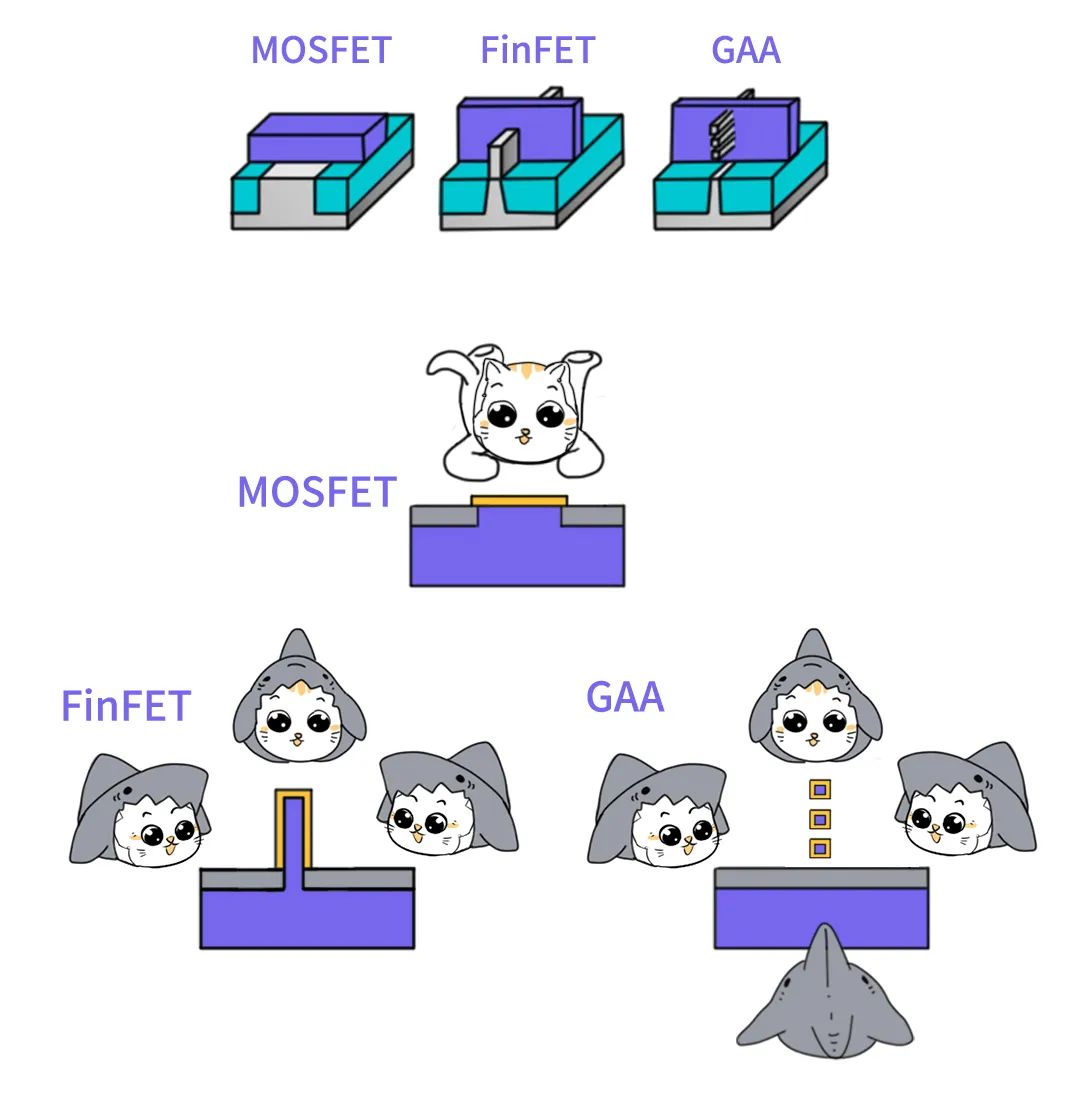

开山之石──MOSFET

1960s,MOSFET晶体管诞生了,

译为“金属氧化物半导体场效应晶体管”。

它可以看作是一种平面结构的晶体管,

由三个区域组成:

源极(S)、漏极(D)和栅极(G)

MOSFET的工作原理很简单,

栅极类似于一个控制电压的闸门,

若给栅极G施加电压,闸门打开,

电流就能从源极S通向漏极D;

撤掉栅极上的电压,闸门关上,

电流就无法流过S/D极间的通道。

一个比较传统的MOSFET长度大概100纳米,

那怎么理解这个长度呢?

我们的头发丝直径大约0.1毫米,

已经是MOSFET的1000倍了。

横空出世──FinFET

随着元件尺寸缩小,栅极的长度也越做越短,

当制程小于20nm时,麻烦出现了:

MOSFET的栅极难以关闭电流通道,

躁动的电子无法被阻拦,

漏电现象屡屡出现,功耗也随之变高。

为了减少漏电,

胡正明教授发明了晶体管的立体结构,

他将电流通道做成很薄的竖片,

将其三面都用栅极包夹起来,

控制通道关闭的效率就高多了。

这种结构长得很像鲨鱼背鳍(Fin),

因此也被称为FinFET晶体管。

FinFET技术一路披荆斩棘,

成为了先进制造市场上的先锋。

但当制造工艺微缩到3nm时,

漏电“魔咒”又hold不住了。

闪耀新星──GAA

既然三面包夹还在漏电,

那就四面统统包起来试试!

Gate-all-Around a.k.a GAA(全环绕栅)

是FinFET技术的终极进化版。

通过堆叠多个水平的纳米线,

让栅极包裹无死角,

精确控制电流通道,打破漏电“魔咒”。

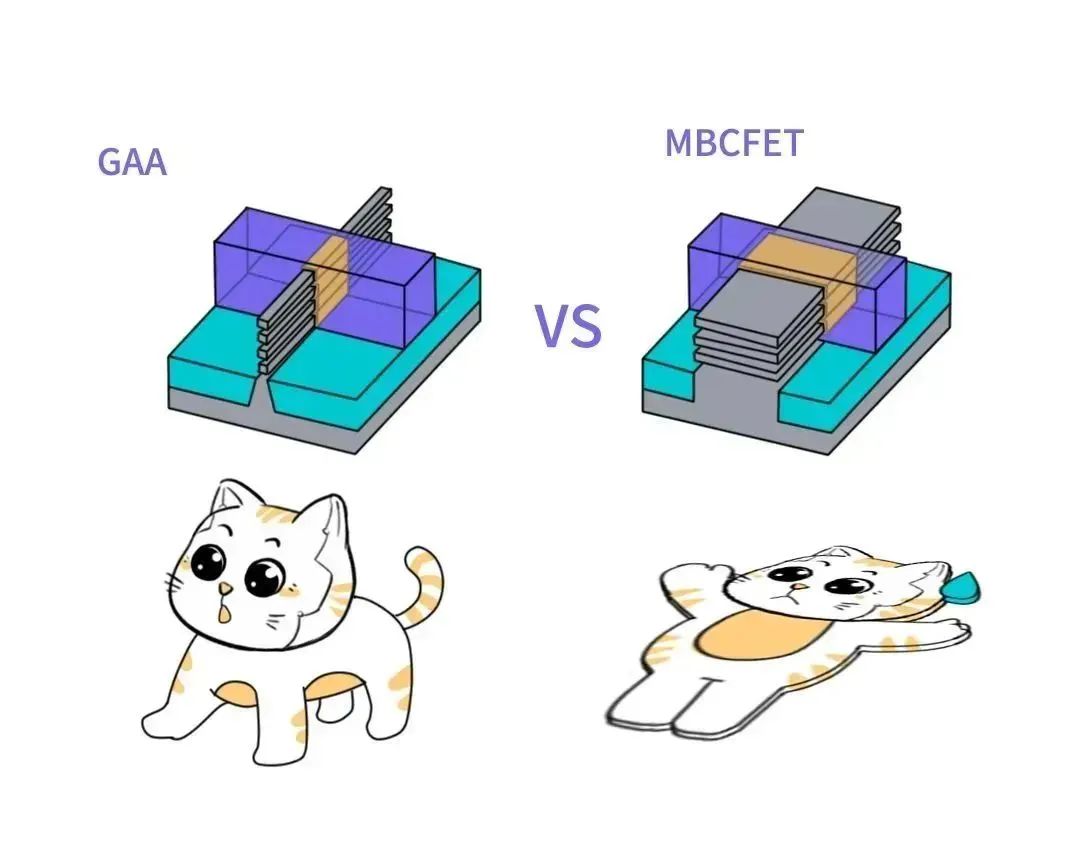

由于GAA与FinFET技术相似度很高,

厂商在3nm制成工艺上选择了不同的道路。

三星选择直接上马GAA技术,

而台积公司则试图深度改进FinFET。

2nm制程上巨头们同归殊途,

不约而同都选择了GAA,

看来,未来能够接棒FinFET,

提升至下一代技术的非GAA莫属。

此外,三星设计出另一种GAA形式──

MBCFET(多桥-通道场效应管)。

多层纳米片替代了GAA中的纳米线,

更大宽度的片状结构增加了接触面,

在保留了所有原有优点的同时,

还实现了复杂度最小化。

新思科技和代工厂长期紧密合作,

通过DTCO

(Design Technology Co-optimization)

创新协同优化FinFET,

提供面向FinFET/GAA工艺技术的解决方案,

并积极支持更先进的新型晶体管工艺,

携手推进半导体产业持续开拓未来。

原文标题:FinFET到GAA:先进制程,先要“支棱起来”

文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

-

新思科技

+关注

关注

5文章

807浏览量

50398

原文标题:FinFET到GAA:先进制程,先要“支棱起来”

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

三星SF4X先进制程获IP生态关键助力

先进制程面临哪些挑战

M31 12纳米GPIO IP获国芯科技采用,点亮先进制程车用电子芯片创新

台积电美国芯片量产!台湾对先进制程放行?

环球晶获4.06亿美元补助,用于12英寸先进制程硅晶圆等扩产

IBM与Rapidus在多阈值电压GAA晶体管技术的新突破

三星芯片代工新掌门:先进与成熟制程并重

苹果加速M5芯片研发,争夺AI PC市场,台积电先进制程订单激增

喆塔科技先进制程AI赋能中心&校企联合实验室落户苏州

FinFET到GAA:先进制程,先要“支棱起来”

FinFET到GAA:先进制程,先要“支棱起来”

评论