产品描述

Versal HBM 栈可通过内部 HSM0 参考时钟来进行时钟设置,此参考时钟是由 CIPS 或外部时钟源生成的。

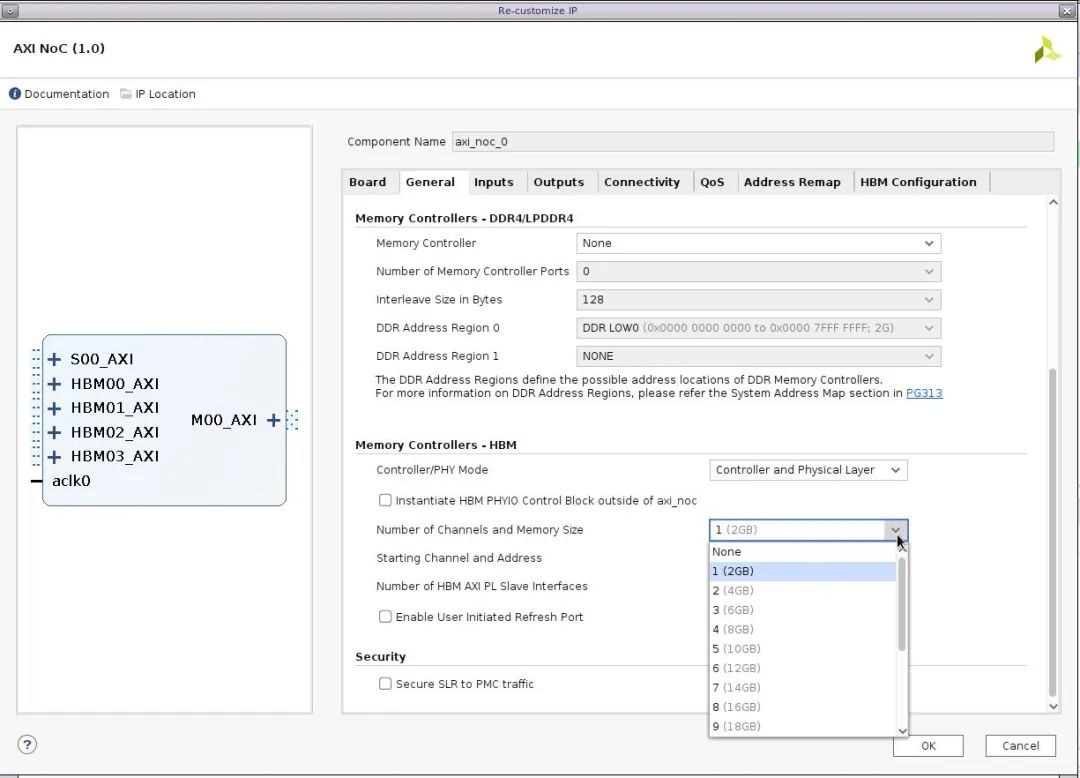

通过 AXI NoC 配置 GUI 启用 HBM 时,将显示一个额外的“HBM Configuration”(HBM 配置)选项卡。以下截屏显示 AXI NoC 配置,其中已启用 HBM 通道并导致出现“HBM Configuration”选项卡:

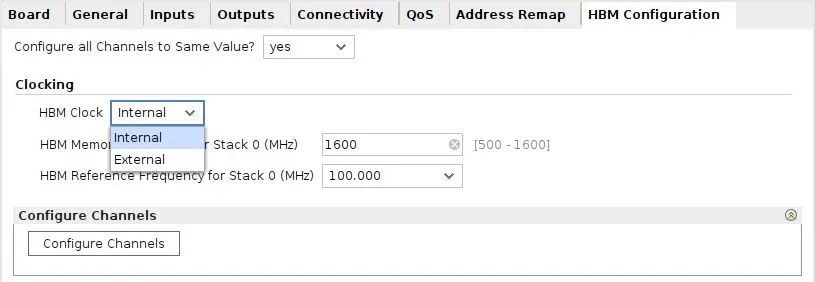

在“HBM Configuration”选项卡中,用户可以通过“HBM Clock”(HBM 时钟)下拉菜单选择“Internal”(内部)或“External”(外部)源,如下所示:

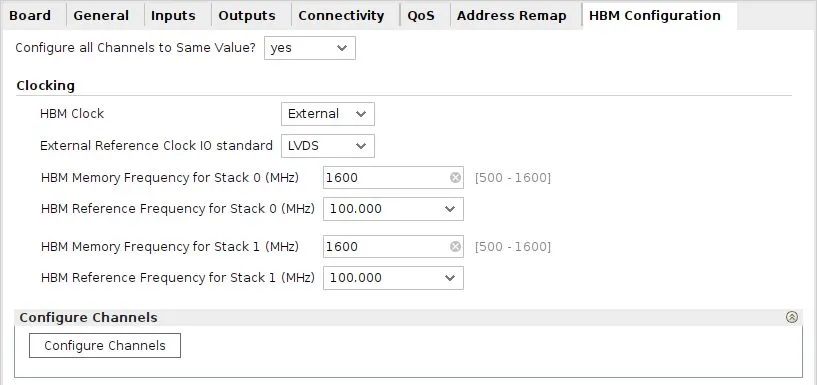

用户可搭配 Versal HBM 系列器件来使用单栈或双栈 HBM 器件。每个 HBM 栈都需要参考时钟。当 AXI NoC 实例配置为同时启用这 2 个 HBM 栈后,GUI 会自动更新 2 个时钟源。

使用 HBM 栈时,这两个栈应同时使用内部时钟设置或者同时使用外部时钟设置。使用 External 时钟设置时,两者应使用相同的“External Reference Clock IO Standard”(外部参考时钟 IO 标准)选项。

示例如下:

当 HBM 栈配置为使用 Internal 时钟设置时,工具将自动把器件配置为根据“HBM Reference Frequency for Stack”(HBM 栈参考频率)字段中设置的频率来生成并传输 HSM0 时钟。

解决方案

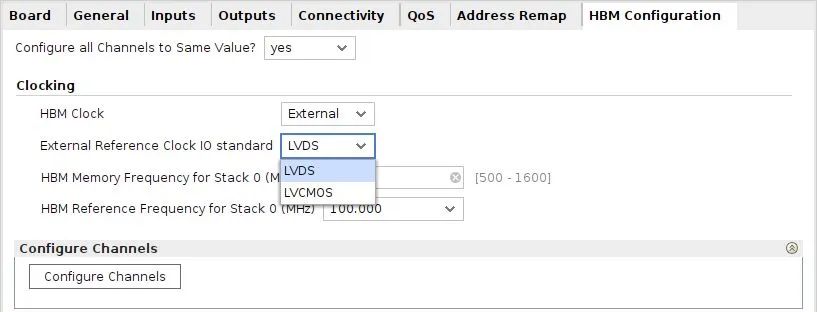

为 Versal HBM 系列参考时钟使用 External 时钟设置时,可以选择 LVDS 或 LVCMOS I/O 标准,如下所示:

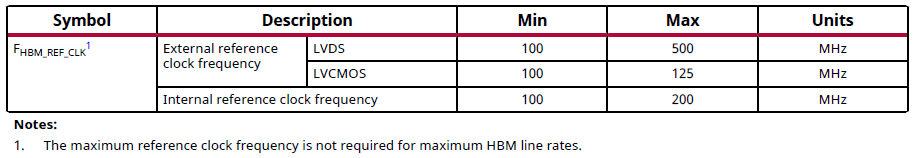

LVDS 和 LVCMOS 的最小时钟频率均为 100MHz,而其各自的最大时钟频率分别为 500MHz 或 125MHz,如下所示:

如需了解此信息以及有关 Versal HBM 器件要求的其他详细信息,请参阅《Versal HBM 系列数据手册:DC 和 AC 开关特性》(DS960)

https://docs.xilinx.com/r/en-US/ds960-versal-hbm

外部参考时钟应保持稳定运行一段时间,然后才能启动 HBM 栈。

外部参考时钟应持续运行,既不停止也不更改时钟周期。

外部参考时钟的 RMS 抖动应少于 3ps,占空比应为 50/50。

不支持扩展频谱时钟设置。

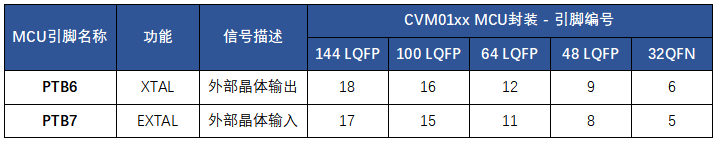

HBM 参考时钟管脚名称采用 C4CCIO_PAD0_800/801 和 C4CCIO_PAD1_800/801 格式,其中 800 和 801 表示器件上的特定 HBM 栈。PAD0 是“P”侧,PAD1 则是“N”侧。

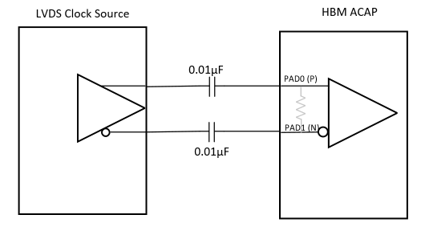

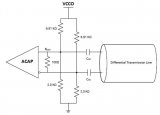

下图显示了使用 LVDS、LVCMOS 或 Internal 时钟设置选项时的外部电路要求。

LVDS

将 0.01µF 电容器与 P 管脚和 N 管脚串联,如下所示:

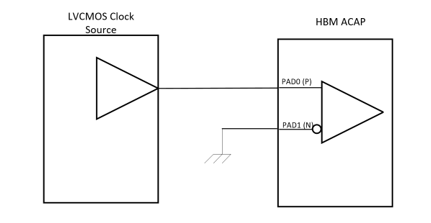

LVCMOS

将 P 输入直接连接到时钟源,将 N 输入接地,如下所示:

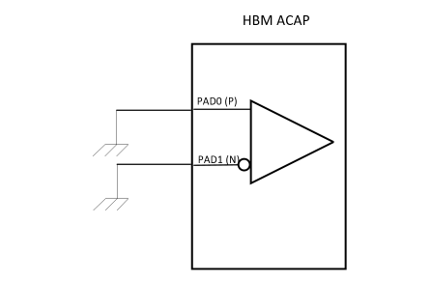

内部时钟设置

使用内部时钟选项时,P 输入和 N 输入都接地,如下所示:

重要

使用任一外部时钟设置选项(LVDS 或 LVCMOS)时,无需其他 I/O 标准约束或用户干预。这些端口不需要额外的 I/O 标准或 I/O 约束,所以手动添加额外标准或约束将会生成错误。

审核编辑:汤梓红

-

时钟

+关注

关注

11文章

2000浏览量

135246 -

NoC

+关注

关注

0文章

43浏览量

12219 -

AXI

+关注

关注

1文章

145浏览量

18023 -

HBM

+关注

关注

2文章

435浏览量

15885 -

Versal

+关注

关注

1文章

176浏览量

8545

原文标题:开发者分享|Versal HBM 系列 - 外部参考时钟设计指南文章

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

DSP芯片如何选择外部时钟?

Xilinx宣布7nm Versal AI Core和Versal Prime系列器件全面量产出货

Versal ACAP DDRMC-DDR4、LPDDR4和LPDDR4X外部参考时钟设计指南

Versal ACAP收发器向导 LogiCORE IP产品指南

用于PCI Express的Versal ACAP集成块产品指南

AMD Versal HBM 自适应 SoC 已投入量产

Versal HBM系列外部参考时钟设计指南文章

Versal HBM系列外部参考时钟设计指南文章

评论