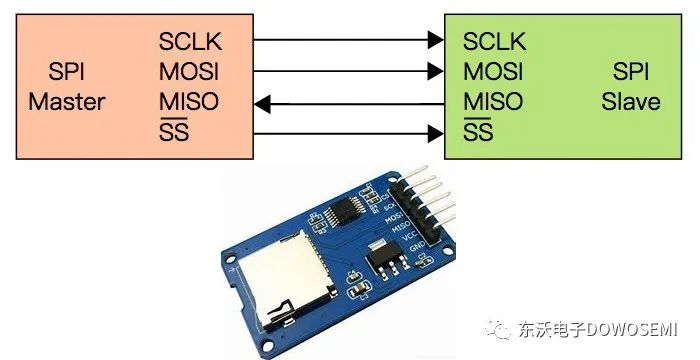

串行外设接口(Serial Peripheral Interface),简称SPI接口,是一种高速、全双工、同步的通信总线接口,可以使单片机与各种外围设备以串行方式进行通信以交换信息。SPI 在芯片的管脚上占用四根线,节约芯片的管脚,同时为PCB的布局节约空间,越来越多的芯片集成了这种通信协议。

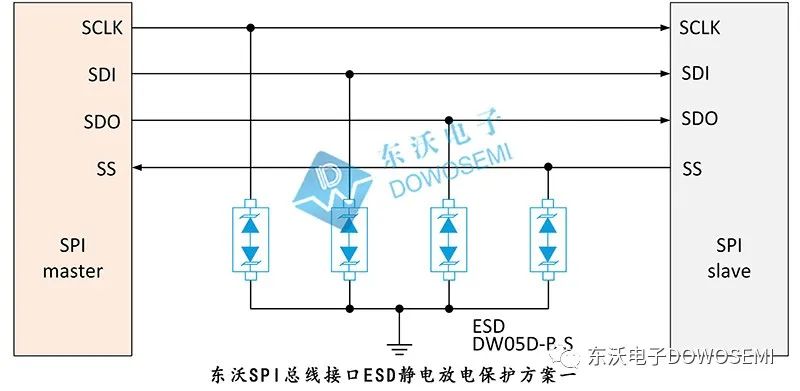

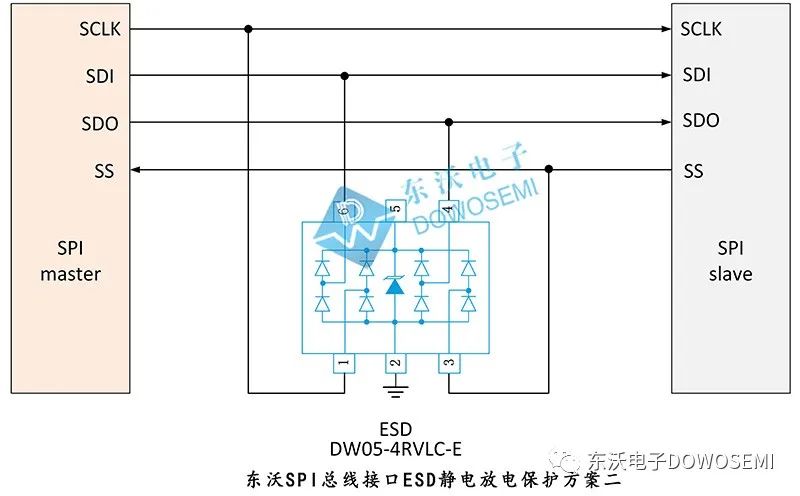

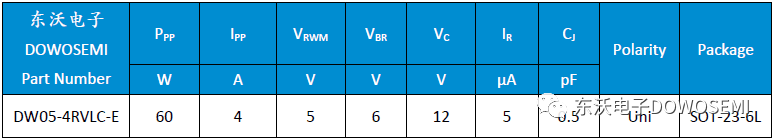

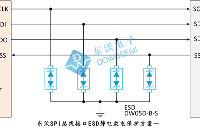

众所周知,对于通信总线接口而言,ESD静电放电防护是一项挑战。针对SPI通信总线接口ESD静电放电问题,东沃电子(DOWOSEMI)技术推荐选用ESD静电保护二极管DW05D-B-S或DW05-4RVLC-E做防护 。东沃SPI总线接口ESD静电放电保护方案设计图如下所示:

从上图可知,东沃SPI总线接口ESD静电放电防护方案设计图有两种,方案一选用了分立式ESD保护二极管DW05D-B-S,方案二选用了集成式多路 ESD保护二极管DW05-4RVLC-E。DW05D-B-和DW05-4RVLC-E导通电压精度高、响应速度快、寄生电容值低、钳位电压低,在不影响数据传输的前提下,能够满足IEC 61000-4-2 Level 4静电放电防护需求,且做到成本最优化。

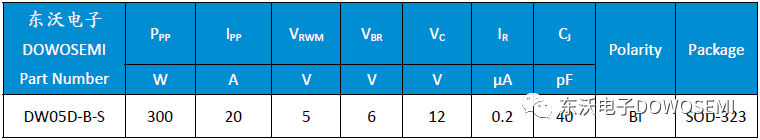

有客户问,东沃SPI总线接口ESD静电放电保护方案一和方案二有什么区别呢?查看方案一可知,东沃技术推荐选用4颗分立式ESD保护二极管DW05D-B-S,工作电压5V、击穿电压6V、峰值脉冲电流20A、12V低钳位电压、SOD-323封装,占用空间比较大,结电容40pF,比较适合用于传输信号速率要求不是很高的场合。查看方案二可知,东沃技术推荐选用集成式多路 ESD保护二极管DW05-4RVLC-E,工作电压5V、击穿电压6V、峰值脉冲电流4A、12V低钳位电压、SOT-23-6L封装,体积小,结电容0.5pF,适用于通信速率要求更高的场合和产品。

审核编辑:刘清

-

二极管

+关注

关注

148文章

9837浏览量

168219 -

ESD

+关注

关注

49文章

2130浏览量

173728 -

单片机

+关注

关注

6045文章

44665浏览量

640570 -

SPI接口

+关注

关注

0文章

260浏览量

34743 -

静电放电保护

+关注

关注

0文章

12浏览量

2514

原文标题:如何对SPI总线接口进行ESD静电放电保护?

文章出处:【微信号:杭州东沃电子科技有限公司,微信公众号:杭州东沃电子科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ESD接口处需要静电保护

什么是ESD(静电放电)及ESD保护电路的设计

ESD(静电放电)介绍及ESD保护电路的设计

LIN总线ESD静电防护方案设计图

DC 3.3V 接口ESD静电保护

ESD静电放电产生的原理和危害

ESD静电阻保护器件的应用

ESD保护装置·对策元件基础知识——ESD(静电放电・浪涌)保护装置・对策元件是什么?

ESD保护装置·对策元件基础知识——ESD(静电放电・浪涌)保护装置・对策元件的种类

如何保护麦克风Microphone接口免受ESD静电放电威胁?

如何对SPI总线接口进行ESD静电放电保护?

如何对SPI总线接口进行ESD静电放电保护?

评论