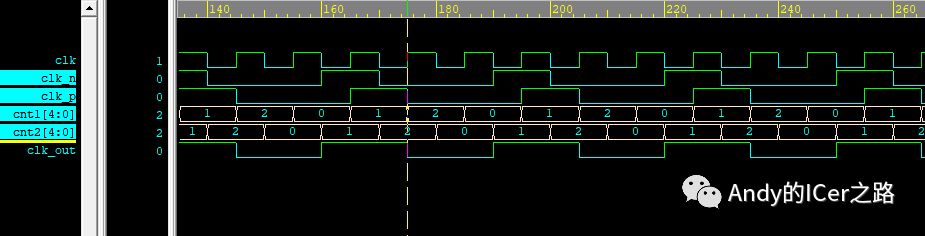

入门从简单开始,先来个三分频分析一下。三分频其实就是把输入时钟的三个周期当作一个周期,具体波形如图所示。(本文只针对于占空比为50%的分析)

此处还是用计数器的方式完成设计,但是与偶分频有所区别。因为奇数分频的频率与输入的时钟频率有相位差,因此需要增加一些信号完成设计。

clk_n是下降沿触发的信号,clk_p是上升沿触发的信号,通过计数并且因为不同的边沿触发而形成一定的相位差,并将两个信号进行或门处理,最后输出的就是奇数分频结果了。

缺点分析:奇数分频需要在两个触发器之后再加一个组合逻辑门,这个组合逻辑门不仅会增加时钟的延时,而且在设计当中可能出现毛刺。

具体的占空比为50%的任意奇数分频的代码如下所示。

`timescale 1ns/1ps

module CLK_DIV #(parameter DIV_NUM=3)(

input clk,

input rst_n,

output clk_out

);

//all odd div

reg [4:0] cnt1,cnt2;

reg clk_p,clk_n;

always @(posedge clk,negedge rst_n)

if(!rst_n) begin

cnt1 <= 0;

clk_p <= 1'b0;

end

else begin

if(cnt1 == DIV_NUM-1) begin

cnt1 <= 0;

clk_p <= clk_p;

end

else begin

cnt1 <= cnt1 + 1'b1;

if(cnt1 == ((DIV_NUM-1)/2)-1 || cnt1 == DIV_NUM-2)

clk_p <= ~clk_p;

end

end

always @(negedge clk,negedge rst_n)

if(!rst_n) begin

cnt2 <= 0;

clk_n <= 1'b0;

end

else begin

if(cnt2 == DIV_NUM-1) begin

cnt2 <= 0;

clk_n <= clk_n;

end

else begin

cnt2 <= cnt2 + 1'b1;

if(cnt2 == ((DIV_NUM-1)/2)-1 || cnt2 == DIV_NUM-2)

clk_n <= ~clk_n;

end

end

assign clk_out = clk_p | clk_n;

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

分频器

+关注

关注

43文章

447浏览量

49876 -

计数器

+关注

关注

32文章

2256浏览量

94476 -

触发器

+关注

关注

14文章

2000浏览量

61132 -

输入时钟

+关注

关注

0文章

3浏览量

7255 -

CLK

+关注

关注

0文章

127浏览量

17158

发布评论请先 登录

相关推荐

奇数分频如何得到呢? 解读奇数分频和逻辑分析仪(ILA)的使用

前言: 偶数分频容易得到:N倍偶数分频,可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数

需要讲解一个占空比50%的奇数分频器的原理

本帖最后由 haozix521 于 2013-10-4 20:42 编辑

想做一个占空比50%的奇数分频器,但是不是很了解这其中的意思。网上的资料都是这样讲的“对于实现占空比为50%的N倍奇数分频

发表于 10-04 20:35

基于FPGA 的等占空比任意整数分频器的设计

基于FPGA 的等占空比任意整数分频器的设计

给出了一种基于FPGA 的等占空比任意整数分频电路的设计方法。首先简要介绍了FPGA 器件的特点和应用范围, 接着讨论了

发表于 02-22 14:22

•39次下载

分频器的作用是什么 半整数分频器原理图分析

分频器主要分为偶数分频、奇数分频、半整数分频和小数分频,如果在设计过程中采用参数化设计,就可以随时改变参量以得到不同的

发表于 02-01 01:28

•1.7w次阅读

偶数分频、奇数分频、半整数分频和小数分频详解

初学 Verilog 时许多模块都是通过计数与分频完成设计,例如 PWM 脉宽调制、频率计等。而分频逻辑往往通过计数逻辑完成。本节主要对偶数分频、奇数分频、半整

介绍一下奇数分频器的设计

介绍一下奇数分频器的设计

评论