最近,需要使用VCS仿真一个高速并串转换的Demo,其中需要用到Vivado的SelectIO IP核以及IDELAYCTRL,IDELAY2原语。而此前我只使用VCS仿真过Quartus的IP核。

而我的VCS装在Ubuntu,Vivado装在Win10,尝试了export仿真库等方法,奈何通通失败了,如果实在折腾不好,恐怕只能在Ubuntu下再装一个Vivado for Linux版了。

经过一系列艰难的搜索资料之后(主要是网上的VCS资料太少),我找到了Vivado的IP核仿真库文件夹。

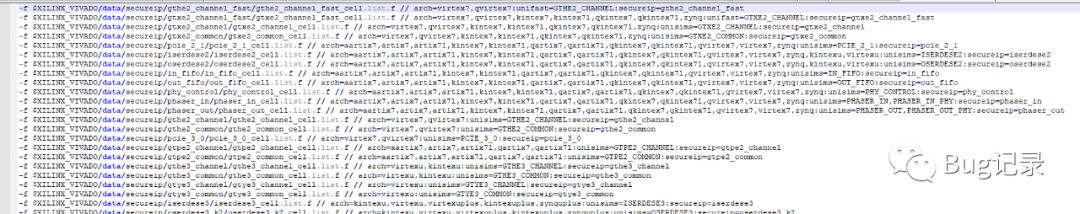

我使用的是Verilog,所以我需要的库在**XILINX/Vivado/2016.1/data/verilog/src (**XILINX是Vivado的安装路径),把里面的unifast, unimacro, unisims, unisims_dr, xeclib文件夹和glbl.v复制到自己的仿真文件夹,并在makefile里的vcs命令下加入相关库,如下图:

正当我以为已经将需要的库加载完成,在命令行输入make comp的时候,命令行却无情的报错,报错信息如下:

真是令人头秃,但是没办法,谁叫我这么闲呢,于是我又开始在网上搜索这个错误信息,知道找到了xilinx的一篇Answer:

这篇Answer,很粗略的回答了错误是因为IP核调用了Xilinx SecureIP包中的一部分库,而这个库是加密的,后面推荐的方法看的是云里雾里,但我查询一些资料之后,原来这个secureIP文件夹也是在Vivado的安装目录下,这个时候就需要使用电脑搜索文件的神器——Listrary。

SecureIP包在$XILINX\\Vivado\\2016.1\\data\\secureip下,我直接将整个"secureip"文件夹复制到ubuntu文件夹下。

注意,此时还有几个步骤需要做:

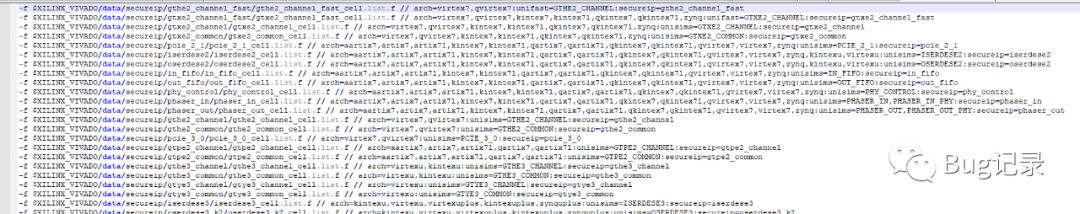

- 将secureip下的secureip.list.f里面的路径做修改,如下图

修改后

工程量可能有些大,这时候可以把不需要的库路径删去,保留我们需要的。

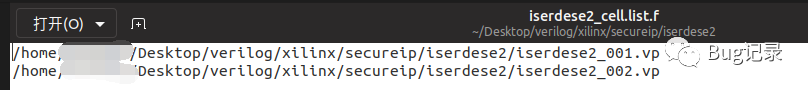

- 到secureIP下找到需要用到的IP核文件夹,并修改文件夹里的f和vf文件;例如,我需要使用的是iserdese2和oserdese2文件夹,

iserdese2_cell.list.f修改如下:

iserdese2_cell.list.vf修改如下:

注意,前面secureip.list.f包含多少个库,就需要改多少个库文件夹里面的这两个文件,所以可以将不需要的库路径删去,等需要的时候再加。

- 在makefile里面增加文件包含,写法如下

- 在vcs编译的命令中需要加入-lca,否则vcs会一直报错提示加入这个命令;

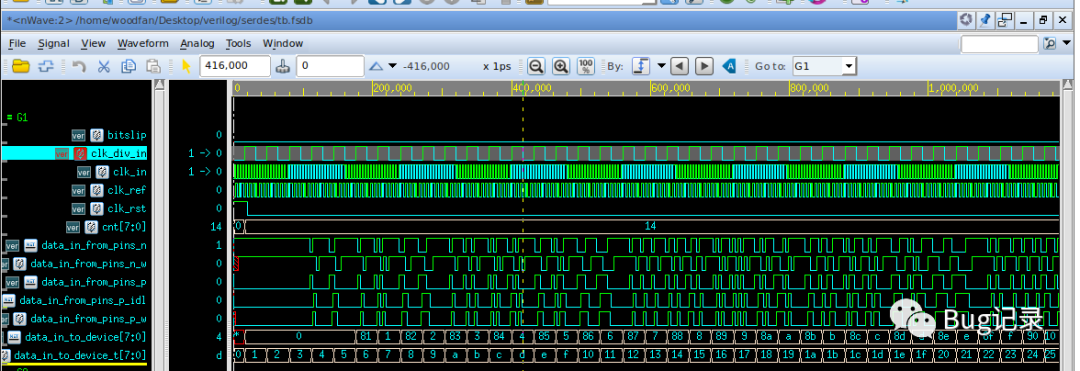

最终效果,仿真成功!

希望这个方法总结可以帮助到其他人,不过说不定大家用的方法更加简单方便快捷呢?

-

VCS

+关注

关注

0文章

79浏览量

9605 -

Vivado

+关注

关注

19文章

812浏览量

66511 -

Ubuntu系统

+关注

关注

0文章

91浏览量

3934

发布评论请先 登录

相关推荐

VCS独立仿真Vivado IP核的一些方法总结

VCS独立仿真Vivado IP核的一些方法总结

评论