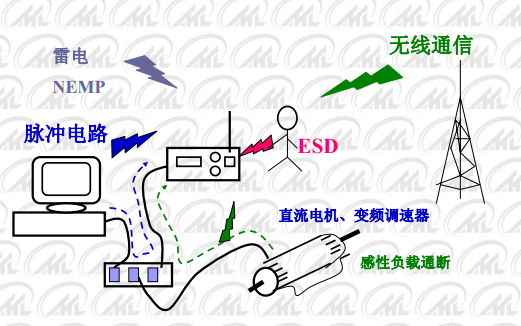

静电放电对电路的影响主要是通过电压、电流和能量传递的方式产生的。静电放电是由于电荷积累在物体表面,当电荷之间或物体与接地之间存在电势差时,会发生电荷的突然释放,形成放电现象。

静电放电可能对电路产生以下几种影响:

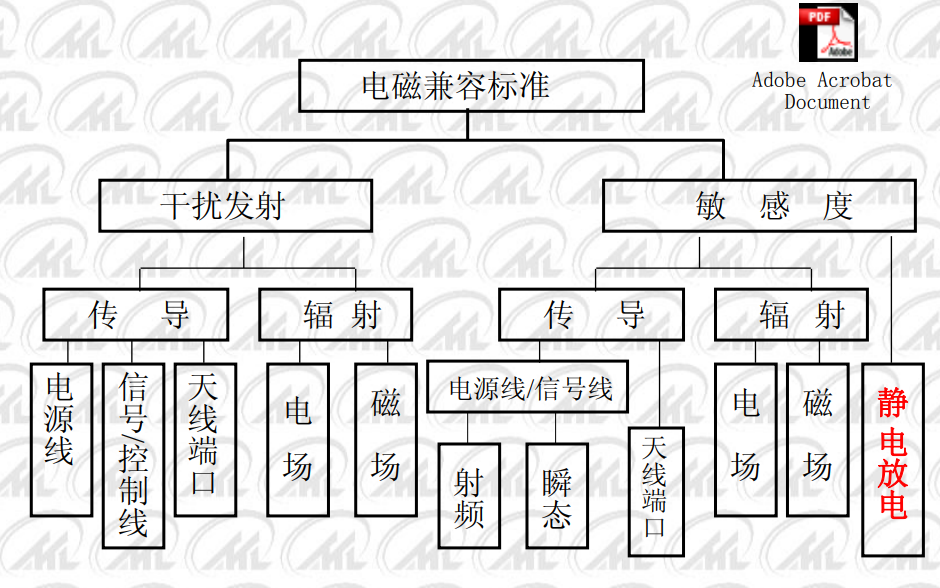

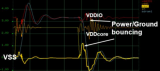

电压干扰:静电放电会引起电路中的瞬态电压变化。这些电压变化可能超过电路元件的额定电压,导致元件失效或损坏。例如,电容器、晶体管等器件可能无法承受过高的电压。

电流干扰:静电放电产生的电流脉冲可以干扰电路中的正常电流流动。这种干扰可能导致电路中的信号失真、误触发或产生噪声。尤其是在高频电路中,静电放电引起的电流干扰可能会干扰电路的正常工作。

热效应:静电放电会产生高能量的电弧或火花,这些电弧或火花可能引起局部的高温。在电路中,这种高温可能导致电路元件的热损坏、熔断或引发火灾。

电磁辐射:静电放电产生的电流变化会引起辐射电磁场。这些电磁辐射可能对电路中的敏感元件(如传感器、放大器等)造成干扰,导致信号质量下降或产生误差。

为了减轻静电放电对电路的影响,可以采取以下措施:

地接:通过将电路或设备接地,可以将静电放电引导到地面,减少对电路的影响。

防静电措施:使用防静电材料或涂层,减少静电的积累和释放,从而降低静电放电的发生概率。

绝缘和屏蔽:对于对静电放电敏感的电路或元件,可以采用绝缘层或屏蔽来隔离它们,减少外界的干扰。

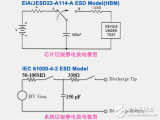

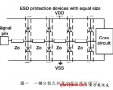

过电压保护:在电路中添加过电压保护元件,如电压稳压器、过压保护二极管等,以防止过高的电压对电路造成损害。

设计优化:在电路设计过程中考虑静电放电的可能影响,并采取合适的电路布局、元件选择和排布方式,以减少静电放电的影响。

我司是专业的第三方检测机构、致力于各类电子电器、汽车电子、医疗器械的检测、认证、整改一站式服务,有需要的朋友可以联系我们,我们将为你提供最专业的服务

审核编辑黄宇

-

电路设计

+关注

关注

6746文章

2800浏览量

220395 -

静电放电

+关注

关注

4文章

312浏览量

46090

发布评论请先 登录

ESD静电放电造成时钟芯片RAM归零问题

系统层级静电放电与芯片层级静电放电有什么差异

详解静电放电保护

系统层级静电放电与芯片层级静电放电的差异

静电放电ESD的介绍和原理及解决方法概述

静电放电ESD的原理和详细资料概述

ESD静电放电分析及整改总结

静电放电对电路设计造成影响机理

静电放电对电路设计造成影响机理

评论