6月4日,在北京举办的第31届中国国际信息通信展览会(PT Expo 2023)上,国内领先的***设计及应用商思朗科技,对外正式发布了基于公司自主研发MaPU内核架构的芯片UCP4008小基站方案,同时还预发布了一款完全国产化的低成本、低功耗的家庭基站系统级芯片Femto SoC。

作为一家成立于2016年的半导体高科技企业,思朗科技在芯片设计和应用领域的能力十分强大。公司自主研发的MaPU内核芯片,是一款基于全新架构理念的代数处理器,完美融合了CPU的可编程性及通用性、FPGA的灵活性以及ASIC的高效性,其运算能力和性能功耗比的优势相当明显。而5G小基站核心芯片UCP4008,正是MaPU内核芯片架构在无线通信边缘侧的杰出应用成果。

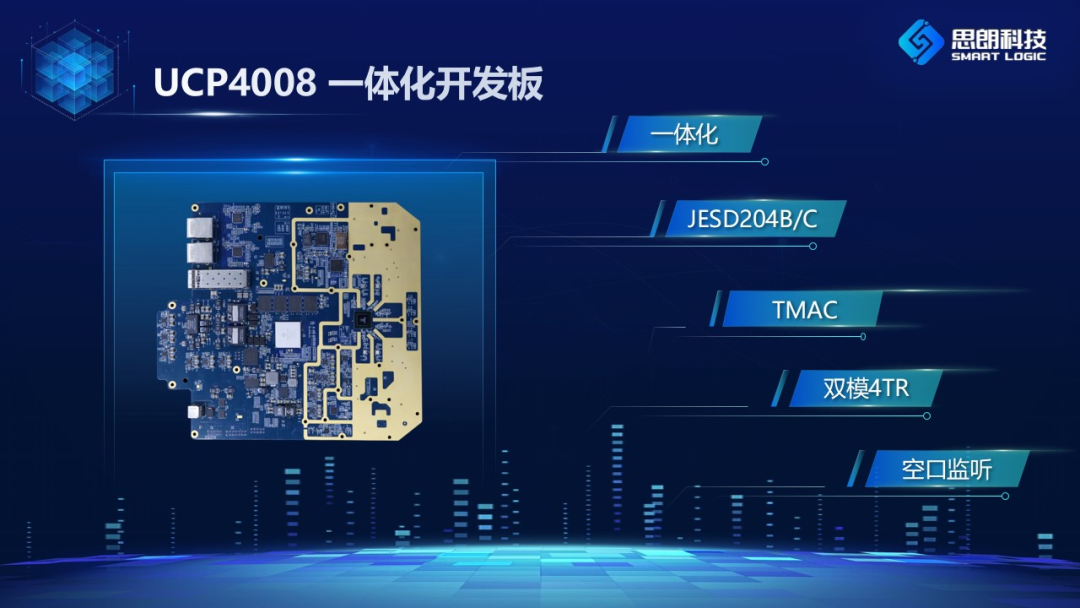

UCP4008芯片采用了灵活先进的软件无线电架构,内部集成了MaPU内核和NPU内核,是一款全栈的基站芯片。UCP4008单芯片即可实现整个基站L1、L2和L3的处理,运行效率高,且硬件成本低。UCP4008芯片提供的接口资源非常丰富,提供了包括PCIe、CPRI/eCPRI、JESD204B/C和T(G)MAC等在内的高速、低速接口,同时支持GPS、1588V2、SyncE和空口等多种同步方式。

在发布会现场,思朗科技对外展示了几套开发板设计,其中最引人注目的是一块基于UCP4008的一体化开发板。这块板卡仅仅使用一个UCP4008芯片,就可以支持2个100M的4天线5G小区,是一个集成化程度相当高,兼具低成本、低功耗特点的一体化基站解决方案。

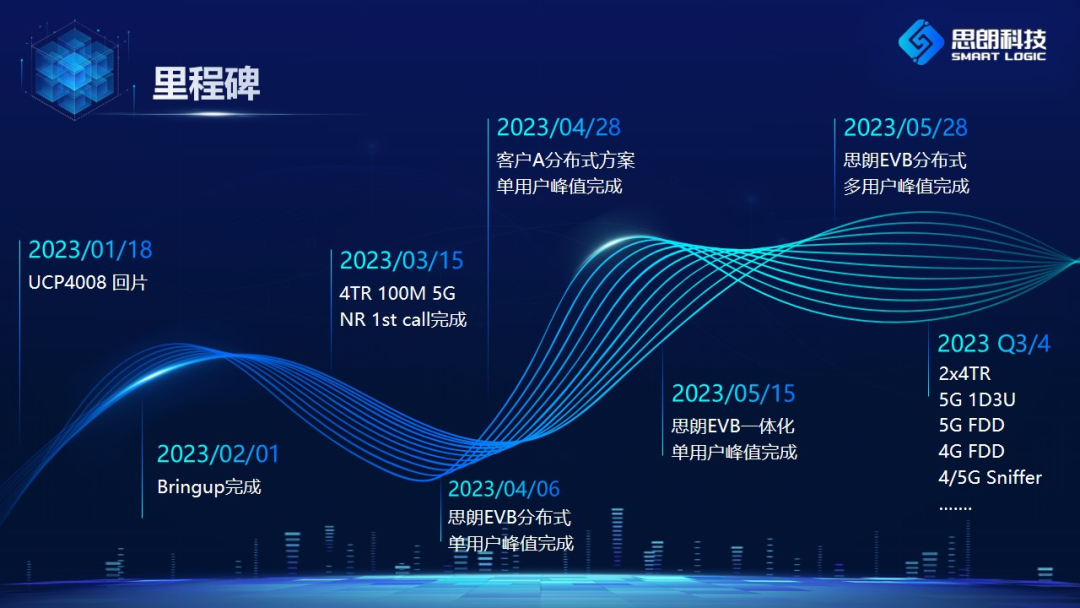

据思朗科技的市场总监周建锋介绍,UCP4008的研发过程非常顺利,体现了让客户都颇为惊叹的“思朗速度”:从2023年1月18号正式回片起,思朗仅用了不到半个月就完成了Bringup;在随后的2个月内,思朗接连不断地取得重大里程碑进展,包括完成4TR 100M 5G NR 1st call、分别基于EVB板卡和客户的硬件板卡达到分布式基站形态的单用户峰值;紧接着又在5月份相继实现了基于思朗EVB 板卡一体化基站形态的单用户峰值和多用户峰值,并且多用户峰值的稳定性超过24小时,几乎保持着每个月都有1-2个重大研发进展突破。

至此,思朗科技向外界完整展示了基于UCP4008芯片的解决方案,包括芯片和硬件平台、SDK、物理层和协议栈(第三方)。思朗还拥有一支专业的工具链团队,开发维护基于MaPU内核的集成开发环境,和自研的编译器、模拟器和调试器等。

除了UCP4008小基站方案以外,本次思朗产品发布的另一个重要环节是思朗Femto SoC的预发布,这款芯片同样采用MaPU内核架构,并且思朗团队在开发时借鉴了UCP4008的开发经验,采用了积极和稳妥的技术路线,其设计目标是全球成本最低、性能功耗比最高的家庭基站系统级芯片。据透露,思朗Femto SoC计划将于2024年Q1流片,2024年Q2回片。

-

芯片

+关注

关注

455文章

50732浏览量

423268 -

soc

+关注

关注

38文章

4163浏览量

218174 -

国产芯片

+关注

关注

2文章

249浏览量

29691

原文标题:遇见PT Expo 2023 | 思朗科技正式发布UCP4008小基站方案并预发布国产Femto SoC

文章出处:【微信号:txshj123,微信公众号:通信世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

思瑞浦发布汽车传感器网络ASN收发器

思必驰AI办公本Turbo重磅发布

思仪科技发布4457M系列数字示波器新品

ESP8266为什么无法在网站上发布数据?

RK3568J“麒麟”+“翼辉”国产系统正式发布,“鸿蒙”也正在路上!

ROS让机器人开发更便捷,基于RK3568J+Debian系统发布!

龙芯 2K0300 蜂鸟开发系统正式发布!!

思特威与主控SoC厂商推出黑光全彩全天候录制解决方案

蓝芯科技正式发布智能搬运机器人VMR-FR31510L

芯来科技正式发布基于RISC-V处理器的HSM子系统解决方案

思朗科技正式发布UCP4008小基站方案并预发布国产Femto SoC

思朗科技正式发布UCP4008小基站方案并预发布国产Femto SoC

评论