基于DWC2的USB驱动开发-0x0D PHY寄存器读写代码编写与测试 (qq.com)

1.1 前言

前面我们详细讲解了ULPI接口,一般情况不需要关注ULPI总线接口上的信号。但有时候我们需要进行底层问题的分析,此时就需要抓取ULPI总线上的数据来进行分析,此时就需要使用逻辑分析进行信号抓取,这个时候一个好用的逻辑分析仪就非常重要了。

我们使用Acute的TL4234B逻辑分析仪抓取ULPI总线数据,该逻辑分析仪支持ULPI解码非常方便。

该逻辑分析仪的使用参考https://mp.weixin.qq.com/s/bCdgCNsGPbYjSzjv8VJyRA。

测试代码见https://mp.weixin.qq.com/s/r64ayPKzJtLxpUvsmZYvWg

设置好相应的信号之后可以按照如下添加ULPI协议分析通道

1.2 读寄存器

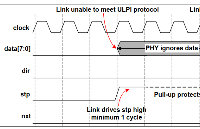

读寄存器的标准时序如下

我们实际抓到的读0寄存器,波形如下

可以看到分析仪自动解析出了过程

对应测试代码

res = hw_dwc2_read_phyreg(0x00,®val,1000);

if(res != 0)

{

return res;

}

usb_hal_info("[VIDL]:0x%x\\r\\n",regval);

我们详细分析下如下过程

(1) 此时DIR为低,总线所有权归LINK所有,但是LINK没有数据要发送,所以驱动数据线全0。

(2) 此时软件进行读立即寄存器0的操作,对应的命令字节为0xC0,发送到总线上,但是NXT被PHY拉为低,说明PHY没有接收,LINK只能继续重发

(3) 重发0xC0,此时NXT被PHY拉高,说明被PHY接收了。

注意DIR和NXT应该在CLK的上升沿处跳变,但是由于信号一致性问题CLK不是很完美,所以逻辑分析抓出来的CLK信号有一些偏移,占空比也不是50%.

(4) DIR低到高之后的CLK上升沿开始是turnaround

(5) 该CLK上升沿,LINK锁存PHY发出的数据0x24

(6) DIR由高到低之后的CLK上升沿开始是turnaround

(7) 回到空闲状态,DIR为0,LINK驱动总线为0

1.3 写寄存器

写寄存器理想的时序如下

写0x16寄存器为0x55

对应代码为

hw_dwc2_write_phyreg(0x16,0x55,1000);

if(res != 0)

{

return res;

}

我们实际抓到的波形如下

可以看到分析仪自动解析出了过程

我们详细分析下如下过程

(1) 此时DIR为低,总线所有权归LINK所有,但是LINK没有数据要发送,所以驱动数据线全0。

(2) 此时软件进行写立即寄存器0x16的操作,对应的命令字节为0x96,发送到总线上,但是NXT被PHY拉为低,说明PHY没有接收,LINK只能继续重发

(3) LINK重发0x96,此时NXT被PHY拉高,说明被PHY接收了。

(4) LINK发送数据0x55,NXT为高说明PHY接收了,于是下一个周期LINK 拉高STP结束。

同样要注意DIR和NXT应该在CLK的上升沿处跳变,但是由于信号一致性问题CLK不是很完美,所以逻辑分析抓出来的CLK信号有一些偏移,占空比也不是50%.

1.4 数据收发

同样可以抓到USB数据传输时的内容进行分析

如下,不再详细分析

寄存器读写和USB数据传输的抓包数据可以参考

链接:https://pan.baidu.com/s/1oOGlc8sbEywoEmRsgEGtvw?pwd=4j92

提取码:4j92

1.5 总结

工欲善其事必先利其器,所以在USB开发中工具很重要,示波器,逻辑分析仪,USB协议分析仪等都不可少。在底层问题分析时缺少有力工具时很难进一步分析,本文分享了ULPI抓包分析,实际抓包波形因为信号质量问题可能没有那么理想,所以信号的冗余度也是很重要的,很多时候问题可能就是时序问题。

审核编辑:汤梓红

-

接口

+关注

关注

33文章

8775浏览量

152394 -

usb

+关注

关注

60文章

8033浏览量

267430 -

逻辑分析仪

+关注

关注

3文章

215浏览量

23369 -

驱动开发

+关注

关注

0文章

131浏览量

12157 -

DWC2

+关注

关注

0文章

35浏览量

170

发布评论请先 登录

相关推荐

基于DWC2的USB驱动开发-0x02 DWC2 USB2.0 IP功能特征介绍

基于DWC2的USB驱动开发-发送相关的寄存器DMA寄存器详解

基于WIN32的USB逻辑分析仪

巧用逻辑分析仪 助力单片机开发

kingst虚拟逻辑分析仪使用详解

基于DWC2的USB驱动开发-0x0A ULPI接口同步模式介绍

基于DWC2的USB驱动开发-0x0E 使用逻辑分析仪分析ULPI数据

基于DWC2的USB驱动开发-0x0E 使用逻辑分析仪分析ULPI数据

评论