后仿

相对于RTL仿真,门级仿真占用的计算资源虽然很多,但是在静态时序检查(STA)工具普遍应用之前,带时序的动态门级仿真几乎可以说是唯一的timing sign-off手段了。

那么在STA工具已经成熟的现在,门级仿真还有存在的必要吗?为什么有些公司的设计流程中还包括门级仿真这个必需的步骤呢?

可能存在以下几个原因:

检查时序约束(SDC)的完备性— 防止约束的遗漏

检查异步电路的时序—STA工具无能为力,异步处理部分在SDC约束文件中做的是fath_path处理,所以这部分时序是否满足,STA工具并不会检查也不会报出violation;

检查网表的完备性—防止综合、布局布线过程中的意外

为后续流程如功耗(Power)分析、压降(IR Drop)分析提供波形—更准确

测试向量的仿真—只有门级网表才包含扫描链,DFT逻辑的插入是否导致功能出现问题;

门级仿真分为两种:

一种是不带时序反标的门级仿真(零延时仿真,综合的网表就可以做,因为在布局布线之前,所以也叫前仿,这时由于hold没有修,所以会出现不少时序违例的情况);

一种是带时序反标(back-annotation)的门级仿真(布局布线之后的仿真,也叫后仿,这时的网表是后端做完布局布线,修补完timing的网表);

进行PR网表的后仿真时,我们需要告知仿真工具cell与cell之间的延迟,D端到Q端的延迟,这里就需要SDF文件!

前仿选项

+nospeicy

在仿真时忽略库文件中指定的延时。

+delay_mode_zero

将标准库单元中定义的延时替换为0。testbench中的 #延时也都被消除。

+notimingcheck时序检查开关,比如setup/hold/width检查等等,如使用了该option,则仿真时不检查时序,行为类似于RTL仿真。

在PR未结束,sdf反标文件还没准备好时,可用该选项忽略延时,可用于功能性的粗略检查。

但真正跑后仿真时,不可使用该选项,否则仿真有效性大大降低。

后仿选项

+sdfverbose

显示所有的sdf反标错误;

+no_notifier

可以关掉时序检查产生的不定态。通过这个命令参数可以使时序检查任务中检测到时序违例后,不影响其参数列表中的notifier的值,从而避免了notifier变化引起udp输出不定态的情况,该命令仅对notifier的值有影响,对于时序检查任务检测到的时序违例不产生任何影响;

+neg_tchk若要使用负延时检查,在编译设计时必须包含+neg_tchk选项。如果省略此选项,VCS将所有负延迟更改为0。

-negdelay

用于SDF文件中有负延迟,如果省略此选项,VCS将所有负延迟更改为0。

sdf文件反标

方法一

在makefile中调用,使用如下命令:

vcs+neg_tchk-negdelay-sdfmin|typ|maxfile.sdf

启用SDF反标。在file.sdf中指定的最小值、类型或最大值中的一种,在实例instance_name上进行反标。

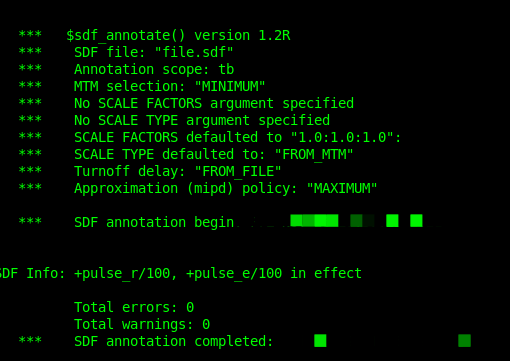

方法二 $sdf_annotate

使用$sdf_annotate将SDF文件反标到网表中:

$sdf_annotate("sdf_file"[,module_instance][,"sdf_configfile"][,"sdf_logfile"][,"mtm_spec"]

[,"scale_factors"][,"scale_type"]);

sdf_file:指定指向SDF文件的路径;

module_instance:调用$sdf_annotate模块实例的范围。

sdf_configfile:指定SDF配置文件。

sdf_logfile:指定SDF log文件,可以使用+sdfverbose显示所有的sdf反标错误。

mtm_spec:指定哪一种延迟类型,通常有三种min:typ:max,它的可能值是"MINIMUM", "TYPICAL", "MAXIMUM", or "TOOL_CONTROL"(默认值)。在仿真器读入SDF的时候,要指定使用哪一组。避免出现指定的组的时序信息不存在的情况。

scale_factors:指定min:typ:max的缩放因子,默认为三个正实数“1.0:1.0:1.0”。

scale_type:指定SDF文件中在缩放前使用的延迟值。它可能的值是“FROM_TYPICAL”、“FROM_MIMINUM”、“FROM_MAXIMUM”和“FROM_MTM”(默认);

在tb中加载sdf文件

`ifdefSDF

initial

begin

$sdf_annotate("../../rtl/post_sim/file.sdf",tb,,"sdf.log",);

end

`endif

确认成功反标

打印出Doing SDF annotation ...... Done

其他

初始化寄存器的值

在vcs编译选项里添加+vcs+initreg +random随机化赋初值,可用于对初始状态是x的寄存器。

导出VCD文件

VCD是不压缩的文本格式,兼容性好,缺点是文件太大。因此后仿先写出高压缩比的FSDB文件,再转成VCD。可指定转换起止时间、结束时间。这样一次后仿,就可以为不同的应用生成不同的VCD文件。

FSDB转VCD的工具通常在Verdi的安装目录,用法:

fsdb2vcdxxx.fsdb-oxxx.vcd-bt100ns-et200ns

其中,-bt是begin time,-et是end time;

关闭某些寄存器的时序检查notiming.list

后仿过程中可能有一些不必要或者不想检查的时序,尤其是跨时钟域的两级同步的第一级DFF出现所谓的时序违例,这是一种假的时序违例所以通常不关心它们是否有时序违例。

instance{tb.U_TOP.reg}{noTiming};

VCS +optconfigfile+notiming.list

可以用上面方法加载这个文件,这样在后仿过程中将不对这些寄存器做时序检查,避免不必要的时序问题而引起X态传递。

Note:

1.后仿开始前,一定要把详细的SDF反标报告打印出来仔细检查。需要把错误全部解决掉,警告视情况要解决大部分。带时序的后仿,一定要注意仿真器是否关闭了notimingcheck和nospecify的选项。如果有nospecify,那么SDF中的时序信息就反标不到仿真模型中(仿真模型的时序类型定义在specify block中);如果有notimingcheck,那么后仿过程中就不检查时序违例,后仿就失去了最大的意义。

2.带时序的后仿开始阶段,建议dump一些波形出来,看看波形上的延时和SDF中的延时信息是否保持一致,这有助于对反标过程的理解和后仿整体进度的把握。

-

芯片

+关注

关注

457文章

51345浏览量

428291 -

仿真

+关注

关注

50文章

4134浏览量

134128 -

RTL

+关注

关注

1文章

385浏览量

60017 -

异步电路

+关注

关注

2文章

48浏览量

11155 -

时序约束

+关注

关注

1文章

115浏览量

13468

原文标题:后仿

文章出处:【微信号:芯司机,微信公众号:芯司机】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

我后仿出现了10种警告。。。求助

Cadence 16.5 Concept HDL原理图反标后每个元件出现CDS_PART_NAME信息

Cadence 16.5 Concept HDL原理图打包反标后电源、地网络显示为红色

运行后实现时序仿真后重新生成sdf文件

金橙子打标卡labview打标开发没头绪?c#封装成dll后labview调用真香!

如何将PT产生的SDF文件反标设计进行后仿真?

Python在IC中的应用——文本处理

解析SDF的Header Section信息与Cell Entries信息

详解芯片SDF文件 MCU芯片全流程设计

芯片后仿之SDF 3.0解析

芯片后仿真要点

芯片后仿及SDF反标

芯片后仿及SDF反标

评论