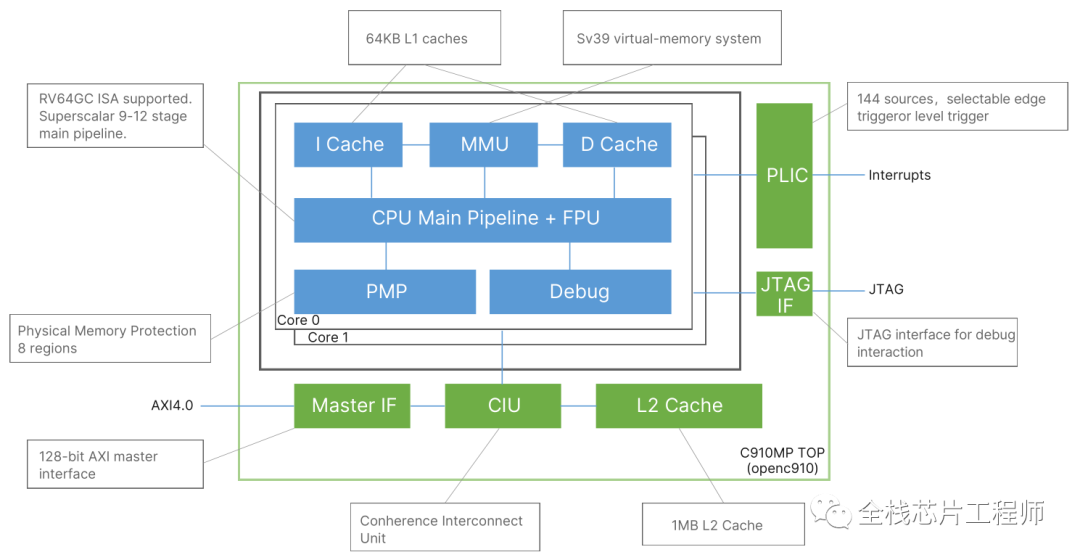

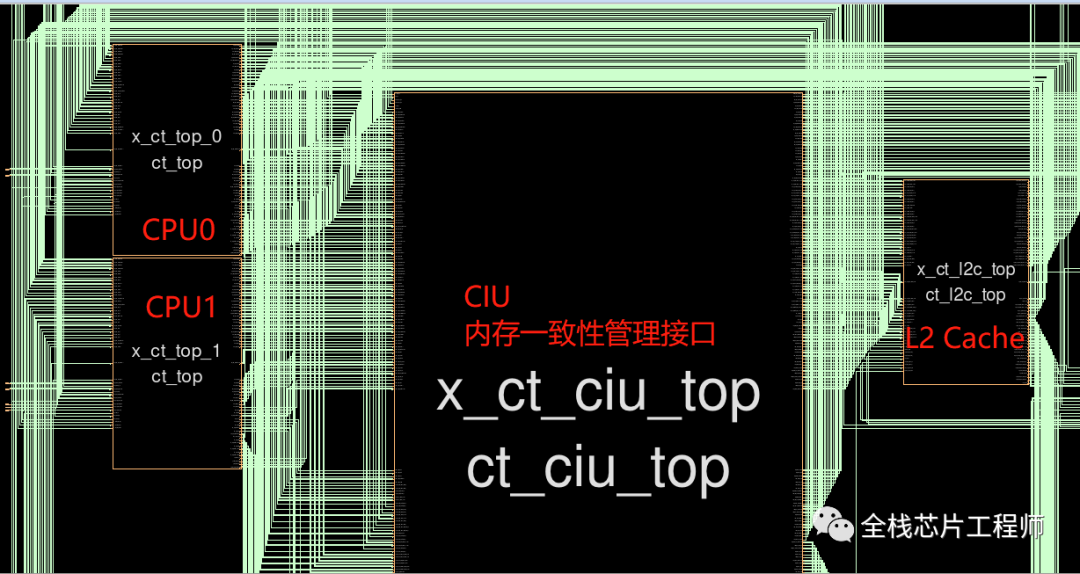

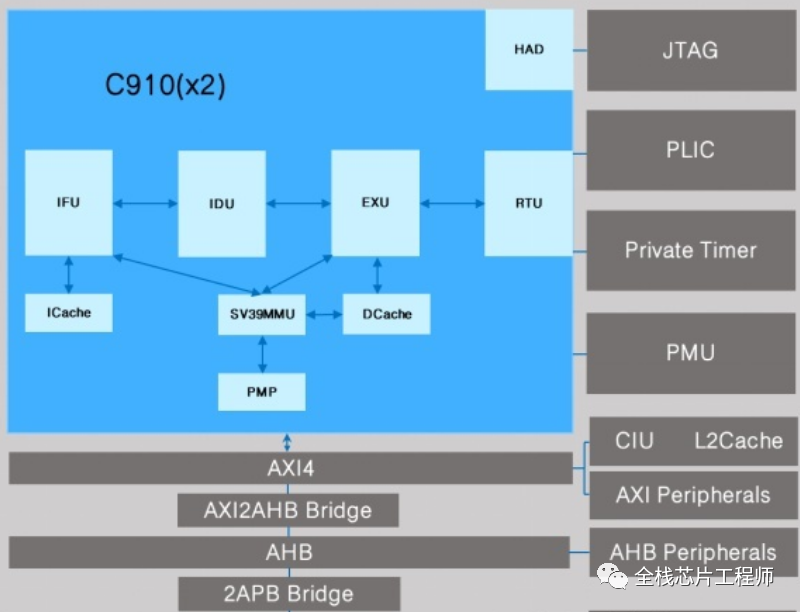

玄铁C910处理器是同构多核架构,支持双核;(开源版本为双核,预留四核接口),主要特征有:

• 支持各个核心独立下电以及cluster下电;

• 支持1 个AXI4.0 Master 接口,128比特的总线宽度;

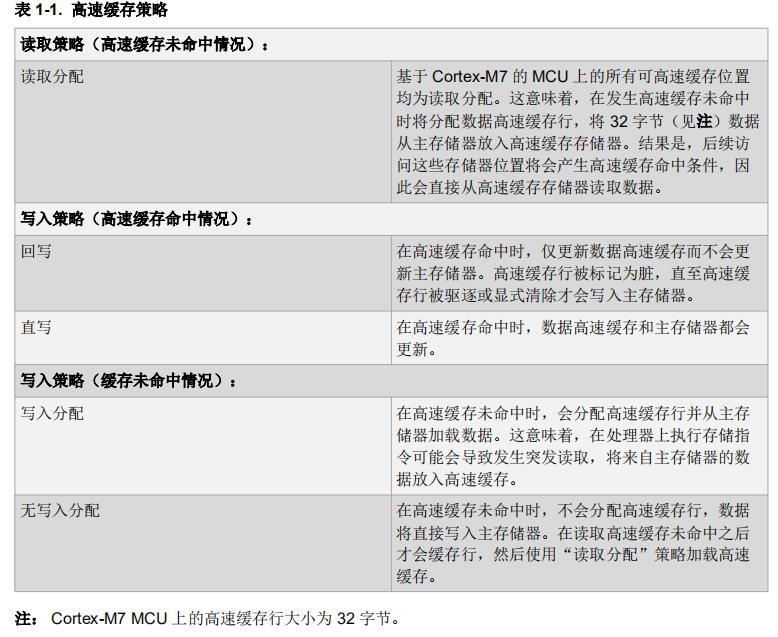

• 两级cache结构,哈佛结构L1cache(Icache、Dcache)和共享的L2cache;

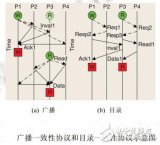

• L1cache支持MESI 的一致性协议,L2cache支持MOESI 的一致性协议;

• 支持RISC-V私有中断控制器CLINT 和平台级中断控制器PLIC;

• 支持自定义且接口兼容RISC-V 的多核调试框架;

C910MP 二级高速缓存采用 MOESI 协议维护多个处理器核心数据高速缓存的一致性。MOESI 代表了每个缓存行在数据高速缓存上的 5 个状态,分别是:

• M:表示缓存行仅位于此数据高速缓存中,且被写脏;(UniqueDirty)

• O:表示缓存行可能位于多个数据高速缓存中,且被写脏;(ShareDirty)

• E:表示缓存行仅位于此数据高速缓存中,且是干净的;(UniqueClean)

• S:表示缓存行可能位于多个数据高速缓存中,且是干净的;(ShareClean)

• I:表示缓存行不在该数据高速缓存中。(Invalid)

那么MESI是什么原理?硬件如何维护多核CPU的数据一致性?答案参见知识星球讨论。

-

处理器

+关注

关注

68文章

19480浏览量

231479 -

控制器

+关注

关注

113文章

16505浏览量

179916 -

cpu

+关注

关注

68文章

10928浏览量

213407 -

接口

+关注

关注

33文章

8745浏览量

152166 -

soc

+关注

关注

38文章

4222浏览量

219399

原文标题:多核CPU的SoC缓存一致性设计概述

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何解决数据库与缓存一致性

顺序一致性和TSO一致性分别是什么?SC和TSO到底哪个好?

一致性规划研究

加速器一致性接口

Cache一致性协议优化研究

自主驾驶系统将使用缓存一致性互连IP和非一致性互连IP

搞定缓存一致性验证,多核SoC设计就成功了一半

本周五|搞定缓存一致性验证,多核SoC设计就成功了一半

Redis缓存与Mysql如何保证一致性?

多核CPU的SoC缓存一致性设计概述

多核CPU的SoC缓存一致性设计概述

评论