目录/contents

● 速度-面积互换原则概述

● 设计思想1:乒乓操作

● 设计思想2:串/并转换

● 设计思想3:流水线设计

● 设计思想4:逻辑复制与模块复用

01速度-面积互换原则概述

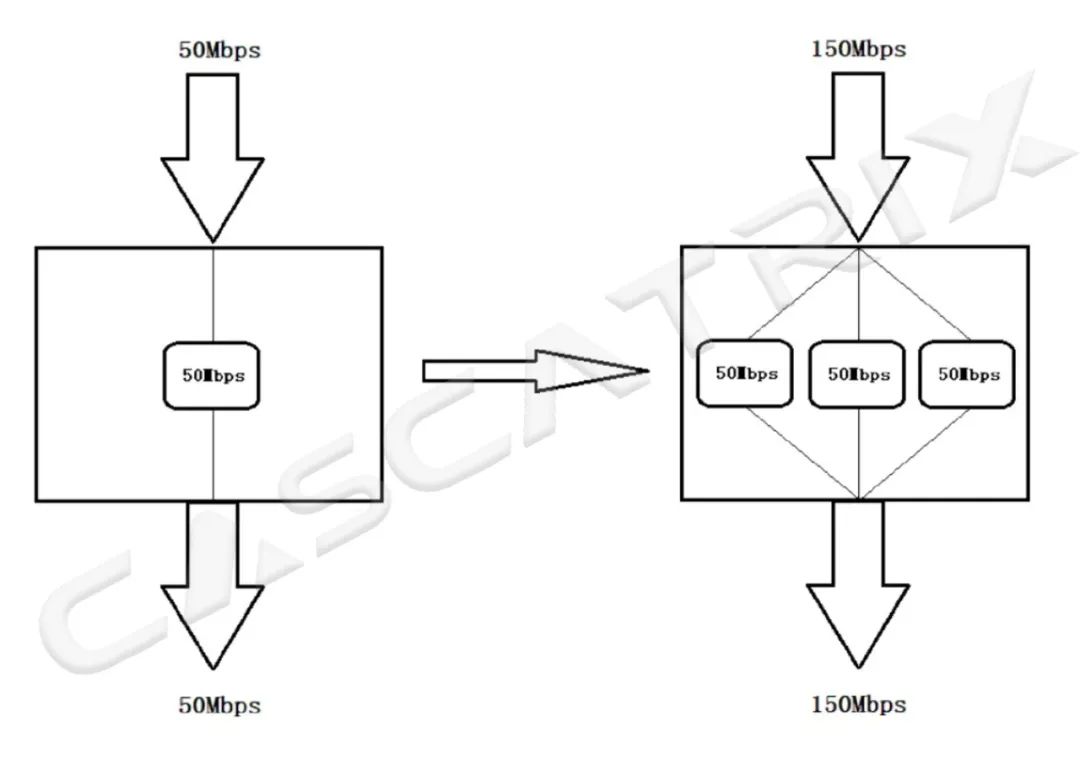

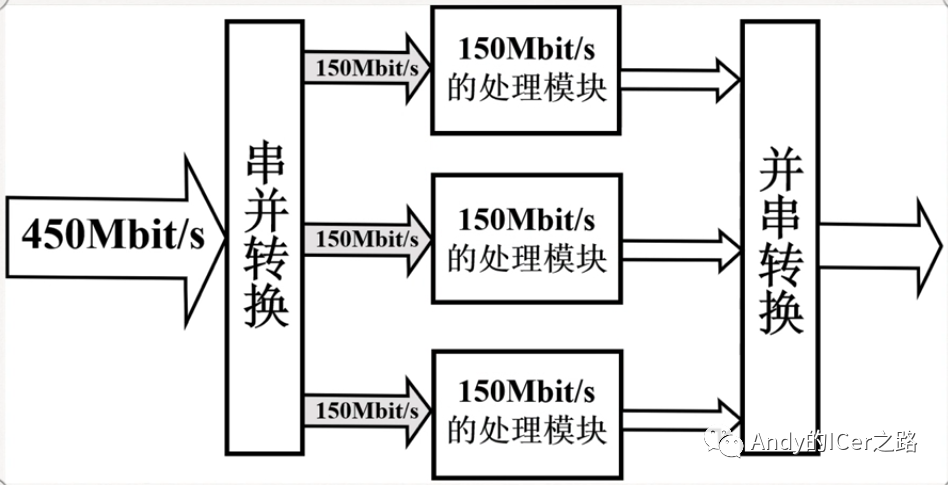

速度-面积互换原则是贯穿FPGA设计的重要原则:速度是指工程稳定运行所能达到的最高时钟频率,通常决定了FPGA内部寄存器的运行时序;面积是指工程运行所消耗的资源数量,通常包括触发器(Flip-Flop)和查找表(Look Up Table)等资源。在FPGA设计过程中,速度的提高通常以面积扩增为代价,面积的缩减通常以速度的降低为代价。如何权衡二者的性能要求,在满足时序(速度)要求的前提下尽可能节约逻辑资源(面积),是FPGA设计过程中需要考虑的重点。

例如,工程中占用一定的逻辑资源可以实现50Mbps的数据吞吐量,采用三倍的资源实现相应的功能,通过并行处理则可以实现150Mbps的数据吞吐量,从而实现用面积换速度的操作。

速度-面积互换原则的常用设计思想包括:乒乓操作、串/并转换、流水线设计、逻辑复制与模块复用。

02设计思想1:乒乓操作

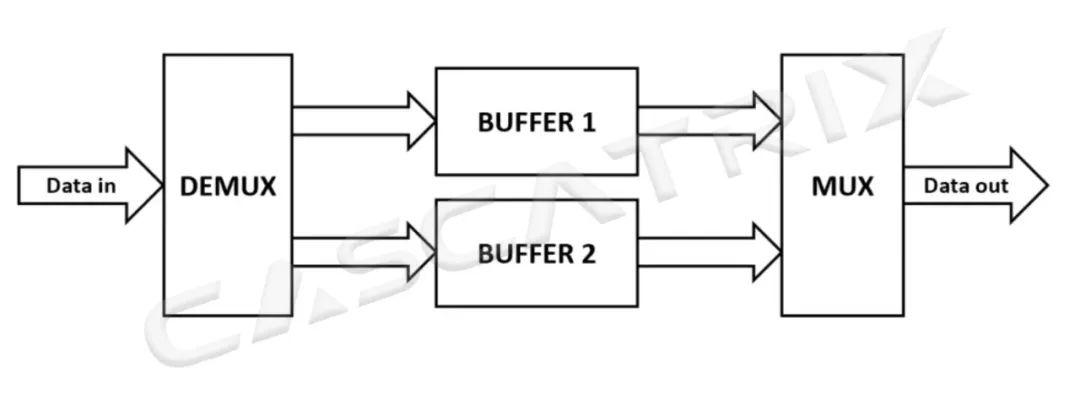

乒乓操作是一种常用的牺牲面积换取速度设计思想,常用于图像数据传输等数据量较大且实时性要求较高的场景。乒乓操作的具体流程为:分配输入数据进入多路缓存,常用缓存模块包括RAM、FIFO等,随后依次从多路缓存中输出数据,从而保证数据高速传输的连续性。

以上述图中所示模块为例:在第一个周期,输入数据流Data in通过DEMUX分配缓存在BUFFER1模块中;在第二个周期,输入数据流Data in通过DEMUX分配缓存在BUFFER2模块中,同时,MUX将BUFFER1模块中的缓存数据输出到后续处理模块;在第三个周期,输入数据流Data in再次通过DEMUX分配缓存在BUFFER1模块中,同时,MUX将BUFFER2模块中的缓存数据输出到后续处理模块...如此反复循环切换,通过乒乓操作完成数据的缓冲与传输,保证数据流无停顿地持续传输。

乒乓操作经常应用于外部接口传输以图像数据为代表的按帧划分的数据。在图像数据传输过程中,当前帧存入缓存BUFFER1的同时,显示器用于显示BUFFER2的图像数据帧;下一帧存入BUFFER2的同时,显示器用于显示BUFFER1的图像数据帧。乒乓操作保证显示器瞬间完成图像的切换,提高图像数据传输的效率和稳定性,特别是在通信环境较差的情况下。

03设计思想2:串/并转换

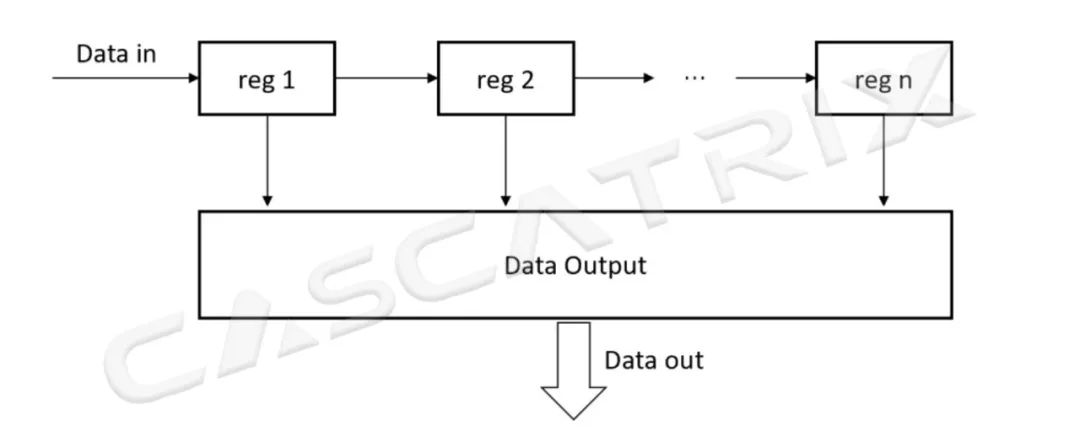

串/并转换是体现速度-面积互换思想的另一种设计方案,在高速数据流处理中发挥重要的作用。串/并转换通常将数据分成多个较小的数据块,这些数据块可以同时并行传输,从而提高数据的传输速率。

串/并转换的实现方法多种多样,根据数据数量的不同,可以选用寄存器、RAM、FIFO等实现。对于数量较小的设计通常可以采用移位寄存器实现。

以上述图中所示模块为例:串行输入数据data in通过n个移位寄存器后,通过位宽为n的并行总线输出数据data out。移位过程通常依赖于时钟进行同步,因此,完成一个周期的n位串/并转换需要消耗n个串行时钟周期。例如,串行传输时钟频率为100MHz,若将串行数据转为4bit并行数据输出,并行传输的时钟频率将降低至25MHz,这是串入并出的基本设计思想。

串/并转换通过牺牲面积换取数据带宽,提高数据传输的吞吐量,从一定程度上提高了数据的传输速率,同样体现出速度-面积互换思想。

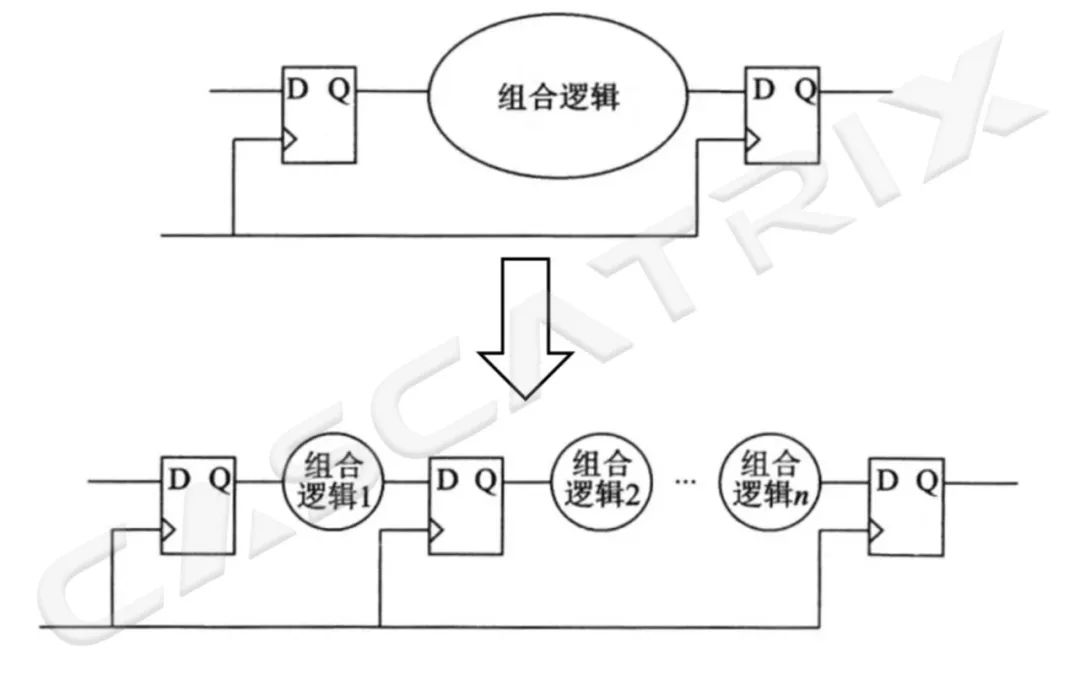

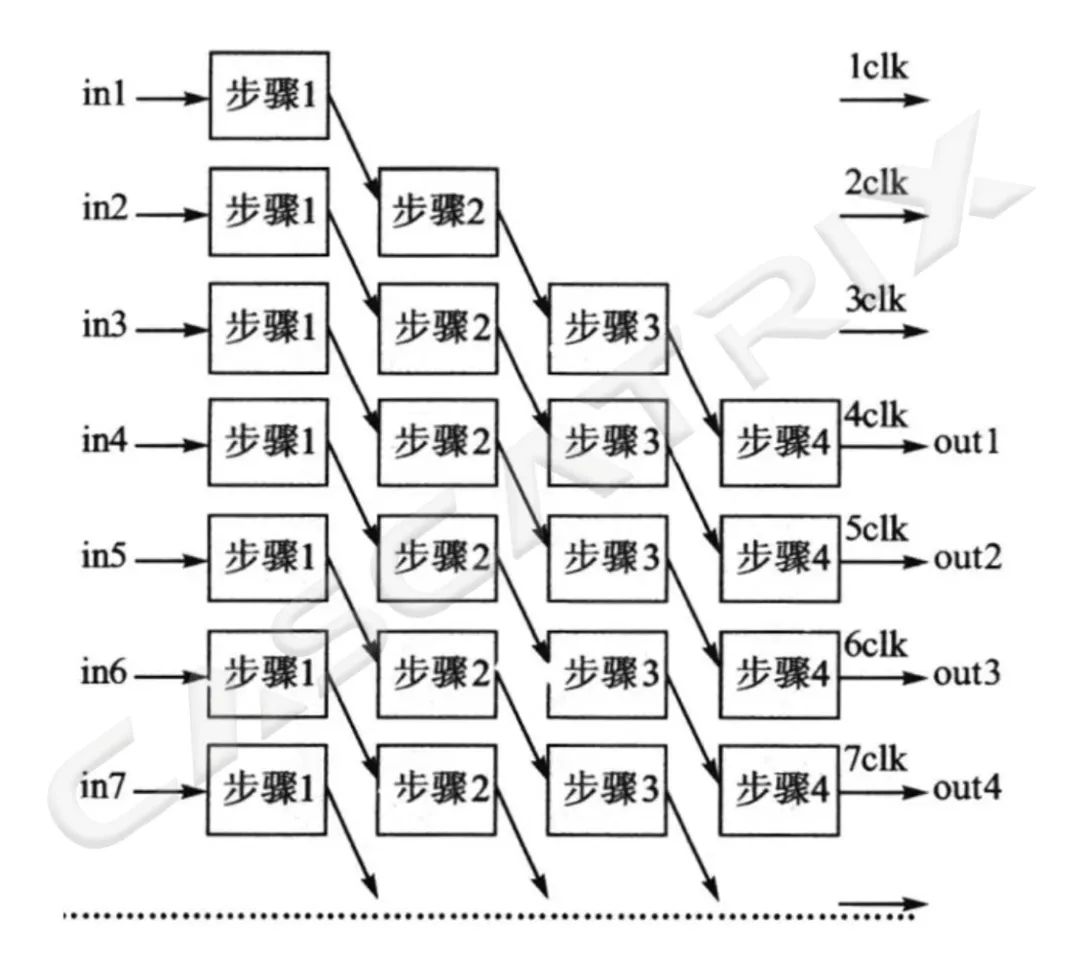

04设计思想3:流水线设计

流水线设计通过处理模块复制的方法提高数据流的处理速度,在高速信号处理领域发挥着重要作用。流水线设计主要应用于单向数据处理过程,即前一个模块的输出可以直接作为下一个模块的输入,运算处理不涉及反馈和迭代,那么可以考虑采用流水线设计方法提高系统的工作频率。

以上述图中所示模块为例,当原设计在一个时钟周期内实现一个较大的组合逻辑时,通过切割可以将较大的组合逻辑分解为多个较小的组合逻辑,分割后的组合逻辑需要在多个时钟周期内完成。尽管分割后的设计需要更多的时钟周期,但是这部分逻辑运行的时钟周期会有明显的提升,系统时钟频率提升后的耗时总体上优于提升前的单周期耗时,同时保证系统时序更加稳定可靠,尤其在当前组合逻辑所涉及的路径是一条关键路径时,采用流水线设计后,整个系统的性能将得到极大提升。

例如,当一个流水线设计需要四个时钟周期时,输入数据in1从第一个时钟周期1clk开始,直到第四个时钟周期4clk才处理完,但是在前四个周期处理完成后,每个时钟周期内都会有处理完成的数据输出。由此可见,流水线设计仅在开始时需要一定的处理时间,之后将不间断地输出数据,从而极大提高处理速度。如果不采用流水线设计对四周期处理过程进行分割,那么每个输入数据的处理都将需要四个时钟周期,而在耗费更多时钟周期的同时,系统的时钟频率也受到极大限制,甚至出现时序紊乱的情况。

流水线设计牺牲面积换取时钟频率,从而提高数据的传输速率,这种设计思想在高速通信、高速信号采集、图像处理等领域得到广泛应用。

05设计思想4:逻辑复制与模块复用

逻辑复制通过牺牲面积改善时序条件,从而降低信号的路径延时,常应用于信号扇出(fan out)的调整。如果某个信号的扇出很大,即需要驱动的后记逻辑信号较多,为增强这个信号的驱动能力,通常需要加入多级Buffer,这在一定程度上增加了信号的路径演示。此时可以复制生成这个信号的逻辑,用多路同频同相的信号驱动后续电路,降低平均到每路的扇出,从而在满足驱动能力的同时,避免多级Buffer造成的路径延时。

模块复用通过牺牲速率换取更低的资源占用面积,是逻辑复制的逆过程,可以极大降低硬件资源消耗。

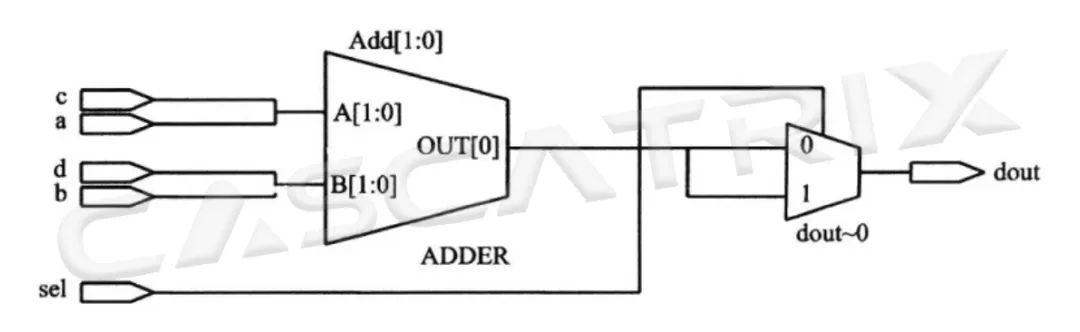

下面通过两段代码设计阐释上述概念:

Ex1:

input a,b,c,d;

input sel;

output dout;

assign dout = sel ? (a+b) : (c+d);

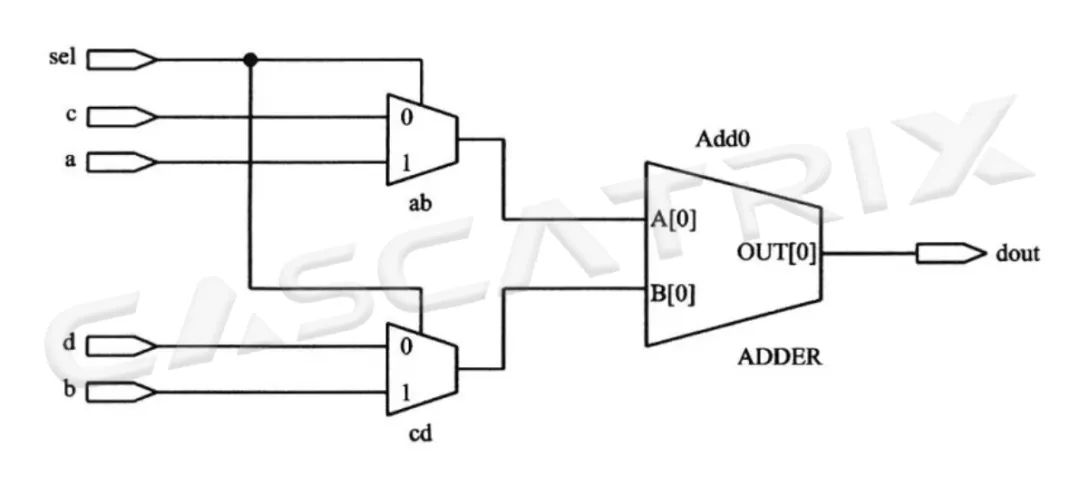

Ex2:

input a,b,c,d;

input sel;

output dout;

wire ac;

wire bd;

assign ac = sel ? a : c;

assign bd = sel ? b : d;

assign dout = ac + bd;

上述两端代码实现功能相同:Ex1综合出的RTL视图使用了两个2选1数据选择器和一个加法器;Ex2综合出的RTL视图使用了两个加法器和一个2选1数据选择器。Ex1占用更多的资源,但是处理速率更快;Ex2占用资源较少,但是处理速率较慢。

从一方面看,Ex1相对于Ex2是一种逻辑复制的过程,由于这个设计通过一个加法器就可以实现,但是为了提高处理速度,所以对加法器进行逻辑复制;从另一方面看,Ex2相对于Ex1是一种模块复用的过程,通过复用加法器逻辑模块,降低资源的消耗。

值得一提的是,当前很多综合工具都可以自动设置最大扇出值。如果某个信号的扇出值大于最大扇出值,那么该信号将会自动被综合工具复制。

审核编辑:汤梓红

-

FPGA

+关注

关注

1630文章

21796浏览量

605644 -

FPGA设计

+关注

关注

9文章

428浏览量

26601 -

寄存器

+关注

关注

31文章

5363浏览量

121053 -

流水线

+关注

关注

0文章

121浏览量

25944 -

RTL

+关注

关注

1文章

385浏览量

59931

原文标题:FPGA速度-面积互换原则设计

文章出处:【微信号:Carlinx FPGA,微信公众号:Carlinx FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA速度-面积互换原则设计

FPGA速度-面积互换原则设计

评论