本文转自TechSugar

感谢TechSuger对新思科技的关注

当前,我们正处于一个数据大爆炸的时代。IDC数据显示,全球数据量自2022至2026五年时间里将增长一倍以上,仅中国的数据量就将达到56.16ZB,年复合增长率为24.9%。

高速增长的数据量让我们从“计算驱动”走向“数据驱动”,数据正成为社会经济发展重要的生产要素,也引发出三个关键性问题——开放流通、价值挖掘和安全保护。

我们都知道芯片是数据流转的核心载体,数据的计算、传输和存储都离不开芯片。近几年,“芯片后门”事件时有发生,造成的经济损失也越来越大,因此安全已经成为芯片设计架构中不可或缺的一环。

大数据时代,芯片的地位就像电气时代的电能一样。如果将终端产品的外包装去除,芯片便随处可见,从人们生活中使用的手机、PC,到出行时乘坐的汽车、高铁,再到生产制造中的工控、机器人等皆是如此。之所以会这样,就是因为芯片是各行各业实现数字化和智能化的物理载体。因此,每一个行业都在强调芯片安全。

我们看两个具有代表性的行业。首先是数据中心领域,这个领域的安全强度往往取决于下层硬件系统的强度,因为底层漏洞能够从内部瓦解软件的防御体系,让黑客和不法分子获得整个系统的访问特权。因此,我们看到芯片的可信根是数据中心安全架构师开始构建安全防护体系的源头。

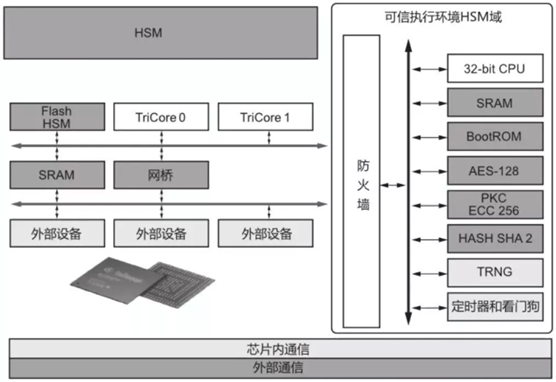

另一个具有代表性的领域是汽车,由于汽车功能的特殊性,可以说汽车对于芯片安全体系的构建是当前各行业的表率。就以EVITA HSM规范来说,它是SHE(Secure Hardware Extension,安全硬件扩展)规范的扩展,用数字密钥的方式构建整个汽车芯片硬件安全体系。如下图所示,这是英飞凌公司展示的一种典型HSM逻辑架构,该架构的左侧是密码协处理器HSM,通过安全模块与执行内核TriCore和芯片外部通信;还提供一个HSM域,作为一个内部的可信执行环境。

图1:典型HSM逻辑架构 (图源:英飞凌)

很明显,安全已经成为芯片架构的一部分。除了数据中心和智能汽车,智能手机和PC等领域的芯片基本都拥有一套完整的芯片安全体系。这是芯片产业发展的一个重大改变。在过去很长一段时间里,安全体系和芯片架构是脱节的,安全问题需要通过补丁解决,解决不了的则在下一代设计中添加。

随着数据价值提升,这种安全和架构分离的方式显然不能够适应这个时代,芯片需要从设计之初就确保足够安全。

从行业发展的情况来看,推动芯片安全的要素有两个:黑客攻击和法律法规。数据价值量的提升让黑客的攻击不再局限于软件层面,使用更安全的芯片就意味着拥有更完整的安全防御体系;法律法规层面,像欧洲《通用数据保护条例》(GDPR)这样的法案已经非常多,不胜枚举。

安全和防御是一个动态的博弈,因此实际上不存在绝对安全的芯片,不过通过更好的芯片架构设计,我们便能够在芯片安全防护战中占得先机。那么,该如何去部署更安全的芯片架构呢?

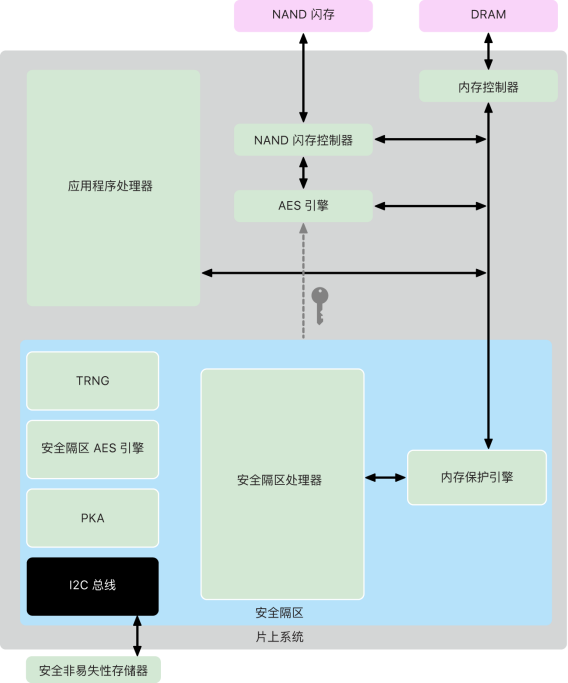

相信很多人从英飞凌典型HSM逻辑架构中已经看出端倪——接口IP对打造安全芯片至关重要。为了加强这一概念,我们再举一个实例,下图是苹果公司的Secure Enclave方案框图,能够看到该方案增强芯片安全的节点都是在传输环节,包括处理器和DRAM内存的连接,处理器和NAND闪存的连接,以及芯片上的I2C接口等。

图2:苹果Secure Enclave安全方案 (图源:苹果公司)

从主流芯片厂商的方案中能够看出,对于芯片设计而言,往往接口安全了,芯片也就安全了。这便是我们要传达给大家的理念。

为什么要这样讲呢?事实上,芯片的安全主要有两个维度:第一个是基于芯片的安全服务,也可以理解为芯片能够向外提供的安全服务,包括密码算法、密钥管理、PUF等;第二个是芯片自身需要的安全防护能力,要能够抵抗外来的物理攻击,检测和防御故障注入攻击等。

不难发现,芯片安全这两大维度都是围绕着芯片接口展开的,向外提供安全服务需要通过接口,外界对芯片的攻击实际上也是通过芯片接口。

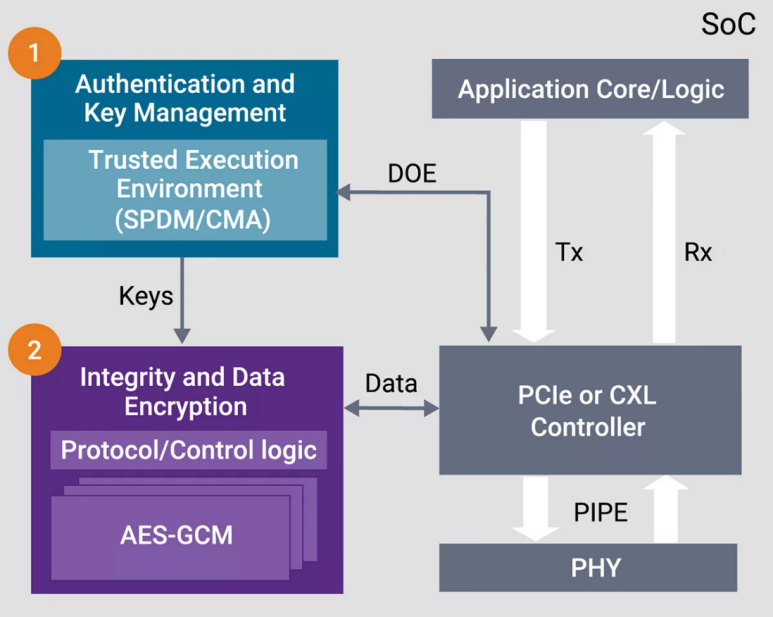

意识到这一点之后,芯片领域的接口标准很快就做出了积极的回应。我们还是以数据中心这个领域为例,为了提升数据传输的安全保障,PCI-SIG和CXL标准组织在2020年末将完整性和数据加密等安全要求添加到PCIe 5.0和CXL 2.0规范中,增加了下图中“1”点标注的认证和密钥管理,和“2”点标注的完整性和数据加密 (IDE)。

图3:PCIe 5.0和 CXL 2.0规范中的安全措施

“认证和密钥管理”包括认证、鉴权、测量、识别和密钥交换等功能,它让所有功能都在可信的执行环境安全模块中运行;“完整性和数据加密”是为PCIe的事务层数据包(TLP)和CXL的流量控制单元(FLIT)提供保密性、完整性和重放保护,它确保线路上的数据不会被观察、篡改、删除、插入和重放。

根据规范详情,PCIe6.0中继续保留了工程变更通知(ECN)与完整性和数据加密这些安全功能,满足TEE设备接口安全协议(TDISP),保护虚拟主机和设备的互联。

不过,虽然知道接口IP在芯片安全中的重要性,但是在实际芯片设计过程中依然会面临其他方面的挑战。

首先,如果是自研接口IP,除了接口IP研发本身就具有很高的技术壁垒之外,如何保证接口IP安全也是一个很大的挑战。综合而言,目前产业界大概有数十种保障接口IP安全的方案,包括加密传输、API Key验证、请求限制、防止SQL注入、完整性和数据加密等,采用哪些安全方案进行融合,如何实现这些安全方案都是让开发者“头疼”的事情。

其次,如果是采用第三方的接口IP。Riscure的高级安全分析师Nicole Fern曾表示,如果接口IP供应商没有技术实力和优势,那么其产品的透明度会很差,你可能需要先阅读“500页”的产品说明书才能够知晓这款接口IP的使用限制范围,一旦有所疏忽,所谓的安全将会是形同虚设。

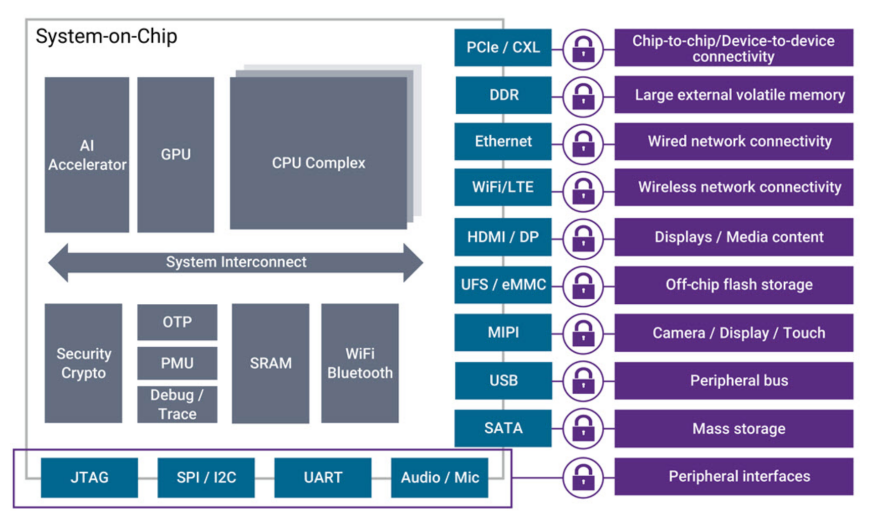

另外,如下图所示,随着芯片集成度的提高,接口IP的复杂度也在提升,包括DDR、PCIe、CXL、以太网、MIPI、USB、UFS、eMMC、HDMI和DisplayPort等,开发者不仅需要确认每一个接口IP的标准、规范和安全性,还需要确保整个系统是受到保护的。优秀接口IP供应商此时的优势便凸显出来了——既安全,又透明,且易用。

图4:SoC上需要确保安全性的接口非常多

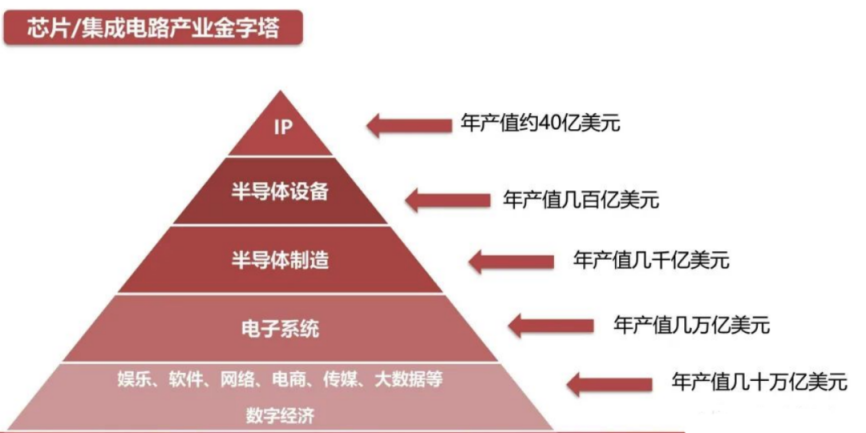

一直以来,IP在芯片产业都有着崇高的地位,和EDA工具并称为“芯片产业上的皇冠”。根据IPnest提供的数据,在IP产业里,接口IP近几年受益于数据中心、5G和智能汽车领域的高速发展,增速达到IP产业平均增速的两倍。

图5:芯片产业金字塔 (图源:方正证券)

不过,正如上文提到的,高速发展的接口IP不仅要满足更高的数据传输要求,同时也要提供透明、可靠的安全保障,赋能大数据时代更好地发展。

作为全球排名第一的芯片接口IP供应商,同时也是信息安全和软件质量的全球领导者,新思科技为芯片产业提供广泛的安全接口IP产品,实现最高级别的SoC安全性,以保护HPC、IoT、移动和汽车SoC免受篡改和物理攻击。

安全PCIe 6.0/5.0接口和CXL 3.0/2.0接口

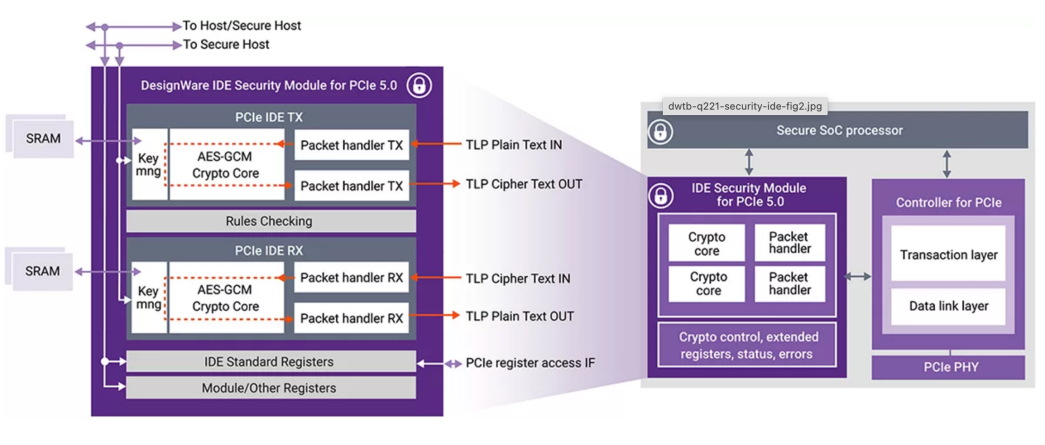

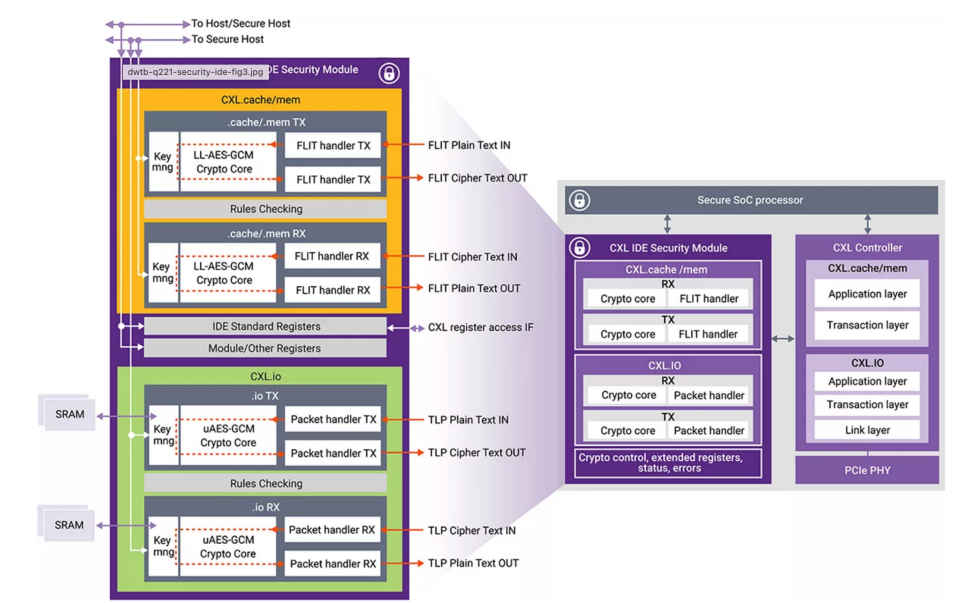

早在2021年2月,新思科技就推出了DesignWare IDE安全模块——业界首个符合PCIe5.0和CXL2.0规范的完整性和数据加密安全IP核模块,帮助开发者更好地利用PCIe5.0架构或CXL2.0接口进行HPC SoC设计。

图6:用于PCIe5.0的DesignWare IDE安全模块框图

图7:用于CXL2.0的DesignWare IDE安全模块框图

综合而言,DesignWare IDE方案有以下几个优势:

-

接收和发送方向的全双工最大化吞吐量;

-

基于256位密钥大小的AES-GCM加密算法,为PCIe TLP和CXL FLIT提供高效的加密、解密和认证;

-

密码和哈希算法的宽度可配置以满足方案的面积和延迟优化;

-

高效的动态密钥刷新,实现系统中密钥的无缝更改;

-

针对无保护流量的低延迟顺序旁路模式。

目前,新思科技的IDE安全模块已经能够适用于最新的PCIe6.0和CXL3.0规范,让开发者在开发满足最新标准的高性能计算芯片时,同样做到性能和安全性兼顾,且在上市时间上取得领先。

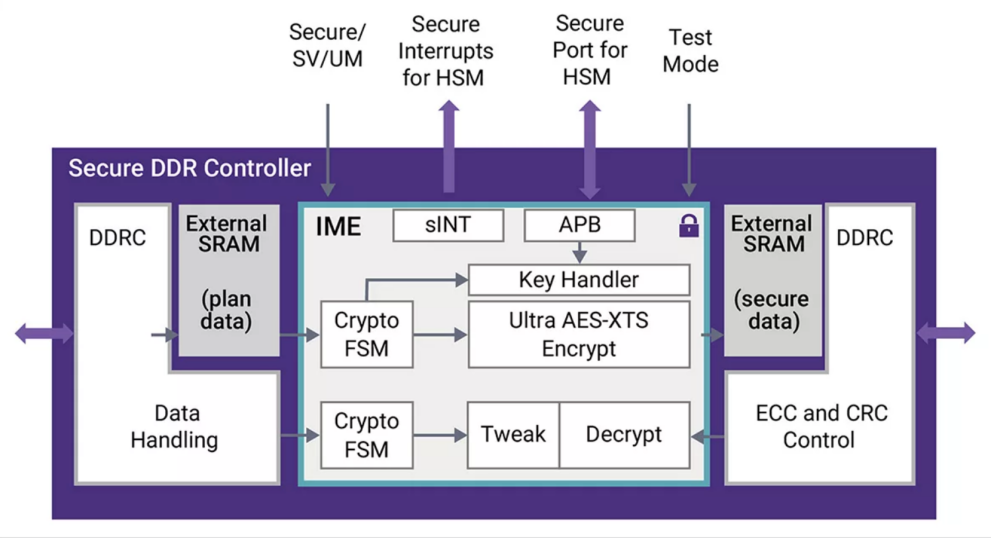

具有内嵌存储加密(IME)功能的安全DDR控制器

在现有的计算架构中,计算和存储是最核心的两大单元。内存和存储安全旨在保护存储资源和存储在其中的数据,那么DDR、LPDDR、GDDR 和HBM内存接口上的数据安全就显得非常重要。

下面这款方案是新思科技推出的具有集成IME安全功能的安全DDR/LPDDR控制器。方案优势包括:

-

高性能、低延迟的安全内存接口,可高效地支持各种数据流量;

-

读写通道独立保护;

-

基于符合标准的AES-XTS加密算法的加密/解密;

-

支持256位和512位AES-XTS密钥大小;

-

超低延迟(低至2个周期);

-

每个区域加密/解密;

-

每个周期一次tweak预计算;

-

高效的密钥设置和刷新;

-

密钥读回保护/归零;

-

支持FIPS 140-3认证;

-

旁路模式。

图8:具有集成IME安全功能的安全DDR/LPDDR控制器

如图8所示,这是一种内嵌式的存储安全接口,与相关的DDR控制器紧密集成,靠近PHY接口,在DRAM突发模式下工作,这是实现高效、低延迟安全性能的关键。

适合各种应用最广泛协议的安全接口

除了安全PCIe6.0/5.0接口和CXL3.0/2.0接口,具有内嵌存储加密(IME)的安全DDR/LPDDR接口以外,新思科技丰富的安全接口IP方案还包括:

-

具有媒体访问控制安全性(MACsec)的安全以太网接口;

-

具有高清内容保护(HDCP v2.3)的安全HDMI和DisplayPort接口;

-

具有加密和身份验证的安全USB接口;

-

具有Die-to-Die接口加密的安全Multi-Die系统;

-

具有端到端安全传输的安全MIPI接口;

-

具有内嵌加密和高级重放保护内存块(RPMB)的安全UFS和eMMC接口。

也就是说,围绕高性能SoC的安全接口设计,你都能在新思科技找到对应的解决方案。这些方案不仅让你的芯片能够满足最新的行业规范,同时也具备行业领先的安全性。并且,这些IP都是易于集成的,正如Arbe硬件工程副总裁Avi Bauer所言,“新思科技的安全IP让我们能够在硅面积预算内达到安全标准和性能水平。”

数据大爆炸的时代,信息的价值也随之飞升,因此带来的数据安全挑战是极大的。芯片作为大数据的物理载体,其安全的重要性已经不言而喻,关系到国计民生的方方面面。

在打造安全芯片的过程中,把好接口IP的安全关,芯片也就安全了。新思科技作为全球顶尖的IP方案商,在接口IP方面,拥有深厚的技术积累和领先的行业理解,能够提供安全、透明、易用的接口IP产品,携手IC设计公司共同打造更安全的SoC产品。

-

新思科技

+关注

关注

5文章

790浏览量

50323

原文标题:芯片接口IP:数字世界的第一层“屏障”

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

OSI七层模型的每一层功能

OSI七层模型详解 OSI七层模型与TCP/IP模型比较

ESP8266是否能实现金字塔式的Wifi级联?

卷积神经网络每一层的作用

求助,关于AN2867的晶振布局问题求解

stm32f030从return跳出会死在void HardFault_Handler(void)的原因?怎么解决?

CNN如何解决边缘检测问题

芯片接口IP:数字世界的第一层“屏障”

芯片接口IP:数字世界的第一层“屏障”

评论