有关加法器的知识,加法器是用来做什么的,故名思义,加法器是为了实现加法的,它是一种产生数的和的装置,那么加法器的工作原理是什么,为什么要采用加法器,下面具体来看下。

一、加法器的原理

加法器是为了实现加法的,即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。如果加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

对于1位的二进制加法,有五个的相关量:1,被加数A,2,被加数B,3,前一位的进位CIN,4,此位二数相加的和S,5,此位二数相加产生的进位COUT。前三个量为输入量,后两个量为输出量,五个量均为1位。

对于32位的二进制加法,也有五个相关量:1,被加数A(32位),2,被加数B(32位),3,前一位的进位CIN(1位),4,此位二数相加的和S(32位),5,此位二数相加产生的进位COUT(1位)。

二、采用加法器的原因

如果需要实现32位的二进制加法,一种自然想法就是将1位的二进制加法重复32次(即逐位进位加法器),这么做无疑是可行且易行的,但由于每一位的CIN都是由前一位的COUT提供的,所以第2位必须在第1位计算出结果后,才能开始计算;第3位必须在第2位计算出结果后,才能开始计算等。而最后的第32位必须在前31位全部计算出结果后,才能开始计算。这种方法使得实现32位的二进制加法所需的时间是实现1位的二进制加法的时间的32倍。

可见,上述方法是将32位的加法1位1位串行进行,需要缩短进行的时间,就要设法使上叙进行过程并行化。

逐位进位加法器,在每一位的计算时,都在等待前一位的进位。那么不妨预先考虑进位输入的所有可能,对于二进制加法来说,就是0与1两种可能,并提前计算出若干位针对这两种可能性的结果。等到前一位的进位来到时,可以通过一个双路开关选出输出结果。这就是进位选择加法器的思想。

提前计算多少位的数据为宜?

同为32位的情况:线形进位选择加法器,方法是分N级,每级计算32/N位;平方根进位选择加法器,考虑到使两个路径(1,提前计算出若干位针对这两种可能性的结果的路径,2,上一位的进位通过前面的结构的路径)的延时达到相等或是近似方法,或是2345666即第一级相加2位,第二级3位,第三级4位,第四级5位,第五级6位,第六级6位,第七级6位;或是345677即第一级相加3位,第二级4位,第三级5位,第四级6位,第五级7位,第六级7位。

-

加法器

+关注

关注

6文章

183浏览量

30110 -

半加器

+关注

关注

1文章

29浏览量

8790 -

二进制加法

+关注

关注

0文章

4浏览量

1745

发布评论请先 登录

相关推荐

十进制加法器,十进制加法器工作原理是什么?

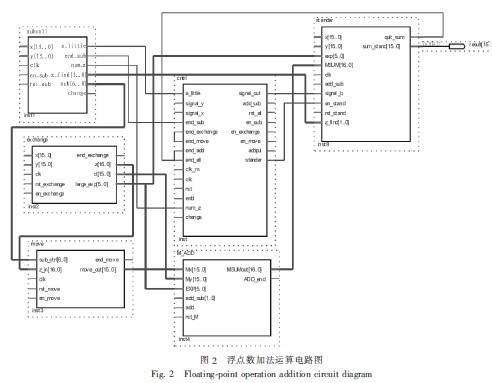

FPU加法器的设计与实现

同相加法器电路原理与同相加法器计算

加法器的原理及采用加法器的原因

加法器的原理及采用加法器的原因

评论