集成电路对其输入电源快速瞬变的响应通常是一项重要的测量。如果被测器件(DUT)是微功率器件,不需要输入旁路电容,只需使用50Ω端接函数发生器驱动电源输入即可。然而,随着电流要求和电容的增加,这不再提供可接受的结果。

将这种快速瞬态转换为大容性负载的一种解决方案是制作开环缓冲器。由于开环缓冲器没有反馈,因此对容性负载不敏感,可以设计为满足大多数电流要求。该缓冲器的重要标准包括高压摆率、高输出驱动、低失调电压、低失真和热补偿。

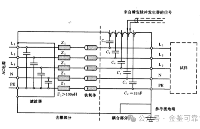

下图中的电路满足这些要求。它类似于经典的 BJT 缓冲区,但进行了一些修改。由于所使用的晶体管不在单个单片芯片上,因此必须提供一些方法来调整偏置。此外,电路必须有某种方法使该偏置在整个温度范围内保持恒定。

图1.开环缓冲器原理图。

该电路由三个主要模块组成。有一个高阻抗互补输入级,后跟一个V是用于偏置调整的乘法器,然后是互补的达林顿输出级。输入级和V是乘法器通过恒流源偏置,而输出级由V的输出偏置是乘。

将输入级连接到V的关键是乘法器和输出级通过电阻R7和R8包含一些串联电阻。这允许 V是乘法器用于控制输出级偏置,而不会对抗输入级的偏置电平。当输出级因负载要求而升温时,这成为一个因素。如果不包括串联电阻,输入级将在高温下使输出级过偏置。因为 V是乘法器安装在输出散热器上,它对输出级进行热跟踪,消除了热失控。

该电路设计用于高于最大输出约5V和低于最小输出约5V的双极性电源。工作在+15V和-5V可提供良好的性能。请注意,董事会中已包含多个理由。输入电源应使用一对短的粗规格导线连接到PCB。不要与任何其他电路共用这些接地。输出应使用非常短的粗规格导线连接到 DUT 输入。这些导线将承载超过10A的瞬态电流,应相应地调整尺寸。

缓冲器采用高输入阻抗设计,具有灵活的驱动要求。不要将缓冲器的输出连接到 DUT 的输入,而缓冲器输入端没有驱动信号。如果输出电压低于±5V,则在缓冲器输入端使用50Ω端接器。如果输出高达10V,则不端接运行脉冲发生器以获得此电压。超出此电压的电压将需要增加一个外部放大器。缓冲器的最大电源电压为 |V+ - V-|< 40V。

审核编辑:郭婷

-

电源

+关注

关注

184文章

17762浏览量

250683 -

集成电路

+关注

关注

5389文章

11570浏览量

362212 -

DUT

+关注

关注

0文章

189浏览量

12417

发布评论请先 登录

相关推荐

CDN输出端口电快速瞬变脉冲群波形的校准方法

RS485端口浪涌瞬变防护设计

EN61000-4-4 电快速瞬变脉冲群抗扰性试验

快速瞬变脉冲群发生器及电路

电快速瞬变脉冲群常见抑制方法

电快速瞬变脉冲群发生器的校准方法

产生快速线路瞬变

产生快速线路瞬变

评论