本文来自“深度报告:大算力时代下先进封装大有可为(2023)”,重点分析了摩尔定律经济效能达到瓶颈,先进封装提升芯片系统性能、封装技术发展趋势:芯片性能不断提高、系统趋于小型化、先进封装的技术与形态根据需求不断迭代,多应用于高性能场景。

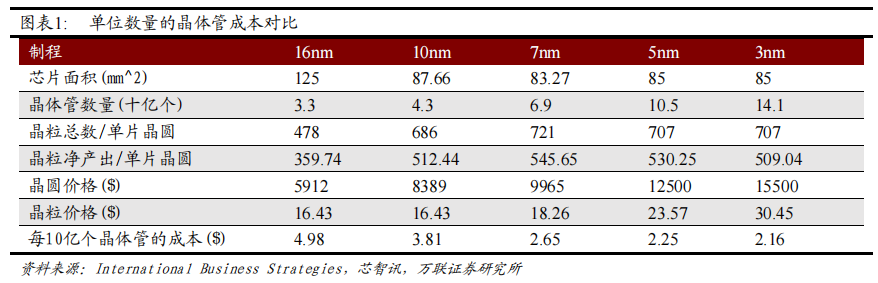

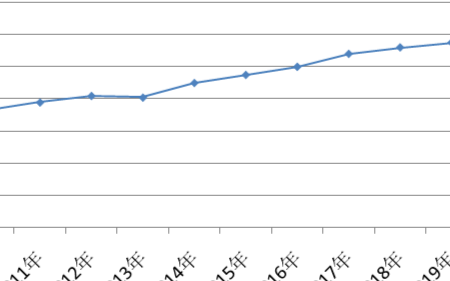

摩尔定律是指随着技术演进,芯片上容纳的晶体管数量会呈指数级增长,每1.5-2年翻一倍,同时带来芯片性能提升一倍或成本下降一半的效应。随着芯片制程工艺的不断发展,芯片上容纳的晶体管数量不断增加,但单位数量晶体管的成本下降幅度正在持续降低。根据IBS的统计及预测,从16nm到10nm,每10亿颗晶体管的成本降低了30.7%,从7nm到5nm成本下降了17.8%,而从5nm到3nm成本仅下降了4.2%。

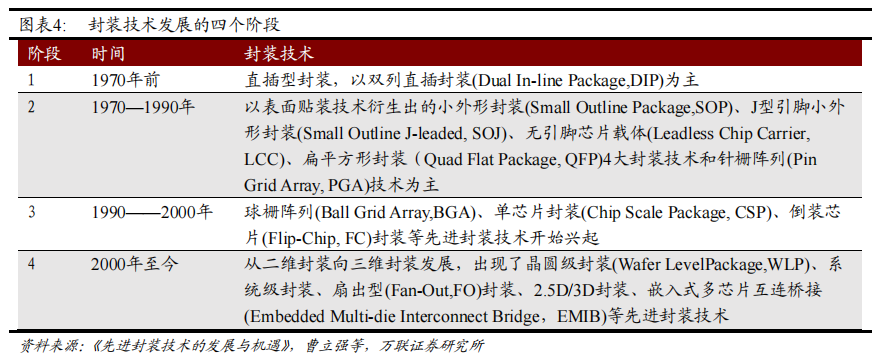

先进封装成为超越摩尔定律、提升系统性能的关键路径之一。目前集成电路发展主要沿着两个技术路线进行,一个是摩尔定律的延伸,即向芯片小型化的方向发展,通过微缩半导体器件的晶体管尺寸以增加可容纳的晶体管数量,以单个芯片性能的提升为目标;另一个是超越摩尔定律,即以先进封装技术的发展为主要方向,将处理、模拟等多种芯片集成在一个系统内,实现系统级封装(System in Package, SiP),以系统性能的提升为目标。 封装技术的发展史是芯片性能不断提高、系统不断小型化的历史。封装是半导体晶圆制造的后道工序之一,目的是支撑、保护芯片,使芯片与外界电路连接、增强导热性能等。封装技术的发展大致分为4个阶段:

第一、第二阶段(1990年以前)以DIP、SOP和LCC等技术为主,属于传统封装;第三阶段(1990至2000年)已经开始应用先进封装技术,这一阶段BGA、CSP和FC技术已开始大规模生产;第四阶段(2000年至今),先进封装技术从二维开始向三维拓展,出现了2.5D/3D封装、晶圆级封装、扇出型封装等封装技术。先进封装也称为高密度封装(HDAP,High Density Advanced Package),采用先进的设计和工艺对芯片进行封装级重构,并有效提升系统性能。相较于传统封装,先进封装具有引脚数量增加、芯片系统更小型化且系统集成度更高等特点。 先进封装技术的发展主要朝上游晶圆制程和下游模组两个方向。 1)向上游晶圆制程领域发展,该方向发展的技术即晶圆级封装,通过晶圆重构工艺在晶圆上完成重布线,并通过晶圆凸点工艺形成与外部互联的金属凸点以进行封装,该技术的特点是可以在更小的封装面积下容纳更多的引脚; 2)向下游模组领域拓展,即发展系统级封装技术,将以前分散贴装在PCB板上的多种功能芯片,包括处理器、存储器等功能芯片以及电容、电阻等元器件集成为一颗芯片,压缩模块体积、缩短电气连接距离,提升芯片系统整体功能性和灵活性。 先进封装的四要素是Bump、RDL、Wafer和TSV,具备四要素中任意一种技术即为先进封装。

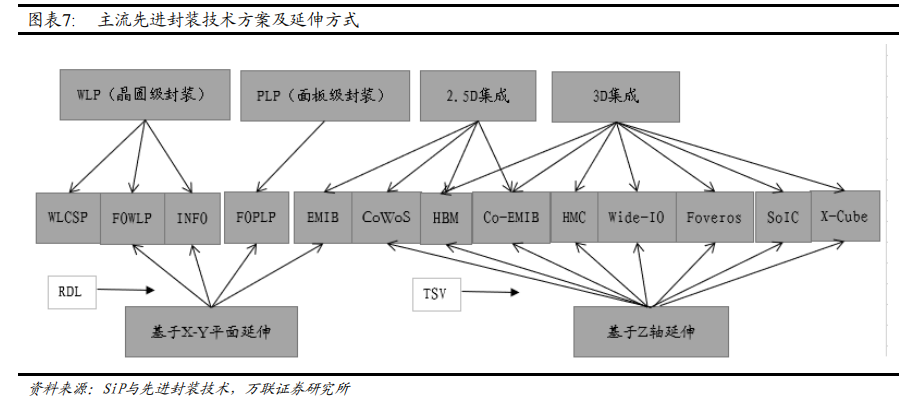

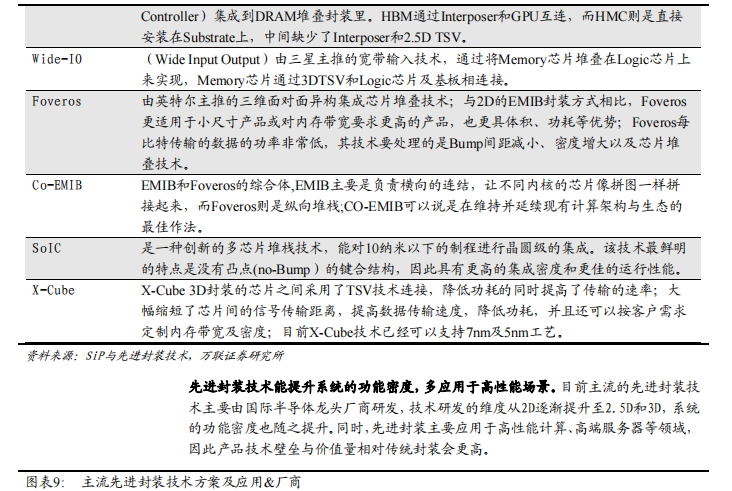

1)Bump(金属凸点)技术,普遍应用于Flip-Chip(倒装焊)技术中,处于晶圆之间互联的位置,起着电气互联和应力缓冲的作用,其发展趋势是使金属凸点越来越小,直至发展为Hybrid Bonding(混合键合)技术,该技术制造的电介质表面光滑、没有凸点,且具有更高的集成密度; 2)RDL(重布线层)技术,用于X与Y平面电气延伸和互联,适用于为I/O端口进行宽松排布,广泛应用于WLP(晶圆级封装)技术和2.5D/3D技术中,但不适用于Flip-Chip技术; 3)Wafer(晶圆)技术,可以用作芯片的基底和WLP封装的载体,也可以与硅基板一同实现2.5D集成,技术发展趋势是使Wafer面积逐渐增大; 4)TSV(硅通孔)技术,用于Z轴电气互联,是实现多维立体结构封装的关键技术。 RDL和TSV使封装技术在X-Y-Z三维空间中具备延伸和发展的可能性。重布线层(RDL)技术使得晶圆级封装得以在X-Y平面进行延伸,诞生了WLCSP、FOWLP、INFO、FOPLP、EMIB等技术。基于硅通孔(TSV)技术,封装系统沿着Z轴进行延伸,实现了二维向三维的拓展,出现了2.5D和3D集成,并演变出CoWoS、HBM、Co-EMIB、HMC、Wide-IO、Foveros、SoIC、X-Cube等技术。 先进封装的技术与形态会根据应用侧需求不断变化与迭代。从WLP、SiP、2.5D/3D等技术方案出发,各厂商根据应用侧需求进一步迭代出更深层的技术。以晶圆级封装(WLP)技术为例,起初WLP技术采用Fan-in形态,随着引脚数要求增加,Fan-out形态逐渐成为主流;而后出于提升系统性能的目标,台积电将多个芯片Fan-out工艺集成起来,诞生了INFO技术;而从节省成本的角度出发,单个芯片的FOWLP技术又进一步迭代出面板级封装技术(FOPLP)。

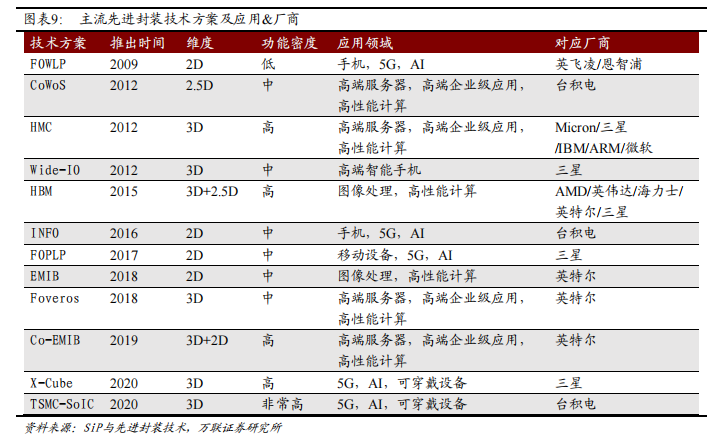

先进封装技术能提升系统的功能密度,多应用于高性能场景。目前主流的先进封装技术主要由国际半导体龙头厂商研发,技术研发的维度从2D逐渐提升至2.5D和3D,系统的功能密度也随之提升。同时,先进封装主要应用于高性能计算、高端服务器等领域,因此产品技术壁垒与价值量相对传统封装会更高。

系统级封装(SiP)属于广义的先进封装,侧重于系统属性。SiP是指在封装内形成一个系统,关注系统在封装内的实现,所以系统是其重点关注的对象,与之对应的是CSP(单芯片封装)。但SiP并不是先进封装特定的某种技术方案,因为SiP可能采用传统的Wire Bonding工艺,也可能采用先进封装的Flip Chip工艺。但随着系统对性能、功耗、体积的要求越来越高,集成密度的需求也越来越高,SiP也会越来越多地采用先进封装工艺。在下方示意图中,SiP指代的是封装整体,Chiplet/Chip是封装中的单元,先进封装是由Chiplet/Chip组成的,2.5D和3D是先进封装的工艺手段。

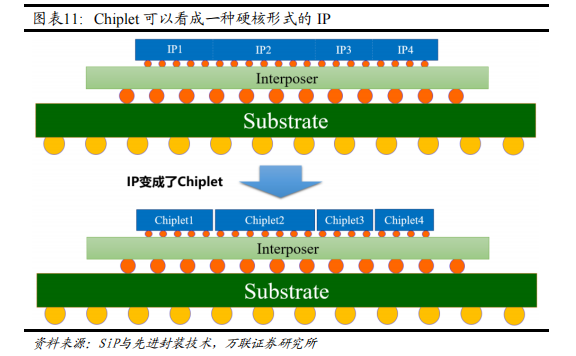

Chiplet通过先进封装工艺实现。Chiplet也称为小芯片或芯粒,该技术通过将多个芯片裸片(Die)通过内部互联技术集成在一个封装内,构成专用功能的异构芯片。通过采用2.5D、3D等高级封装技术,Chiplet可实现多芯片之间的高速互联,提高芯片系统的集成度,扩展其性能、功耗优化的空间。相对SoC系统级芯片的传统设计方法,Chiplet技术方案不需要购买IP或者自研生产,只需要购买已经实现好的小硅片进行封装集成,且IP可以复用。所以Chiplet可以看成是一种硬核形式的IP,但它是以芯片的形式提供的。

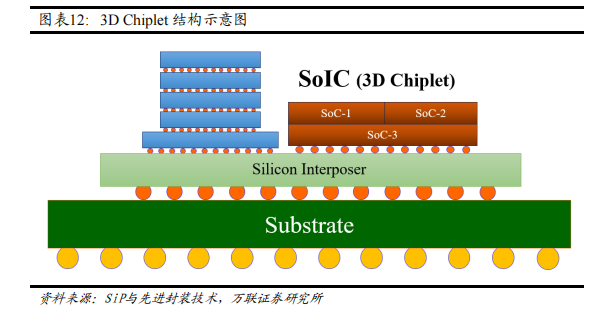

3D Chiplet是Chiplet进一步的发展。3D Chiplet是由AMD在2021年6月首先提出的,通过3D TSV将Chiplet集成在一起,同时为了提高互联密度,采用了no Bump的垂直互联结构。目前3D Chiplet产品是由台积电以SoIC的先进封装技术进行代工,主要应用在3D V-Cache上,将包含有64MB L3 Cache的Chiplet以3D堆叠的形式与处理器封装在一起。

-

pcb

+关注

关注

4319文章

23105浏览量

398074 -

封装技术

+关注

关注

12文章

549浏览量

67991 -

后摩尔时代

+关注

关注

0文章

12浏览量

9182 -

先进封装

+关注

关注

2文章

405浏览量

246

原文标题:先进封装:成后摩尔时代提升性能的主要技术

文章出处:【微信号:AI_Architect,微信公众号:智能计算芯世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

后摩尔定律时代,提升集成芯片系统化能力的有效途径有哪些?

根据“后摩尔时代”芯片行业如何发展?

IC在后摩尔时代的挑战和机遇

摩尔时代集成电路发展的三大支撑技术使得后摩尔定律得以继续

先进封装技术将推动后摩尔时代的半导体发展

重磅演讲:持续推进摩尔时代的IC设计艺术

聚焦后摩尔时代,后摩尔时代集成电路产业如何突破

普莱信智能孟晋辉出席CSPT 2022,共探后摩尔时代的封装技术

后摩尔时代,十大EDA验证技术趋势展望

UCIe为后摩尔时代带来什么?

先进封装:成后摩尔时代提升性能的主要技术

先进封装:成后摩尔时代提升性能的主要技术

评论