碳化硅 (SiC) 等宽带隙器件可实现能够保持高功率密度的晶体管,但需要使用低热阻封装,比如 TO-247。然而,此类封装的连接往往会导致较高的电感。阅读本博文,了解如何谨慎使用开尔文连接技术以解决电感问题。

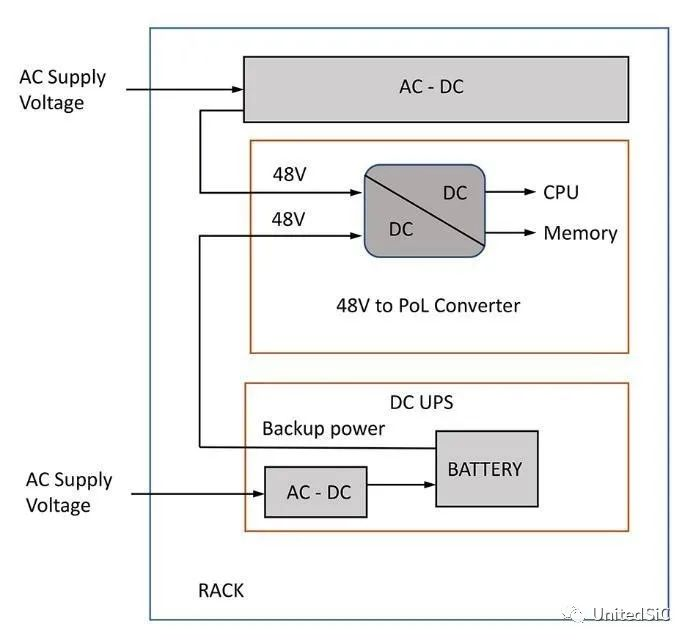

这篇博客文章最初由 United Silicon Carbide (UnitedSiC) 发布,该公司于 2021 年 11 月加入 Qorvo 大家庭。UnitedSiC 是一家领先的碳化硅 (SiC) 功率半导体制造商,它的加入促使 Qorvo 将业务扩展到电动汽车 (EV)、工业电源、电路保护、可再生能源和数据中心电源等快速增长的市场。

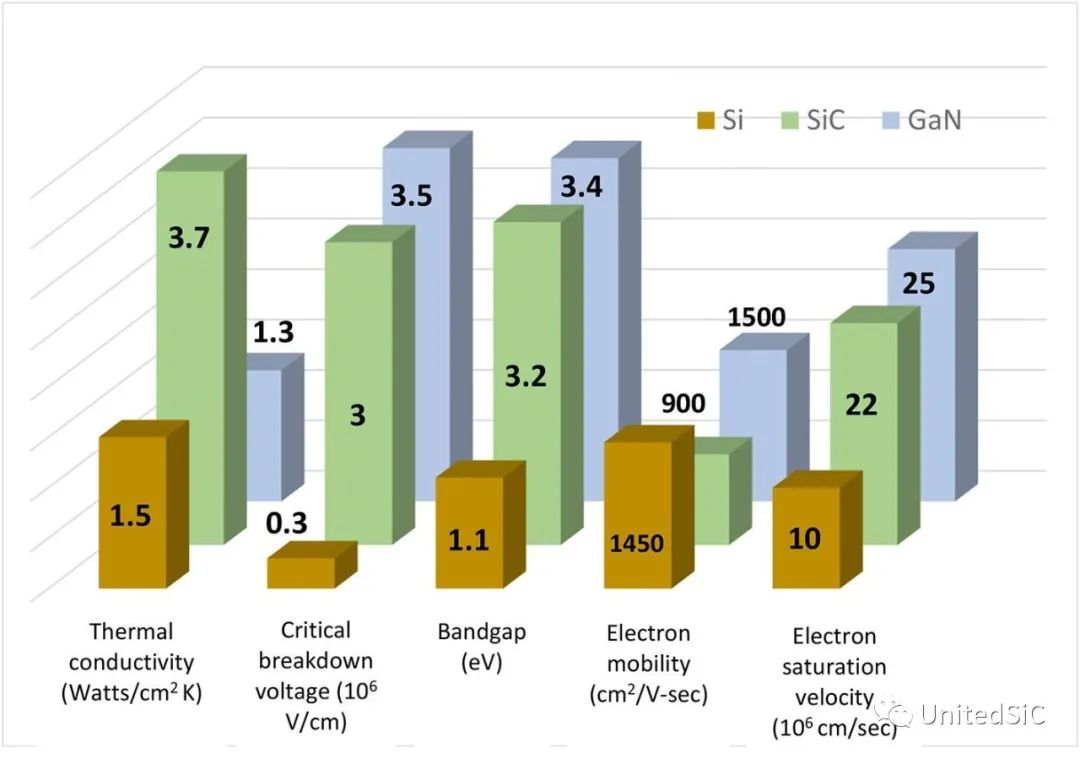

物理现象既会带来优势,也会产生弊端。采用碳化硅 (SiC) 等宽带隙材料构建而成的器件,可为设计人员提供能够保持高功率密度的晶体管,因为这些晶体管的传导损耗和开关损耗较低,而且工作结温高,开关速度快。高功率密度的晶体管对于实现更小的功率控制和转换电路有非常大的帮助,但仅仅改变半导体材料是无法实现的,还需要使用低热阻封装,比如 TO-247,以便轻松散热。不幸的是,这又是一个物理难题:TO-247 封装的连接往往电感较高,这会限制开关速度。

物理现象有利有弊,而在这种情况下,使用开尔文连接技术可以解决电感问题。但是我们必须谨慎实现此类连接,以避免发生更糟糕的物理现象。

开尔文连接

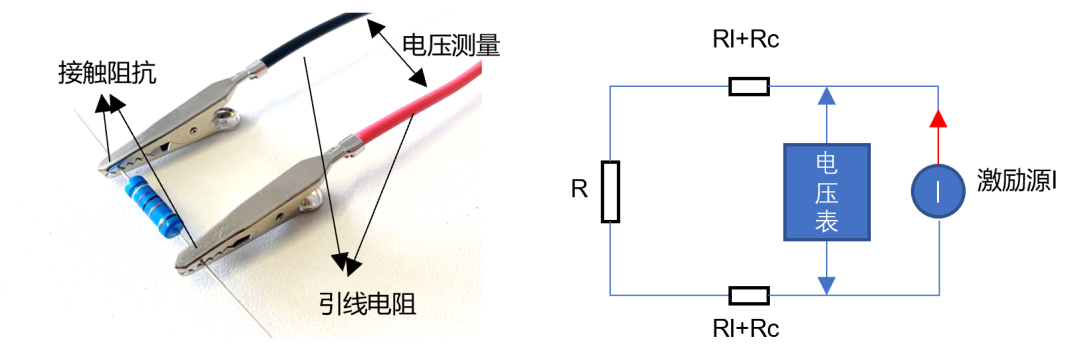

苏格兰/爱尔兰实验主义者开尔文男爵非常关注物理现象(如电流)的测量精度。他明白,要想通过检测给定电流下低电阻导致的压降,并结合使用欧姆定律来得出其阻值,就必须精确地测量电阻上的电压,并且要将测量电压的线路和载流路径分开。这种方法被称为开尔文连接。

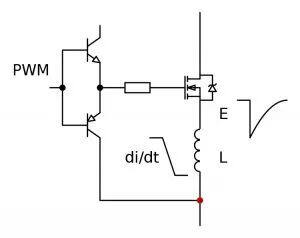

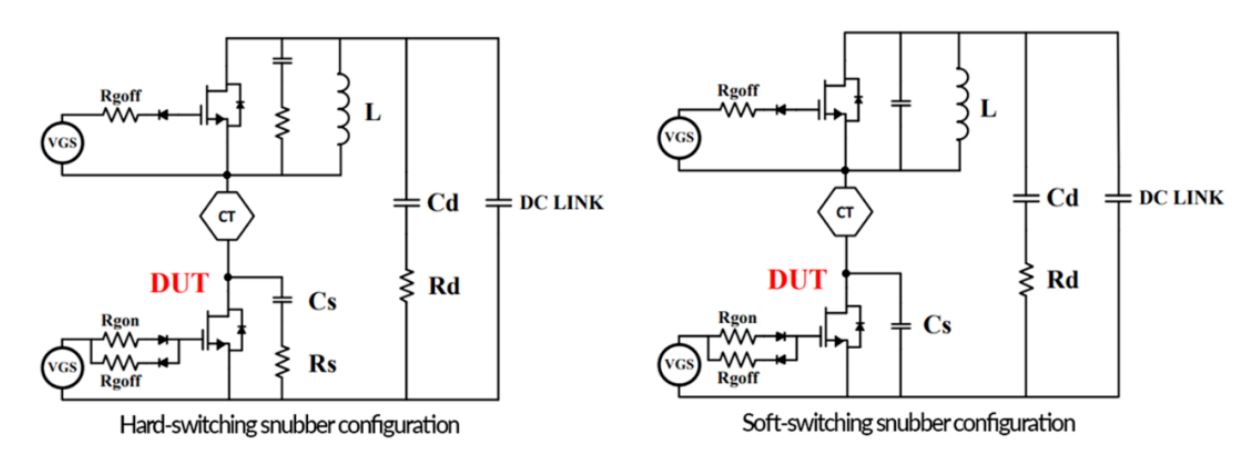

开尔文连接最初用于测量电路中适当位置的静态电压,但也可以用于在适当位置注入电压。例如:当以高频率驱动 MOSFET 开关的栅极时,器件的源连接就是栅极驱动电压与漏极-源极电流的共用点。如果存在共源电感 L(如图 1 中所示),则电流的变化就会影响栅极电压,且影响程度与电感 L 和电流变化率成正比。在栅极被驱动关断时,电感 L 两端产生的电压就会使栅极更长时间地保持接通状态,从而降低电流减小的速度。相反,在接通期间,电感 L 上的电压就会降低电流增加的速度。

控制引脚电感的影响

电感 L 来源于 MOSFET 的内部焊线,通常约为 1nH/mm。如果器件带有引脚(比如 TO-247 封装),则那些外部连接也会导致 L 增加。

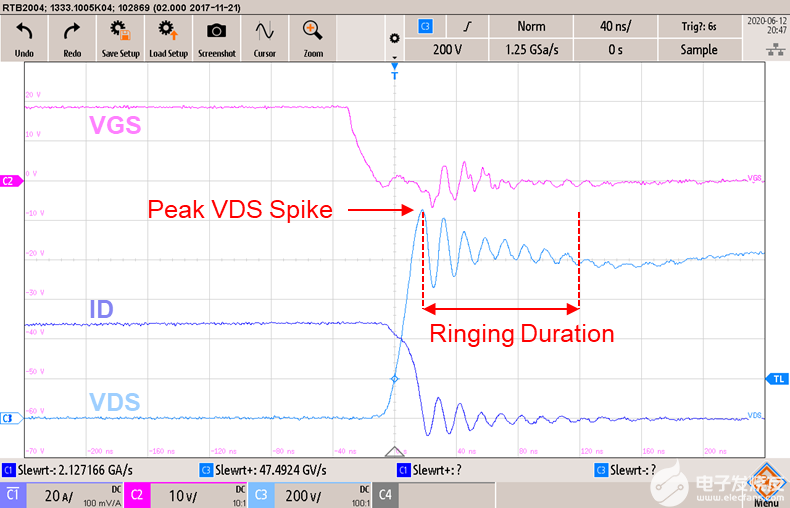

图 1:共源电感会产生瞬态栅极电压,从而降低开关电流速度

当以微秒为单位计算开关时间时,数安培的开关电流只会产生几毫伏的瞬态电压,从而使栅极驱动电压几乎保持不变。但是,宽带隙 (WBG) 器件可在数纳秒时间内产生数十安培的开关电流,这样每 nH 连接电感就会产生大约 2-5V 瞬态电压。如果栅极驱动中增加了这种瞬态电压,就会阻止 MOSFET 关断,从而产生振铃风险,甚至会导致器件故障。

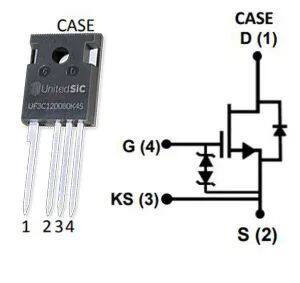

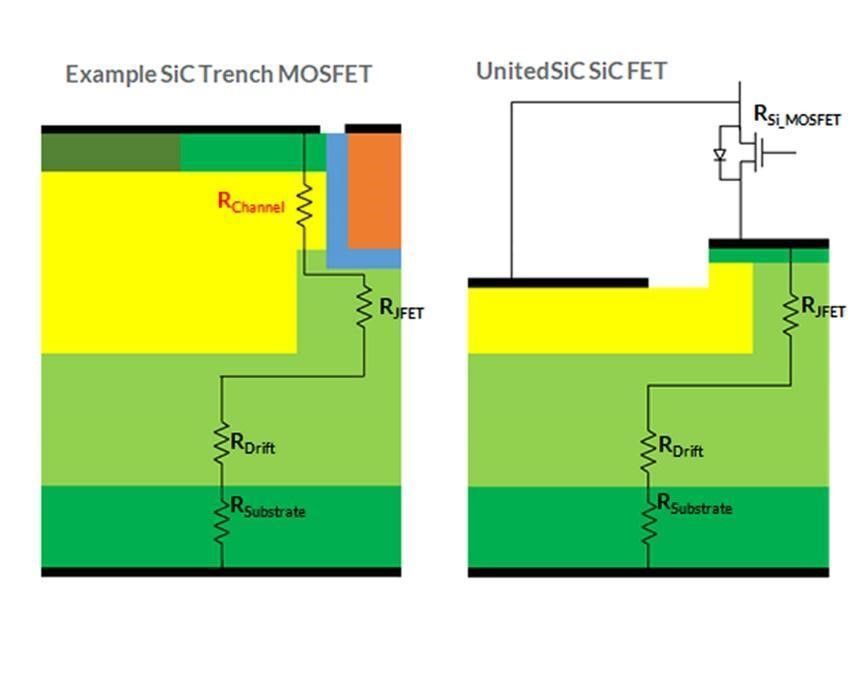

对于 Si MOSFET,可以在栅极关闭时施加加负电压(或许为 -10V)以克服栅极电压尖峰造成的偏压降低。但这会导致更高的栅极驱动功耗,该功耗会随总栅极驱动电压波动一同变化。这一问题对于采用 SiC 或氮化镓的 WBG 器件更为严重,因为此类器件只支持大约 -3V 的负驱动电压。解决方案就是使用开尔文连接,以确保栅极驱动回路尽可能靠近 MOSFET 晶粒的源连接。尽管使用芯片级封装比较容易实现这一点,但如果制造商想要使用 TO-247 封装以获得出色的散热特性,则必须增加第 4 个引脚,以便进行开尔文连接(图 2)。

图 2:TO-247 封装的第 4 个引脚可提供至源极的开尔文连接

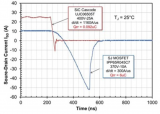

开关速度越快,效率越高

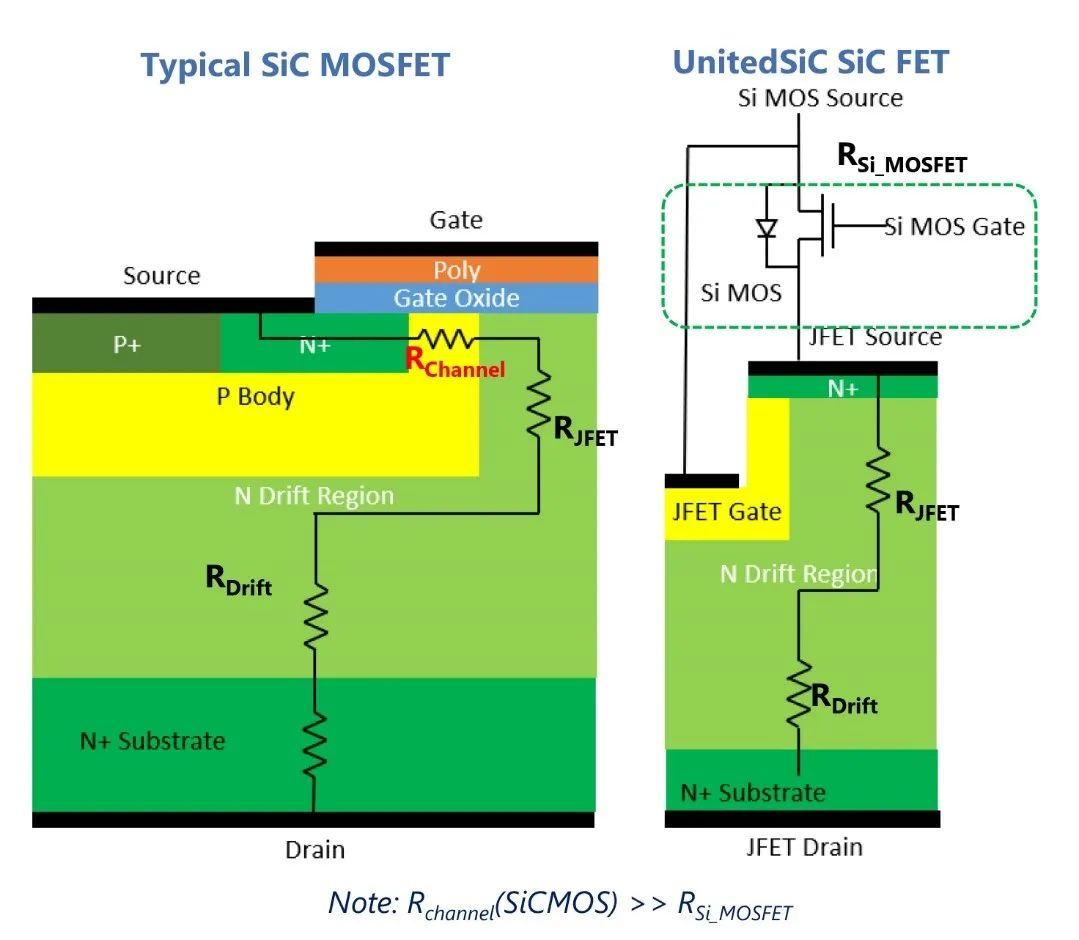

使用开尔文连接可控制引脚电感及其对栅极偏置电压的潜在影响,让宽带隙器件以其真实的开关速度运行,无需使用栅极负电压。这可以简化驱动电路。效果非常明显:当 UnitedSiC 的 SiC JFET 共源共栅使用三引脚封装时,必须降低器件的速度才能保持其可靠性。而使用四引脚封装以及开尔文连接时,电流压摆率可超过5000 A/µs,从而实现更高效率,且不会影响栅极驱动信号。

物理现象并非尽如人意,即使是采用 TO-247 封装,也有需要处理的器件引脚电感。常用的处理方式是跨漏极-源极放置一个小型缓冲电路,以防止功率路径中出现电压过冲。我们还必须小心部署栅极驱动回路,以尽可能地减少回路中的电感,同时防止出现由主换向回路导致的外部磁场拾取问题。

哪种开尔文连接?

使用开尔文连接时还会遇到其他实际问题。如果栅极驱动回路的电压为主系统 0V 电压,也就是与电源地线连接,则可能难以成为开尔文连接至开关的共用点。如果电路为全桥,那么至少会有两个低侧器件,如果都采用开尔文连接,则应将哪个连接至系统 0V?如果在器件源极引脚中使用电阻式电流感测,那么这个问题会变得更加复杂:如果开尔文连接的电压为系统 0V 电压,则电阻中的电压将为负电压。

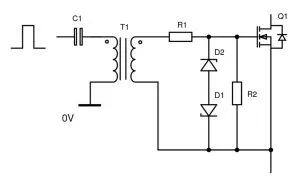

解决这个问题的一个方法就是,通过光耦合器或变压器来隔离栅极驱动,这也是任何高侧驱动都需使用的办法。如果此类隔离用于低侧,则可以灵活实现开尔文连接,与系统 0V 隔离(图 3)。此外,使用变压器意味着,设计人员可以根据需要生成关态栅极驱动负电压,并且可以通过调整匝比将驱动正电压调整至其最佳值。

图 3:隔离的变压器栅极驱动

优势大于劣势

使用开尔文接法连接带引脚的宽带隙器件还可使用 TO-247 封装,从而具有出色的散热性能。这使我们更接近于理想电气开关,并且实际上还可在较高功率水平下使用。

-

开关

+关注

关注

19文章

3139浏览量

93747 -

FET

+关注

关注

3文章

634浏览量

63014 -

SiC

+关注

关注

29文章

2841浏览量

62741 -

碳化硅

+关注

关注

25文章

2784浏览量

49121

发布评论请先 登录

相关推荐

采用SiC-FET的PSR反激参考设计

SiC FET性能和优势及起源和发展介绍

SiC FET的起源和发展

SiC FET导通电阻随温度变化

最大限度降低SiC FET的EMI的开关损耗

使用开尔文连接提高 SiC FET 的开关效率

给SiC FET设计PCB有哪些注意事项?

使用开尔文连接提高SiC FET的开关效率

使用开尔文连接提高SiC FET的开关效率

评论