绪论

该项目的目标是展示 HLS 在设计数字系统方面的能力。为此,本文展示如何在 HLS 中描述数字时钟。

时钟在 7 段数码管上显示小时、分钟和秒。

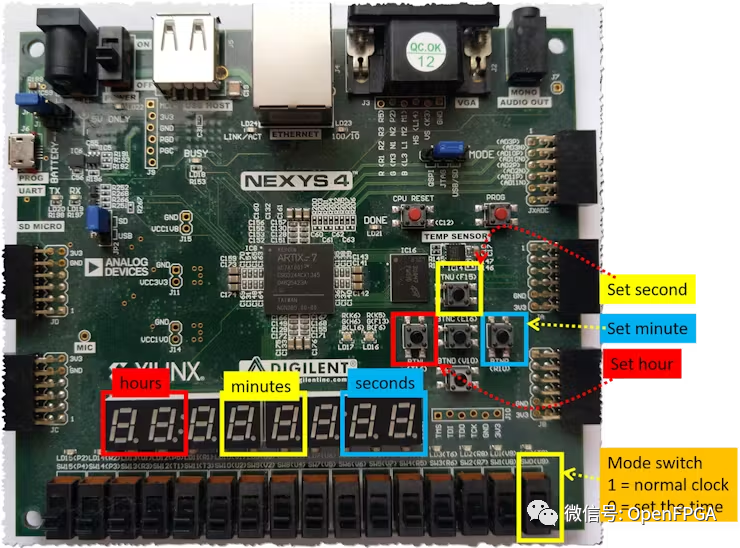

它有两种操作模式:时钟和设置。时钟模式是标准模式,在此模式下,当前时间显示在数码管上。在设置模式下,可以使用按钮设置时间。

下图显示开发板上的时钟配置。

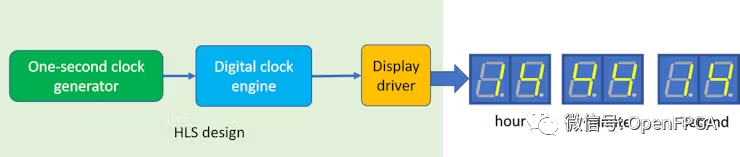

如下图所示,该设计主要分为三个模块:秒时钟发生器、数字时钟引擎和显示驱动。

下面的流水线循环用于实现秒时钟发生器。

booldelay(longlongintn){

#pragmaHLSINLINEoff

staticbooldummy=0;

for(longlongintj=0;j< n; j++) {

#pragma HLS pipeline

dummy = !dummy;

}

return dummy;

}

void one_second_clock_generator(bool &second) {

#pragma HLS INTERFACE ap_none port=second

#pragma HLS INTERFACE ap_ctrl_none port=return

static bool s = 0;

s=!s;

second = s;

delay(50000000L);

}

数字时钟引擎主要是跟踪小时、分钟和秒,并在收到来自秒时钟发生器模块的时钟节拍时更新它们。以下代码完成上诉功能。

voiddebounce(boolpulse,bool&out){

#pragmaHLSINLINEoff

staticboolout0=0;

staticboolout1=0;

staticboolout2=0;

staticboolstate=0;

if(state==0){

out2=out1;

out1=out0;

out0=pulse;

state=1;

}else{

delay(2500000);

state=0;

}

out=out0&out1&out2;

}

voidset_time(

ap_uint<6>&seconds,

ap_uint<6>&minutes,

ap_uint<5>&hours,

boolset_second,

boolset_minute,

boolset_hour)

{

//--------------------------------------------------

staticboolsecond_state=0;

if(second_state==0&&set_second==1){

seconds++;

if(seconds==60){

seconds=0;

}

second_state=1;

}

if(second_state==1&&set_second==0){

second_state=0;

}

//---------------------------------------------------

staticboolminute_state=0;

if(minute_state==0&&set_minute==1){

minutes++;

if(minutes==60){

minutes=0;

}

minute_state=1;

}

if(minute_state==1&&set_minute==0){

minute_state=0;

}

//----------------------------------------------------

staticboolhour_state=0;

if(hour_state==0&&set_hour==1){

hours++;

if(hours==24){

hours=0;

}

hour_state=1;

}

if(hour_state==1&&set_hour==0){

hour_state=0;

}

//----------------------------------------------------

}

voidclock_ticking(

ap_uint<5>&hours,

ap_uint<6>&minutes,

ap_uint<6>&seconds)

{

seconds++;

if(seconds==60){

seconds=0;

minutes++;

if(minutes==60){

minutes=0;

hours++;

if(hours==24)

hours=0;

}

}

}

voiddigital_clock(

boolset_time_sw,

bool&set_time_led,

boolset_second,

boolset_minute,

boolset_hour,

boolone_second_delay,

ap_uint<6>&seconds_out,

ap_uint<6>&minutes_out,

ap_uint<5>&hours_out

)

{

#pragmaHLSINTERFACEap_noneport=set_time_sw

#pragmaHLSINTERFACEap_noneport=set_time_led

#pragmaHLSINTERFACEap_noneport=set_minute

#pragmaHLSINTERFACEap_noneport=set_hour

#pragmaHLSINTERFACEap_noneport=seconds_out

#pragmaHLSINTERFACEap_noneport=minutes_out

#pragmaHLSINTERFACEap_noneport=hours_out

#pragmaHLSINTERFACEap_ctrl_noneport=return

staticap_uint<6>seconds=0;

staticap_uint<6>minutes=0;

staticap_uint<5>hours=0;

ap_uint<8>segment_data;

ap_uint<8>segment_enable;

staticboolstate_clock=0;

boolone_second=one_second_delay;

boolset_time_flag=set_time_sw;

if(one_second==1&&set_time_flag==0&&state_clock==0){

clock_ticking(hours,minutes,seconds);

state_clock=1;

}

if(one_second==0&&set_time_flag==0&&state_clock==1){

state_clock=0;

}

if(set_time_flag==1){

boolset_minute_debounce;

boolset_hour_debounce;

boolset_second_debounce;

debounce(set_minute,set_minute_debounce);

debounce(set_hour,set_hour_debounce);

debounce(set_second,set_second_debounce);

set_time(seconds,minutes,hours,set_second_debounce,set_minute_debounce,set_hour_debounce);

}

seconds_out=seconds;

minutes_out=minutes;

hours_out=hours;

set_time_led=set_time_sw;

}

最后一个 HLS 代码在 7 段数码管上显示当前时间。

#includeconstap_uint<8>seven_segment_code[10]={ 0b11000000, 0b11111001, 0b10100100, 0b10110000, 0b10011001, 0b10010010, 0b10000010, 0b11111000, 0b10000000, 0b10010000 }; booldelay(longlongintn){ #pragmaHLSINLINEoff staticbooldummy=0; for(longlongintj=0;j< n; j++) { #pragma HLS pipeline dummy = !dummy; } return dummy; } void seven_segment_display( ap_uint<5>hours, ap_uint<6>minutes, ap_uint<6>seconds, ap_uint<8>&seven_segment_data, ap_uint<8>&seven_segment_enable) { #pragmaHLSINTERFACEap_noneport=hours #pragmaHLSINTERFACEap_noneport=minutes #pragmaHLSINTERFACEap_noneport=seconds #pragmaHLSINTERFACEap_noneport=seven_segment_data #pragmaHLSINTERFACEap_noneport=seven_segment_enable #pragmaHLSINTERFACEap_ctrl_noneport=return ap_uint<4>second_digit_1=seconds%10; ap_uint<4>second_digit_2=seconds/10; ap_uint<4>minute_digit_1=minutes%10; ap_uint<4>minute_digit_2=minutes/10; ap_uint<4>hours_digit_1=hours%10; ap_uint<4>hours_digit_2=hours/10; ap_uint<8>segment_data; ap_uint<8>segment_enable; staticap_uint<3>state=0; switch(state){ //second case0: segment_data=seven_segment_code[second_digit_1]; segment_enable=0b11111110; delay(250000L); state=1; break; case1: segment_data=seven_segment_code[second_digit_2]; segment_enable=0b11111101; state=2; delay(250000L); break; //minutes case2: segment_data=seven_segment_code[minute_digit_1]; segment_enable=0b11110111; state=3; delay(250000L); break; case3: segment_data=seven_segment_code[minute_digit_2]; segment_enable=0b11101111; state=4; delay(250000L); break; //hours case4: segment_data=seven_segment_code[hours_digit_1]; segment_enable=0b10111111; state=5; delay(250000L); break; case5: segment_data=seven_segment_code[hours_digit_2]; segment_enable=0b01111111; state=0; delay(250000L); break; default: segment_data=seven_segment_code[0]; segment_enable=0b11111111; state=0; delay(250000L); break; } seven_segment_data=segment_data; seven_segment_enable=segment_enable; }

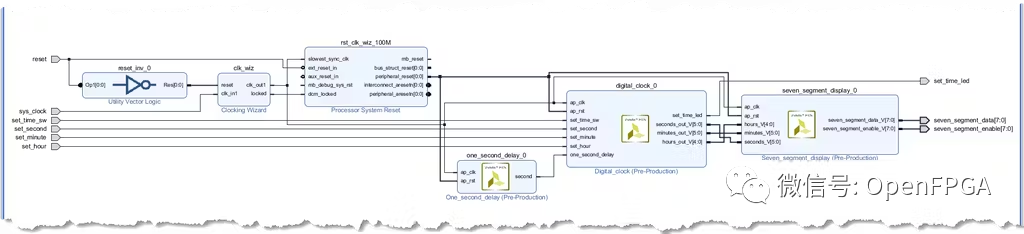

综合这些代码后,使用 Vivado 工具将它们连接在一起并生成 FPGA 比特流。

对电路板编程后,可以看到下图:

审核编辑:刘清

-

FPGA

+关注

关注

1640文章

21897浏览量

611327 -

数码管

+关注

关注

32文章

1888浏览量

92012 -

时钟发生器

+关注

关注

1文章

219浏览量

68601 -

数字时钟

+关注

关注

2文章

153浏览量

20675 -

HLS

+关注

关注

1文章

131浏览量

24535

原文标题:HLS 设计数字时钟

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何在HLS 14.3中编写pow功能?

合成中的Vivado HLS中的Pragma错误怎么解决

【正点原子FPGA连载】第一章HLS简介-领航者ZYNQ之HLS 开发指南

数字时钟设计功能描述

FPGA高层次综合HLS之Vitis HLS知识库简析

使用Vitis HLS创建属于自己的IP相关资料分享

Vivado环境下如何在IP Integrator中正确使用HLS IP

HLS系列–High Level Synthesis(HLS)的端口综合2

FPGA设计中的HLS 工具应用

关于Vivado HLS错误理解

HLS协议实现

如何在Vitis HLS GUI中使用库函数?

如何在HLS中描述数字时钟?

如何在HLS中描述数字时钟?

评论