Checks和coverage是覆盖率驱动的验证流程的关键。在验证环境中,Checks和coverage可以被定义在多个位置。

在Classes中实现Checks和Coverage

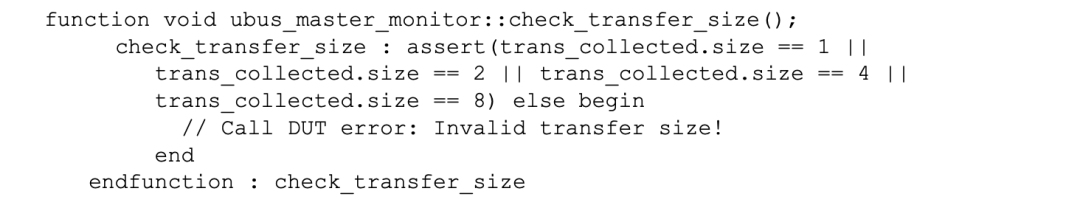

uvm_monitor的派生类总是存在于agent中,因此包含必要的Checks和Coverage。下面是一个断言检查的简单例子,传输的size字段是1、2、4或8。否则断言失败。

check也可以写成函数的形式,例如检查size字段的值与动态数组的size相匹配。

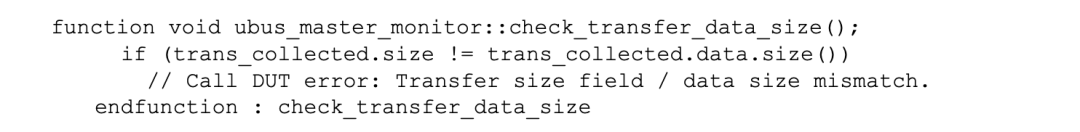

这两个检查都应该在transfer被monitor收集时执行。由于这些check是在同一时间发生的,所以可以封装成一个函数,这样就只需要进行一次调用。

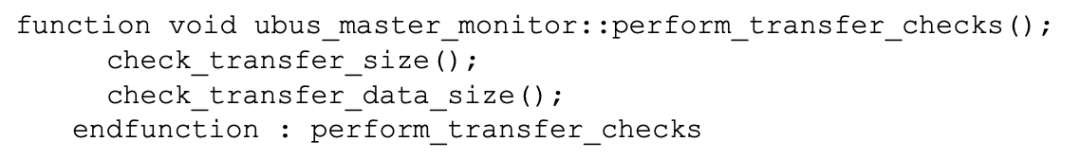

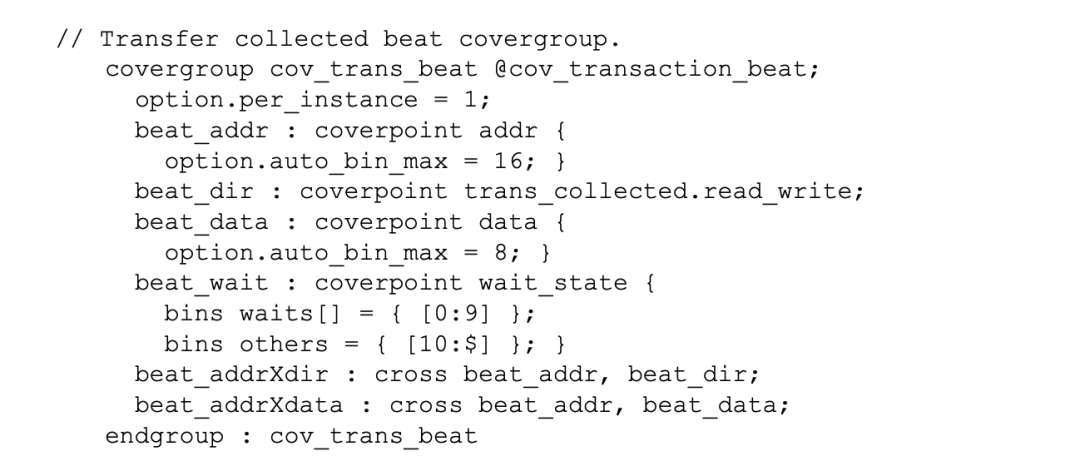

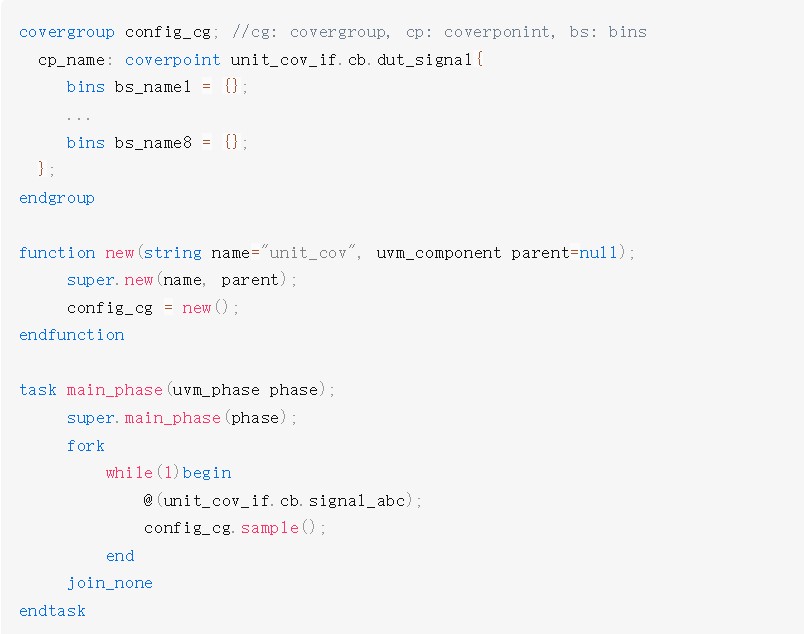

功能覆盖是通过SystemVerilog covergroups实现的,下面是一个简单的covergroups的例子。

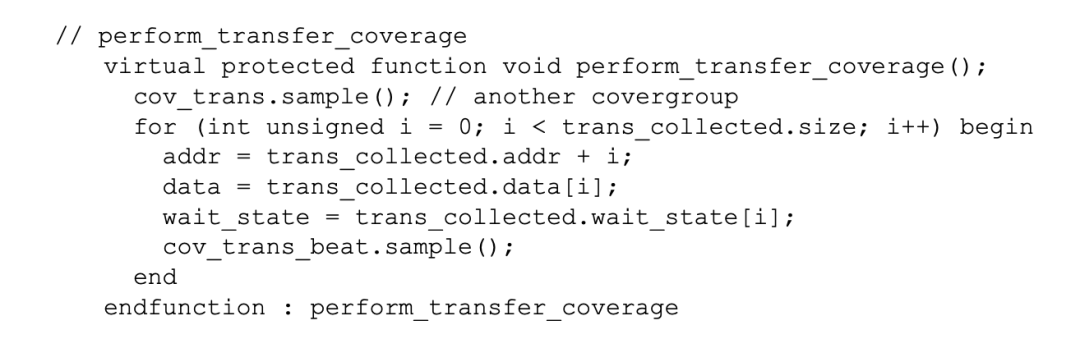

这个covergroup被定义在一个从uvm_monitor派生出来的类里面。对于上述covergroup,应该在一个函数中声明作为coverpoints的局部变量,然后对covergroup进行采样。

SystemVerilog没有提供动态数组覆盖率收集的能力,这个函数实现了这个功能。perform_transfer_coverage()函数会像 perform_transfer_checks()一样,在transaction被monitor收集时调用。

在Interfaces中实现Checks和Coverage

InterfacesChecks被实现为assertions,以检查信号协议为主。例如,一个断言可能会检查一个地址在有效的传输过程中从未出现过X。

在Formal FPV中,

当property表达DUT的内部和输出行为时,使用assert进行检查。

当property表达产生DUT激励的环境行为时,就使用assume约束。

控制Checks和Coverage

应该提供一个字段来控制Checks是否被执行和Coverage是否被收集,该字段可以通过uvm_config_db接口来控制。下面是一个使用checks_enable位来控制Checks的例子。

if (checks_enable) perform_transfer_checks();

uvm_config_db#(int)::set(this,"masters[0].monitor", "checks_enable", 0);

审核编辑:刘清

-

Verilog

+关注

关注

31文章

1374浏览量

114787 -

UVM

+关注

关注

0文章

183浏览量

20115 -

DUT

+关注

关注

0文章

194浏览量

13505

原文标题:在验证环境中开发Checks和Coverage

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

在STM32F334上使用IAR开发环境和jlink的SWD接口调试,怎么设置才可以使用IAR的code coverage功能?

在Linux ubuntu上使用riscv-formal工具验证蜂鸟E203 SoC的正确性

【大联大世平Intel®神经计算棒NCS2试用体验】2.搭建OpenVino开发环境下——测试验证开发环境

ST-Link调试开发环境介绍设置步骤

重点厘清覆盖率相关的概念以及在芯片开发流程中跟覆盖率相关的事项

SpinalHDL开发环境搭建步骤相关资料分享

聊聊芯片IC验证中的风险

SystemVerilog实用知识点:覆盖率之Function Coverage

可重用的验证组件中构建测试平台的步骤

在验证环境中开发Checks和Coverage的步骤

在验证环境中开发Checks和Coverage的步骤

评论